3149

Изобретение относится к области вычислительной техники и может быть использовано в качестве базового узла больших интегральных схем, выпол- няемых по технологии.

Цель изобретения - расширение области применения за счет представления результата по модулю, значение которого меньше значения максимально возможной суммы входных сигналов.

На чертеже приведена функциональная схема реализации сумматора с и модулем q представления результата равного семи.

Сумматор содержит входы 1, объединенные по схеме токового суммирования, первый и второй токовые отражатели 2 и 3 с весами инжекторов,равными 3 q, первый пороговьй детектор 4 с весом инжектора, равным 2 q + К, третий токовый отражатель 5 с весом инжектора, равным q, второй пороговый детектор 6 с весом инжектора,равным q - 0,5, четвертый и пятый токо- вые отражатели 7 и 8 с весами инжекторов, равными q, третий пороговый Детектор 9 с весом инжектора, равным 2 q - 0,5, шестой и седьмой токовые отражатели 10 и 11 с весами инжекторов, равньп 1И q, четвертый пороговый детектор 12 с весом инжектора, равным 3 q, пятый пороговый детектор 13/ с весом инжектора, равным 3 q, контрольные точки 14 - 40, К-янач- ный выход 41 суммы и К-знач- ный выход 42 переноса, соединенные между собой функционально.

Пороговые детекторы и токовые отражатели выполнены на п-р-п-транзис- торах с инжекционным питанием в цепь базы. Эмиттеры всех транзисторов соединены с шиной нулевого потенциала.

Сумматор для и q 7 работает следующим образом.

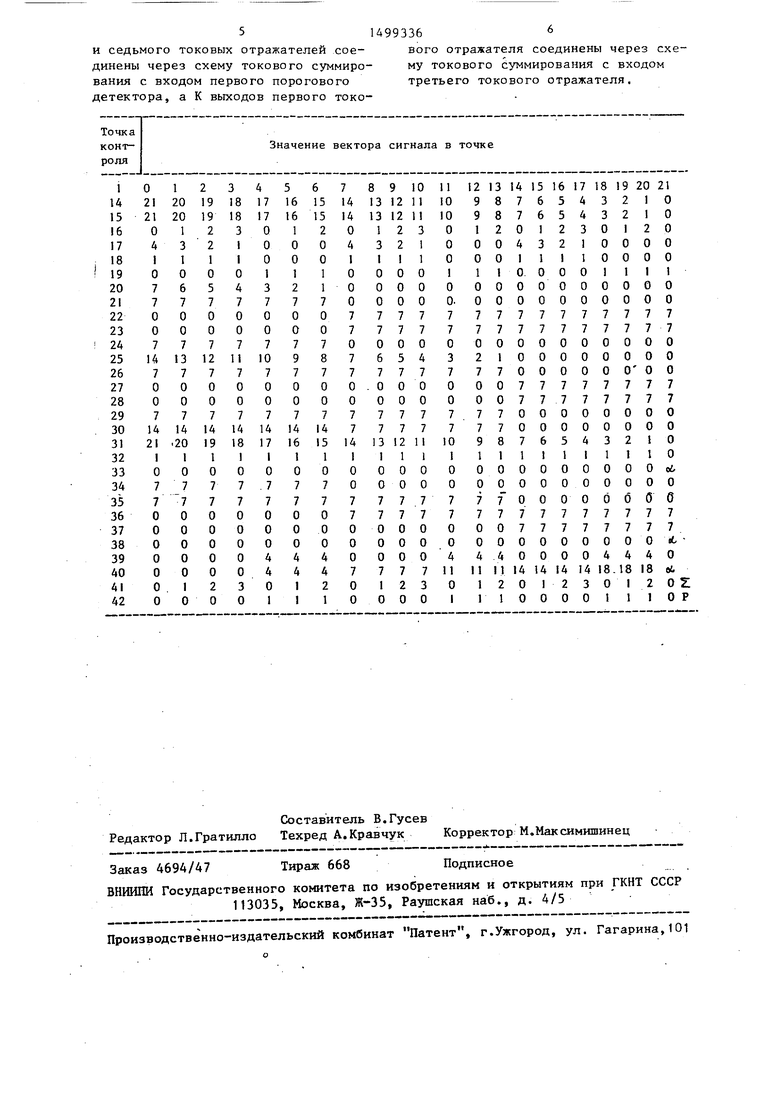

На входах 1 аргументы принимают все возможные значения из множества Е ,l ,2,3} и, следовательно, после токового суммирования могут образовывать вектор С О 123456789 10 11 12 13 14 15 16 17 18 19 20 21 Тогда работа сумматора может быть представлена с помощью таблицы.

Формула из.обретения 55

Од норазрядный К-значный сумматор, содержащий три токовых отражателя и первый пороговый детектор, причем

45

вход первого порогового детектора соединен с первой группой входов сумматора, объединенных по схеме токового суммирования, выход первого порогового детектора соединен с входом первого токового отражателя, выход которого соединен с выходом переноса сумматора, вход второго токового отражателя соединен с второй группой входов сумматора, объединенных по схеме токового суммирования, выход второго токового отражателя соединен с входом третьего токового отражателя, выход которого соединен с выходом суммы сумматора, отличающийся

0 5 5

0

0

0

5

Тем, что, с целью расширения области применения за счет представления результата по модулю, значение которого меньше значения максимально возможной суммы входных сигналов, в не- го введены второй, третий, четвертый и пятый пороговые детекторы и четвертый, пятый, шестой и седьмой токовые отражатели, причем вход второго порогового детектора соединен с третьей группой входов сумматора, объединенных по схемв токового суммирования, выход второго порогового детектора соединен с входом четвертого токового отражателя,первый выход которого соединен с входом пятого токового, отражателя , а второй выход четвертого токового отражателя - с К выходами первого токового отражателя (где К - значность функционирования схемы), вход третьего порогового детектора соединен с четвертой группой входов сумматора, объединенных по схеме токового суммирования, выход третьего порогового детектора соединен с входом шестого токового отражателя, первьтй выход которого соединен с входом седьмого токового 5 отражателя, а второй выход шестого такового отражателя соединен с К выходами первого токового отражателя, вход четвертого порогового детектора соединен с пятой группой входов сумматора, объединенных по схеме токового суммирования,вькод четвертого порогового детектора соединен с входом-пятого порогового детектора, первый вьсход которого соединен с К выходами первого токового отражателя, второй выход пятого порогового детектора соединен через схему токового -суммирования с входом первого токового отражателя, выходы пятого

и седьмого токовых отражателей соединены через схему токового суммирования с входом первого порогового детектора, а К выходов первого токового отражателя соединены через схему токового суммирования с входом третьего токового отражателя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный К-значный сумматор | 1985 |

|

SU1312566A1 |

| Четырехуровневый однозарядный сумматор | 1984 |

|

SU1236463A1 |

| Четырехуровневый одноразрядный сумматор | 1987 |

|

SU1501042A1 |

| Логическое устройство | 1983 |

|

SU1102041A1 |

| Инжекционный сумматор | 1988 |

|

SU1539992A1 |

| Четырехзначный умножитель элементов поля Галуа GF(2 @ ) | 1990 |

|

SU1737443A1 |

| Одноразрядный сумматор на инжекционных элементах | 1985 |

|

SU1275430A1 |

| Четырехзначный умножитель | 1986 |

|

SU1352481A1 |

| Умножитель четверичный инжекционного типа | 1980 |

|

SU928651A1 |

| СПОСОБ ПОЛНОГО СЛОЖЕНИЯ - ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1998 |

|

RU2132566C1 |

Изобретение относится к области вычислительной техники и может быть использовано в качестве базового узла больших интегральных схем, выполняемых на И2Л технологии. Целью изобретения является расширение области применения сумматора за счет представления результата по модулю, значение которого меньше значения максимально возможной суммы входных сигналов. Одноразрядный K-значный сумматор содержит входы 1, объединенные по схеме токового суммирования, первый 2 и второй 3 токовые отражатели, первый пороговый детектор 4, третий токовый отражатель 5, второй пороговый детектор 6, четвертый 7 и пятый 8 токовые отражатели, третий пороговый детектор 9, шестой 10 и седьмой 11 токовые отражатели, четвертый 12 и пятый 13 пороговые детекторы, контрольные точки 14...40, выход 41 суммы и выход 42 переноса, соединенные между собой функционально. 1 ил., 1 табл.

| Одноразрядный сумматор на инжекционных элементах | 1985 |

|

SU1275430A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Одноразрядный К-значный сумматор | 1985 |

|

SU1312566A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-07—Публикация

1987-12-14—Подача