(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приоритета | 1990 |

|

SU1829033A1 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

| Многопроцессорная вычислительная система | 1985 |

|

SU1277129A1 |

| Устройство для управления динамической памятью | 1987 |

|

SU1524089A1 |

| Программируемое устройство для контроля цифровых систем | 1986 |

|

SU1439588A1 |

| ЭВМ | 1990 |

|

RU2024928C1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Устройство логической обработки | 1982 |

|

SU1124317A1 |

| Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе | 1989 |

|

SU1633418A1 |

Изобретение относится к вычислительной технике, в частности к устройствам приоритета, и может быть применено при управлении очередностью- обращения нескольких микропроцессоров к общему ресурсу вычислительных систем. Цель изобретения - повышение быстродействия устройства. Устройство приоритетного доступа к общей шине содержит блок 5 переключения процессоров и блок 6 разрешения доступа к шине. Кроме того, многопроцессорная система, в которой используется предложенное устройство, содержит ПЗУ 1, ОЗУ 2, устройство 3 ввода-вывода и процессоры 7. Блок 5 включает программно-доступный регистр, два дешифратора, N+2 регистров (N - число процессоров), три схемы сравнения, два счетчика, N+2 элементов ИЛИ, а блок 6 - группу узлов доступа к устройству, каждый из которых содержит пять регистров, две схемы сравнения, элемент И, два одновиб- ) ратора и шинный формирователь. 3 ил.

Изобретение относится к вычислительной технике, в частности к устройствам приоритета и может быть применено при управлении очередностью обращения нескольких микропроцессоров к общему ресурсу вычислительной системы.

Известно устройство приоритета, содержащее входной и выходной регистры, первую и вторую группу элементов И, элемент ИЛИ, генератор тактовых импульсов, группу триггеров выходного регистра.

К недостаткам данного устройства приоритета относится низкое быстродействие устройства.

Наиболее близким к предлагаемому является устройство приоритета, содержащее n+З регистра (где п - количество процессо- ров)п+2 элемента ИЛИ, два дешифратора, схему сравнения, две схемы сравнения с нулем, два счетчика, элемент И.

Существенным недостатком приведенного устройства является то, что при обращении процессоров к устройствам общего ресурса не учитывается быстродействие устройств, которое превышает быстродействие микропроцессора (например ОЗУ, ПЗУ и т.д.). При этом возникают паузы в использовании устройств общего ресурса, связан- ные с невозможностью процессоров использовать их с максимальным быстродействием.

Цель изобретения- повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство приоритетного доступа к общей шине, содержащее блок переключения процессоров, содержащий программно-доступный регистр, первый и второй дешифраторы, п+2 регистров, первую, вторую и третью схемы сравнения, первый и второй

4

СО

счетчики, п+2 элемента ИЛИ, причем информационный вход блока переключения процессоров является информационным входом программно-доступного регистра, а первый и второй выходы последнего соеди- нены соответственно с входом первого дешифратора и информационными входами регистров с первого по n-й, входы записи которых соединены с соответствующими выходами первого дешифратора и с входа- ми (п+1)-го элемента ИЛИ, выход последнего соединен с входом чтения (п+1)-го регистра, информационные входы которого соединены с выходами второго дешифратора, а выходы - с входами чтения соответст- вующих регистров с первого по n-й и первыми входами элементов ИЛИ с первого по n-й, выходы регистров с перового по п-й поразрядно объединены и соединены с первыми входами первой и второй схем сравне- ния, второй- вход второй схемы сравнения соединен с выходом первого счетчика, счетный вход которого является синхровходом блока переключения процессоров, вход сброса которого соединен с первым выхо- дом второй схемы сравнения, с первым входом (п+2)-го элемента ИЛИ, и вторыми входами элементов ИЛИ с первого по п-й выход (п+1)-го элемента ИЛИ соединен с вторым входом (п+2)-го элемента ИЛИ и третьими входами элементов ИЛИ с первого по n-й, выход первой схемы сравнения и второй выход второй схемы сравнения объединены между собой и соединены с счетным входом второго счетчика, с входом сброса первого счетчика, а также с третьим входом (п+2)-го элемента ИЛИ и являются входом подтверждения состояния процессоров блока переключения процессоров, выход второго счетчика соединен с входом второго дешифратора и с первым входом третьей схемы сравнения, выход которой соединен с входом сброса второго счетчика, выход (п+2)-го элемента ИЛИ соединен с входом записи (п+2)-го регистра, информа- ционные входы которого соединены с выходами элементов ИЛИ с первого по п-й, выходы (п+2)-го регистра являются выходами блока переключения процессоров, вторые входы первой и второй схем сравнения соединены с шиной логического нуля устройства, в него введен блок разрешения доступа к шине, включающий m узлов доступа к устройству(где m К х L, К - количество типов машинных циклов, L - количество ус- тройств общего ресурса), каждый из которых содержит пять регистров, две схемы сравнения, элемент И, два одновибратора, шинный формирователь, причем в каждом узле доступа к устройству вход шины адреса

узла доступа к устройству является информационным входом шинного формирователя и первого регистра, выход которого соединен с первым входом первой схемы сравнения, второй вход которой соединен с выходом второго регистра, выход первой схемы сравнения соединен с первым входом элемента И, второй вход которого соединен с синхровходом блока доступа к устройству и с входом записи третьего регистра, выход которого соединен с первым входом второй схемы сравнения, второй вход которой соединен с выходом четвертого регистра, выход второй схемы сравнения соединен с третьим входом элемента И, выход которого соединен с входом чтения пятого одновибратора, выход которого соединен с входом первого одновибратора, выход которого соединен с входом чтения пятого регистра и со стробирующим входом шинного формирователя, а также с входом второго одновибратора, выход которого является выходом узла доступа к устройству, выход шинного формирователя выходом шины адреса узла доступа к устройству, информационный вход пятого регистра является входом шины данных узла доступа к устройству, вход записи пятого регистра является входом записи узла доступа к устройству, информационный вход третьего регистра является входом слова состояния узла доступа к устройству.

Такое решение позволяет повысить быстродействие за счет того, что доступ микропроцессоров к общей шине осуществлен с циклами обращения к шине, равными циклам обращения к устройствам (ПЗУ, ОЗУ и др.), путем настройки одновибраторов узла доступа к устройству. Таким образом максимально используется быстродействие (возможности) устройств общего ресурса.

Известно использование буферных регистров в устройствах приоритета для буферизации сигналов вычислительной системы.

В предлагаемом устройстве узел разрешения доступа к устройству обеспечивает доступ к системной шине в момент обращения к устройству с быстродействием авным быстродействию каждого устройства (ПЗУ, ОЗУ) вычислительной системы.

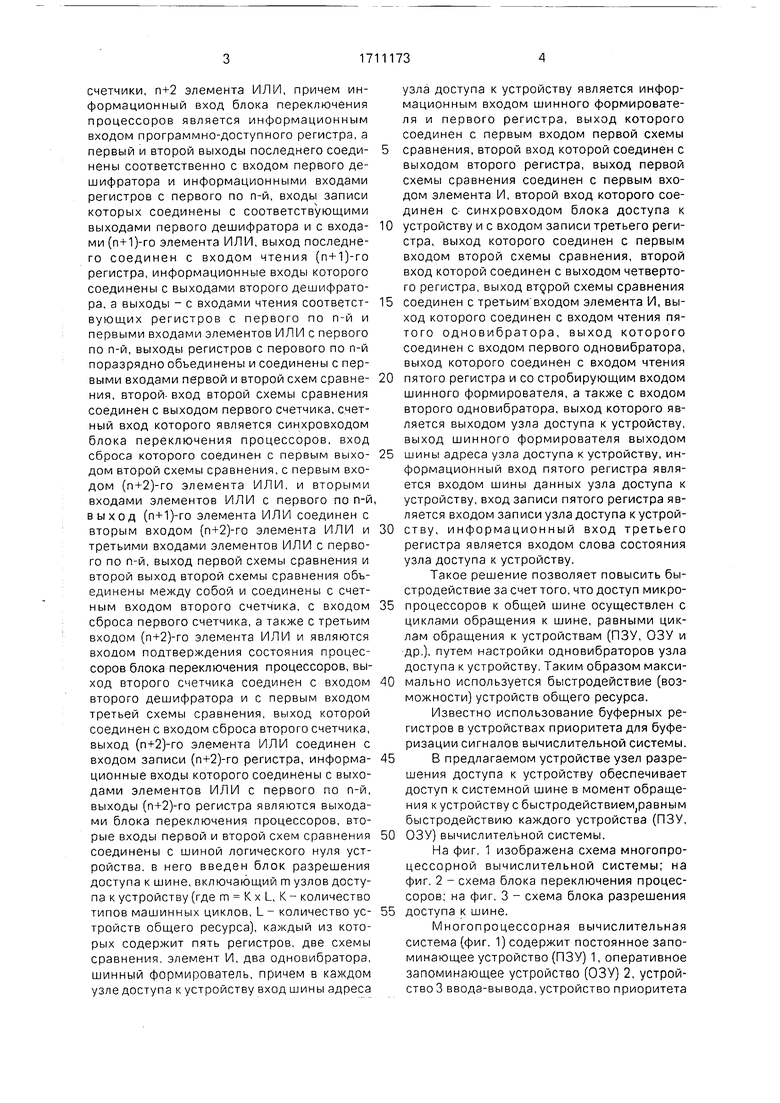

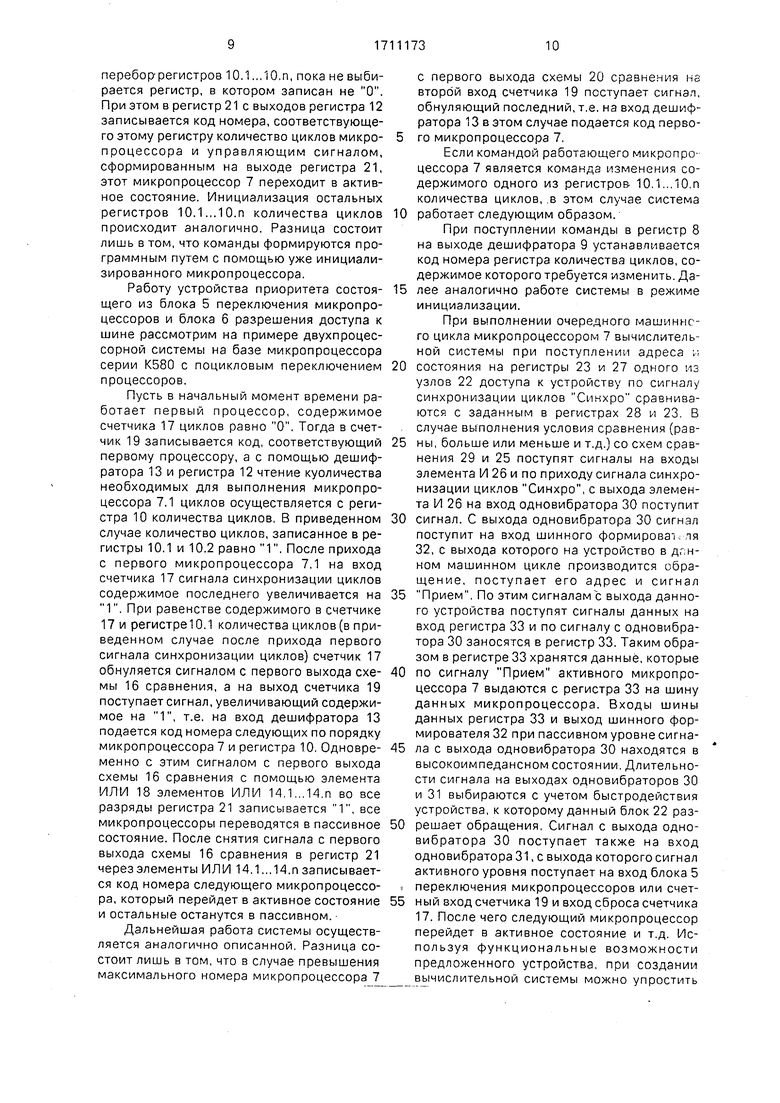

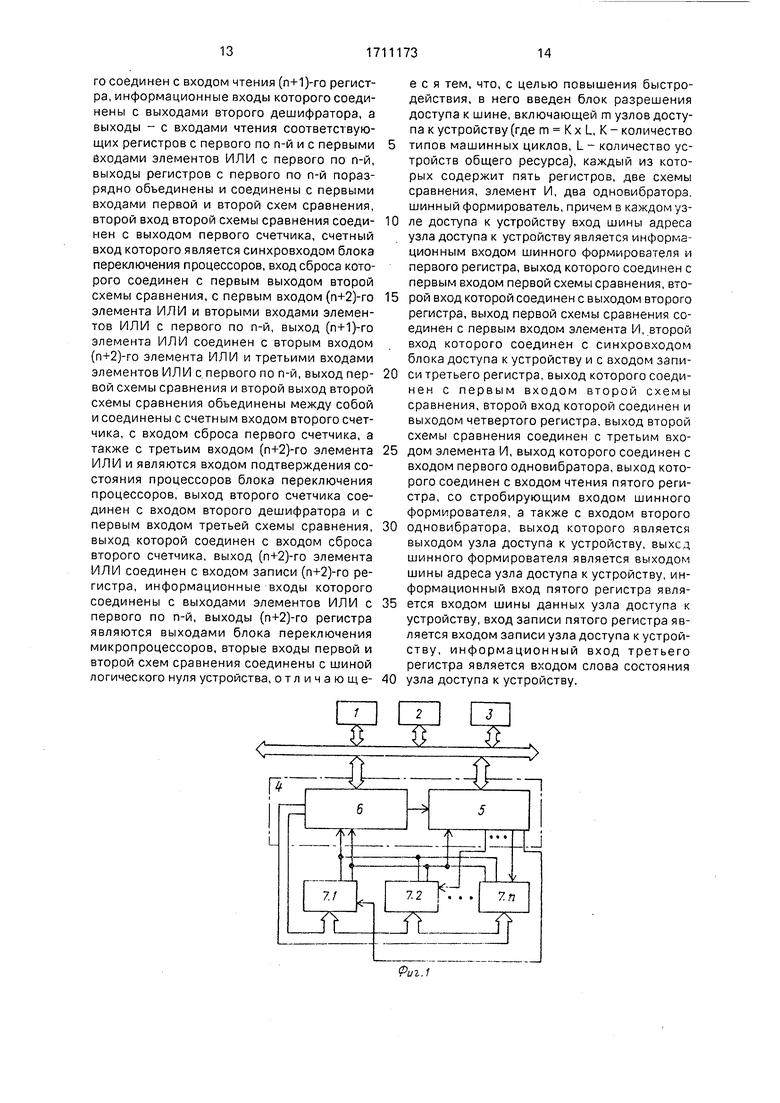

На фиг. 1 изображена схема многопроцессорной вычислительной системы; на фиг. 2 - схема блока переключения процессоров; на фиг. 3 - схема блока разрешения доступа к шине.

Многопроцессорная вычислительная система (фиг. 1) содержит постоянное запоминающее устройство (ПЗУ) 1 .оперативное запоминающее устройство (ОЗУ) 2, устройство 3 ввода-вывода, устройство приоритета

4, включающее блок 5 переключения процессоров и блок 6 разрешения доступа к шине, группу микропроцессоров 7.1...7.п.

Постоянное запоминающее устройство (ПЗУ) 1, оперативное запоминающее устройство (ОЗУ) 2, устройство 3 ввода-вывода через системную шину соединены с блоком 6 разрешения доступа к шине, а также с блоком 5 переключения процессоров. Шина каждого процессора 7.1...7.П соединена с входом шины блока 6 разрешения доступа к шине, выходы синхронизации микропроцессоров 7.1....7.п (Синхро) соединены с первым входом блока 6 разрешения доступа к шине, а также с вторым входом блока 5 переключения процессоров. Входы обращения к шине микропроцессоров 7.1...7.П (сигналы Прием) соединены с вторым входом блока, 6 разрешения доступа к шине. Вход управляющего сигнала каждого из микропроцессоров 7.1...7.П, переводящего их в пассивное состояние, соединены с соответствующими выходами блока 5 переключения процессоров. Выход блока 6 разрешения доступа к шине соединен с вторым входом блока 5 переключения процессоров.

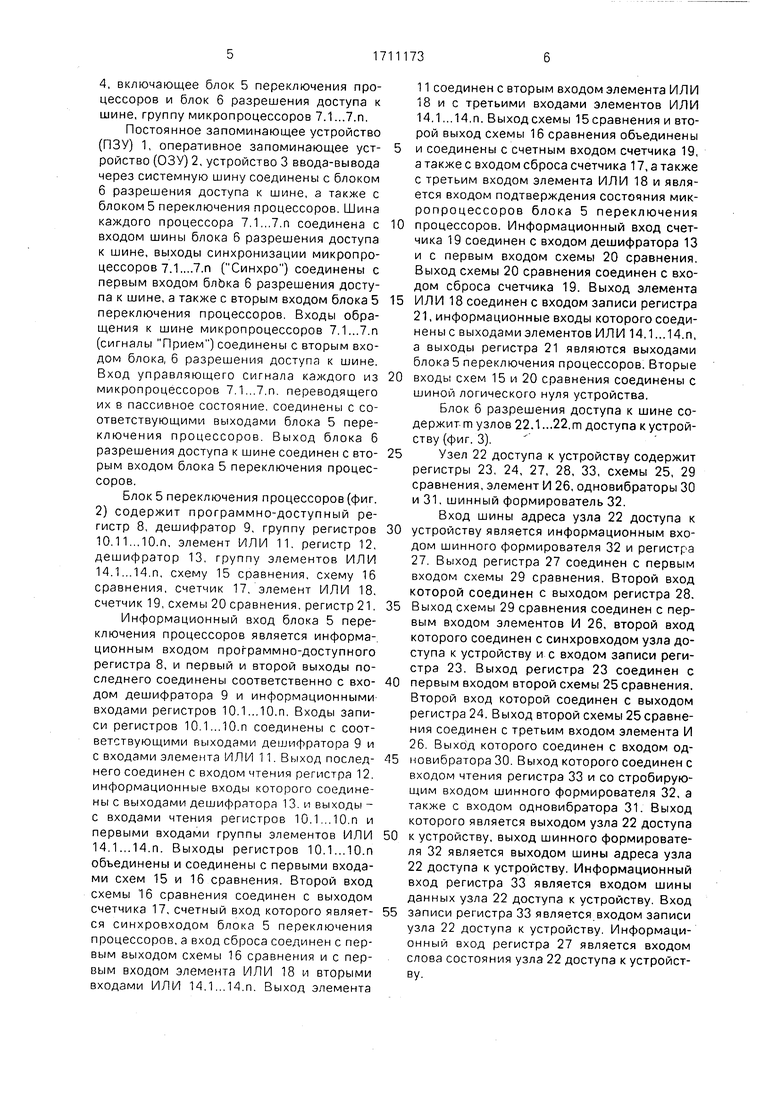

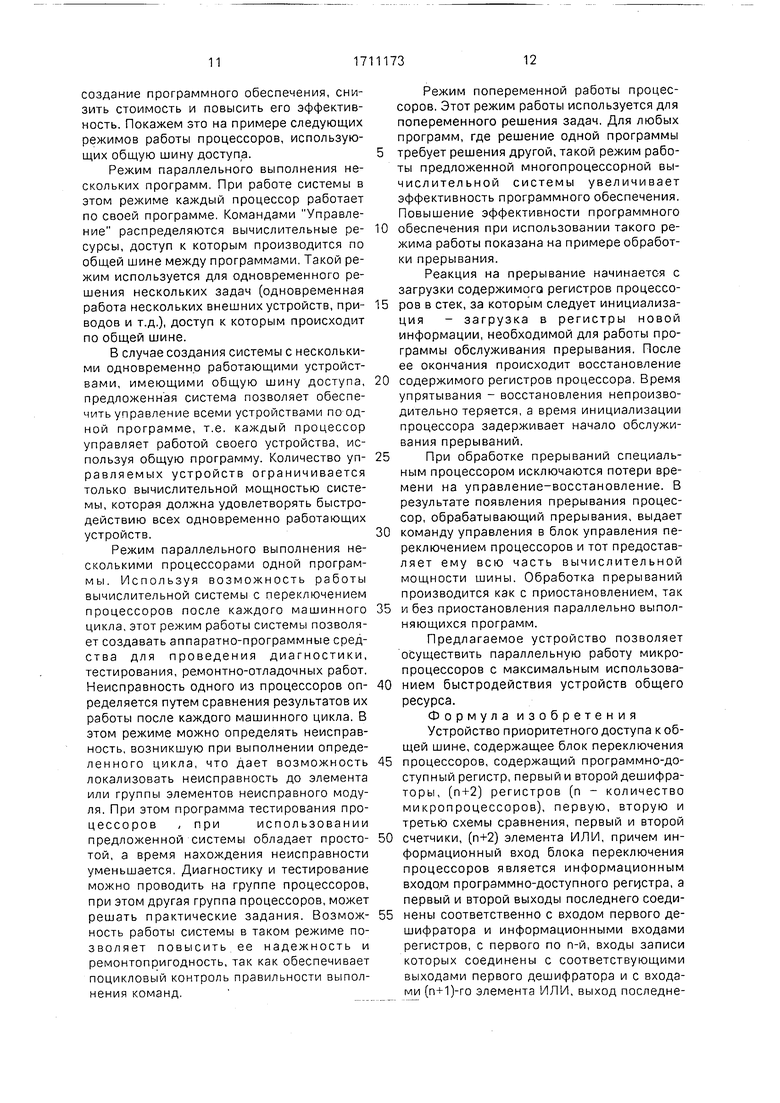

Блок 5 переключения процессоров (фиг. 2) содержит программно-доступный регистр 8, дешифратор 9, группу регистров 10.11...10.п, элемент ИЛИ 11, регистр 12, дешифратор 13, группу элементов ИЛИ 14.1...14.П, схему 15 сравнения, схему 16 сравнения, счетчик 17, элемент ИЛИ 18, счетчик 19, схемы 20 сравнения, регистр 21.

Информационный вход блока 5 переключения процессоров является информа-. ционным входом программно-доступного регистра 8, и первый и второй выходы последнего соединены соответственно с входом дешифратора 9 и информационными- входами регистров 10.1.„10.п. Входы записи регистров 10.1...10.П соединены с соответствующими выходами дешифратора 9 и с входами элемента ИЛИ 11. Выход последнего соединен с входом чтения регистра 12. информационные входы которого соединены с выходами дешифратора 13. и выходы - с входами чтения регистров 10.1...10.пи первыми входами группы элементов ИЛИ 14.1.„14.п. Выходы регистров 10.1...10.П объединены и соединены с первыми входами схем 15 и 16 сравнения. Второй вход схемы 16 сравнения соединен с выходом счетчика 17, счетный вход которого является синхровходом блока 5 переключения процессоров, а вход сброса соединен с первым выходом схемы 16 сравнения и с первым входом элемента ИЛИ 18 и вторыми входами ИЛИ 14.1...14.п. Выход элемента

11 соединен с вторым входом элемента ИЛИ 18 и с третьими входами элементов ИЛИ 14.1.„14.п. Выход схемы 15сравнения и второй выход схемы 16 сравнения объединены

и соединены с счетным входом счетчика 19, а также с входом сброса счетчика 17, а также с третьим входом элемента ИЛИ 18 и является входом подтверждения состояния микропроцессоров блока 5 переключения

процессоров. Информационный вход счетчика 19 соединен с входом дешифратора 13 и с первым входом схемы 20 сравнения. Выход схемы 20 сравнения соединен с входом сброса счетчика 19. Выход элемента

ИЛИ 18 соединен с входом записи регистра 21, информационные входы которого соединены с выходами элементов ИЛИ 14.1...14.П, а выходы регистра 21 являются выходами блока 5 переключения процессоров. Вторые

входы схем 15 и 20 сравнения соединены с шиной логического нуля устройства.

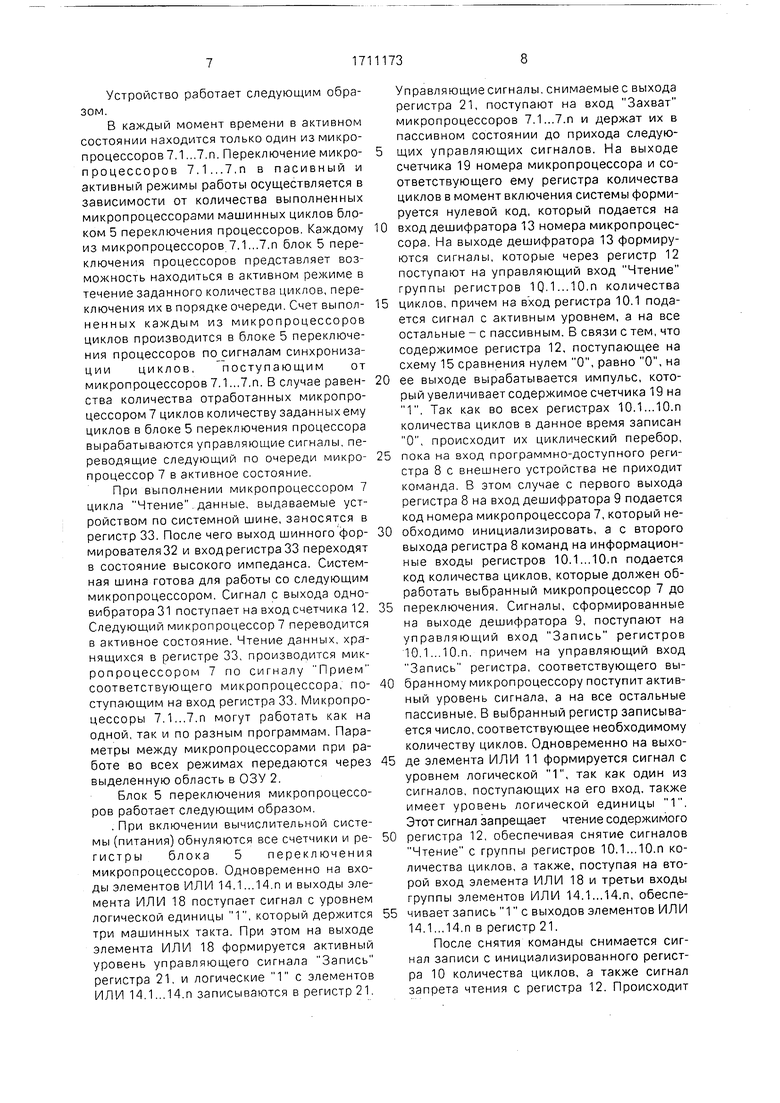

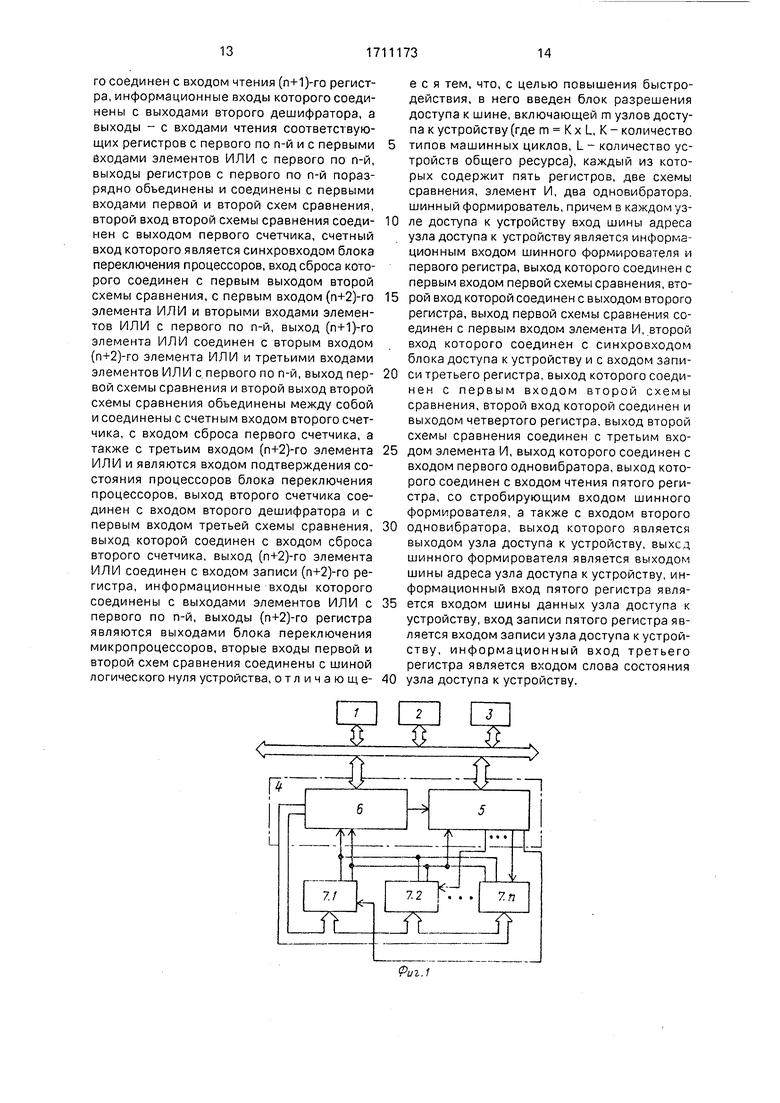

Блок 6 разрешения доступа к шине со- держит-m узлов 22.1...22.т доступа к устройству (фиг. 3).

Узел 22 доступа к устройству содержит

регистры 23, 24, 27, 28. 33, схемы 25, 29 сравнения, элемент И 26, одновибраторы 30 и 31, шинный формирователь 32.

Вход шины адреса узла 22 доступа к

устройству является информационным входом шинного формирователя 32 и регистра 27. Выход регистра 27 соединен с первым входом схемы 29 сравнения, Второй вход которой соединен с выходом регистра 28.

Выход схемы 29 сравнения соединен с первым входом элементов И 26, второй вход которого соединен с синхровходом узла доступа к устройству и с входом записи регистра 23. Выход регистра 23 соединен с

первым входом второй схемы 25 сравнения. Второй вход которой соединен с выходом регистра 24. Выход второй схемы 25 сравнения соединен с третьим входом элемента И 26. которого соединен с входом одновибратора 30. Выход которого соединен с входом чтения регистра 33 и со стробирую- щим входом шинного формирователя 32, а также с входом одновибратора 31. Выход которого является выходом узла 22 доступа

к устройству, выход шинного формирователя 32 является выходом шины адреса узла 22 доступа к устройству. Информационный вход регистра 33 является входом шины данных узла 22 доступа к устройству. Вход

записи регистра 33 является входом записи узла 22 доступа к устройству. Информационный вход регистра 27 является входом слова состояния узла 22 доступа к устройству.

Устройство работает следующим образом.

В каждый момент времени в активном состоянии находится только один из микропроцессоров 7.1 ...7.п. Переключение микро- процессоров 7.1...7.П в пасивный и активный режимы работы осуществляется в зависимости от количества выполненных микропроцессорами машинных циклов блоком 5 переключения процессоров. Каждому из микропроцессоров 7.1...7.п блок 5 переключения процессоров представляет возможность находиться в активном режиме в течение заданного количества циклов, переключения их в порядке очереди. Счет выпол- ненных каждым из микропроцессоров циклов производится в блоке 5 переключения процессоров по сигналам синхронизации циклов, поступающим от микропроцессоров 7.1 ...7.п. В случае равен- ства количества отработанных микропроцессором циклов количеству заданных ему циклов в блоке 5 переключения процессора вырабатываются управляющие сигналы, переводящие следующий по очереди микро- процессор 7 в активное состояние.

При выполнении микропроцессором 7 цикла Чтение .данные, выдаваемые устройством по системной шине, заносятся в регистр 33. После чего выход шинного фор- мирователя32 и вход регистра 33 переходят в состояние высокого импеданса. Системная шина готова для работы со следующим микропроцессором. Сигнал с выхода одно- вибратора31 поступает на вход счетчика 12. Следующий микропроцессор 7 переводится в активное состояние. Чтение данных, хранящихся в регистре 33, производится микропроцессором 7 по сигналу Прием соответствующего микропроцессора, по- ступающим на вход регистра 33. Микропроцессоры 7.1...7.П могут работать как на одной, так и по разным программам. Параметры между микропроцессорами при работе во всех режимах передаются через выделенную область в ОЗУ 2.

Блок 5 переключения микропроцессоров работает следующим образом.

. При включении вычислительной системы (питания) обнуляются все счетчики и ре- гистры блока 5 переключения микропроцессоров. Одновременно на входы элементов ИЛИ 14.1...14.П и выходы элемента ИЛИ 18 поступает сигнал с уровнем логической единицы 1, который держится три машинных такта. При этом на выходе элемента ИЛИ 18 формируется активный уровень управляющего сигнала Запись регистра 21, и логические 1 с элементов ИЛИ 14.1...14.П записываются в регистр 21.

Управляющие сигналы, снимаемые с выхода регистра 21, поступают на вход Захват микропроцессоров 7.1...7.П и держат их в пассивном состоянии до прихода следующих управляющих сигналов. На выходе счетчика 19 номера микропроцессора и соответствующего ему регистра количества циклов в момент включения системы формируется нулевой код, который подается на вход дешифратора 13 номера микропроцессора. На выходе дешифратора 13 формируются сигналы, которые через регистр 12 поступают на управляющий вход Чтение группы регистров 1Q.1...10.n количества циклов, причем на вход регистра 10.1 подается сигнал с активным уровнем, а на все остальные - с пассивным. В связи с тем, что содержимое регистра 12, поступающее на схему 15 сравнения нулем О, равно О, на ее выходе вырабатывается импульс, который увеличивает содержимое счетчика 19 на 1. Так как во всех регистрах 10.1...Ю.п количества циклов в данное время записан О, происходит их циклический перебор, пока на вход программно-доступного регистра 8 с внешнего устройства не приходит команда. В этом случае с первого выхода регистра 8 на вход дешифратора 9 подается код номера микропроцессора 7, который необходимо инициализировать, а с второго выхода регистра 8 команд на информационные входы регистров 10.1...Ю.п подается код количества циклов, которые должен обработать выбранный микропроцессор 7 до переключения. Сигналы, сформированные на выходе дешифратора 9, поступают на управляющий вход Запись регистров 10.1...Ю.п, причем на управляющий вход Запись регистра, соответствующего выбран ному микропроцессору поступит активный уровень сигнала, а на все остальные пассивные. В выбранный регистр записывается число, соответствующее необходимому количеству циклов. Одновременно на выходе элемента ИЛИ 11 формируется сигнал с уровнем логической 1, так как один из сигналов, поступающих на его вход, также имеет уровень логической единицы 1. Этот сигнал запрещает чтение содержимого регистра 12, обеспечивая снятие сигналов Чтение с группы регистров 10.1...Ю.п количества циклов, а также, поступая на второй вход элемента ИЛИ 18 и третьи входы группы элементов ИЛИ 14.1...14.П, обеспечивает запись 1 с выходов элементов ИЛИ 14.1...14.П в регистр 21.

После снятия команды снимается сигнал записи с инициализированного регистра 10 количества циклов, а также сигнал запрета чтения с регистра 12. Происходит

перебор регистров 10.1...10.П, пока не выбирается регистр, в котором записан не О. При этом в регистр 21с выходов регистра 12 записывается код номера, соответствующего этому регистру количество циклов микро- процессора и управляющим сигналом, сформированным на выходе регистра 21, этот микропроцессор 7 переходит в активное состояние. Инициализация остальных регистров 10.1...10.П количества циклов происходит аналогично. Разница состоит лишь втом, что команды формируются программным путем с помощью уже инициализированного микропроцессора.

Работу устройства приоритета состоящего из блока 5 переключения микропроцессоров и блока 6 разрешения доступа к шине рассмотрим на примере двухпроцессорной системы на базе микропроцессора серии К580 с поцикловым переключением процессоров.

Пусть в начальный момент времени работает первый процессор, содержимое счетчика 17 циклов равно О. Тогда в счетчик 19 записывается код, соответствующий первому процессору, а с помощью дешифратора 13 и регистра 12 чтение куоличества необходимых для выполнения микропроцессора 7.1 циклов осуществляется с регистра 10 количества циклов. В приведенном случае количество циклов, записанное в регистры 10.1 и 10.2 равно 1. После прихода с первого микропроцессора 7.1 на вход счетчика 17 сигнала синхронизации циклов содержимое последнего увеличивается на 1. При равенстве содержимого в счетчике 17 и регистре 10.1 количества циклов (в приведенном случае после прихода первого сигнала синхронизации циклов) счетчик 17 обнуляется сигналом с первого выхода схемы 16 сравнения, а на выход счетчика 19 поступает сигнал, увеличивающий содержимое на 1, т.е. на вход дешифратора 13 подается код номера следующих по порядку микропроцессора 7 и регистра 1.0. Одновременно с этим сигналом с первого выхода схемы 16 сравнения с помощью элемента I/IJTH 18 элементов ИЛИ 14.1...14.П во все разряды регистра 21 записывается 1, все микропроцессоры переводятся в пассивное состояние. После снятия сигнала с первого выхода схемы 16 сравнения в регистр 21 через элементы ИЛИ 14.1...14.п записывается код номера следующего микропроцессора, который перейдет в активное состояние и остальные останутся в пассивном. Дальнейшая работа системы осуществляется аналогично описанной. Разница состоит лишь в том, что в случае превышения максимального номера микропроцессора 7

с первого выхода схемы 20 сравнения на второ й вход счетчика 19 поступает сигнал, обнуляющий последний, т.е. на вход дешифратора 13 в этом случае подается код первого микропроцессора 7.

Если командой работающего микропроцессора 7 является команда изменения содержимого одного из регистров- 10.1...10.П количества циклов, .в этом случае система

0 работает следующим образом.

При поступлении команды в регистр 8 на выходе дешифратора 9 устанавливается код номера регистра количества циклов, содержимое которого требуется изменить. Да5 лее аналогично работе системы в режиме инициализации.

При выполнении очередного машинного цикла микропроцессором 7 вычислительной системы при поступлении адреса и

0 состояния на регистры 23 и 27 одного из узлов 22 доступа к устройству по сигналу синхронизации циклов Синхро сравниваются с заданным в регистрах 28 и 23. В . случае выполнения условия сравнения (рав5 ны, больше или меньше и т.д.) со схем сравнения 29 и 25 поступят сигналы на входы элемента И 26 и по приходу сигнала синхронизации циклов Синхро, с выхода элемента И 26 на вход одновибратора 3.0 поступит

0 сигнал. С выхода одновибратора 30 сигнал поступит на вход шинного формирователя 32, с выхода которого на устройство в данном машинном цикле производится обращение, поступает его адрес и сигнал

5 Прием. По этим сигналам с выхода данного устройства поступят сигналы данных на вход регистра 33 и по сигналу с одновибратора 30 заносятся в регистр 33. Таким образом в регистре 33 хранятся данные, которые

0 по сигналу Прием активного микропроцессора 7 выдаются с регистра 33 на шину данных микропроцессора. Входы шины данных регистра 33 и выход шинного формирователя 32 при пассивном уровне сигна5 ла с выхода одновибратора 30 находятся в высокоимпедансном состоянии. Длительности сигнала на выходах одновибраторов 30 и 31 выбираются с учетом быстродействия устройства, к которому данный блок 22 раз0 решает обращения. Сигнал с выхода одно- вибратора 30 поступает также на вход одновибратора 31, с выхода которого сигнал активного уровня поступает на вход блока 5 переключения микропроцессоров или счет5 ный вход счетчика 19 и вход сброса счетчика 17. После чего следующий микропроцессор перейдет в активное состояние и т.д. Используя функциональные возможности предложенного устройства, при создании вычислительной системы можно упростить

создание программного обеспечения, снизить стоимость и повысить его эффективность. Покажем это на примере следующих режимов работы процессоров, использующих общую шину доступа.

Режим параллельного выполнения нескольких программ. При работе системы в этом режиме каждый процессор работает по своей программе. Командами Управление распределяются вычислительные ресурсы, доступ к которым производится по общей шине между программами. Такой режим используется для одновременного решения нескольких задач (одновременная работа нескольких внешних устройств, приводов и т.д.), доступ к которым происходит по общей шине.

В случае создания системы с несколькими одновременно работающими устройствами, имеющими общую шину доступа, предложенная система позволяет обеспечить управление всеми устройствами по одной программе, т.е. каждый процессор управляет работой своего устройства, используя Общую программу. Количество управляемых устройств ограничивается только вычислительной мощностью системы, которая должна удовлетворять быстродействию всех одновременно работающих устройств.

Режим параллельного выполнения несколькими процессорами одной программы. Используя возможность работы вычислительной системы с переключением процессоров после каждого машинного цикла, этот режим работы системы позволяет создавать аппаратно-программные средства для проведения диагностики, тестирования, ремонтно-отладочных работ. Неисправность одного из процессоров определяется путем сравнения результатов их работы после каждого машинного цикла. В этом режиме можно определять неисправность, возникшую при выполнении определенного цикла, что дает возможность локализовать неисправность до элемента или группы элементов неисправного модуля. При этом программа тестирования процессоров , прииспользовании предложенной системы обладает простотой, а время нахождения неисправности уменьшается. Диагностику и тестирование можно проводить на группе процессоров, при этом другая группа процессоров, может решать практические задания. Возможность работы системы в таком режиме позволяет повысить ее надежность и ремонтопригодность, так как обеспечивает поцикловый контроль правильности выполнения команд.

Режим попеременной работы процессоров. Этот режим работы используется для попеременного решения задач. Для любых программ, где решение одной программы

требует решения другой, такой режим работы предложенной многопроцессорной вычислительной системы увеличивает эффективность программного обеспечения. Повышение эффективности программного

0 обеспечения при использовании такого режима работы показана на примере обработки прерывания.

Реакция на прерывание начинается с загрузки содержимого регистров процессо5 ров в стек, за которым следует инициализация - загрузка в регистры новой информации, необходимой для работы программы обслуживания прерывания. После ее окончания происходит восстановление

0 содержимого регистров процессора. Время упрятывания - восстановления непроизводительно теряется, а время инициализации процессора задерживает начало обслуживания прерываний.

5При обработке прерываний специальным процессором исключаются потери времени на управление-восстановление. В результате появления прерывания процессор, обрабатывающий прерывания, выдает

0 команду управления в блок управления переключением процессоров и тот предоставляет ему всю часть вычислительной мощности шины. Обработка прерываний производится как с приостановлением, так

5 и без приостановления параллельно выполняющихся программ.

Предлагаемое устройство позволяет осуществить параллельную работу микропроцессоров с максимальным использова0 нием быстродействия устройств общего ресурса.

Формулаизобретения Устройство приоритетного доступа к общей шине, содержащее блок переключения

5 процессоров, содержащий программно-доступный регистр, первый и второй дешифраторы, (п+2) регистров (п - количество микропроцессоров), первую, вторую и третью схемы сравнения, первый и второй

0 счетчики, (п+2) элемента ИЛИ, причем информационный вход блока переключения процессоров является информационным входрм программно-доступного регистра, а первый и второй выходы последнего соеди5 нены соответственно с входом первого дешифратора и информационными входами регистров, с первого по n-й, входы записи которых соединены с соответствующими выходами первого дешифратора и с входами (п+1)-го элемента ИЛИ, выход последнего соединен с входом чтения (п+1)-го регистра, информационные входы которого соединены с выходами второго дешифратора, а выходы - с входами чтения соответствующих регистров с первого по n-й и с первыми входами элементов ИЛИ с первого по п-й, выходы регистров с первого по n-й поразрядно объединены и соединены с первыми входами первой и второй схем сравнения, второй вход второй схемы сравнения соеди- нен с выходом первого счетчика, счетный вход которого является синхровходом блока переключения процессоров, вход сброса кото- рого соединен с первым выходом второй схемы сравнения, с первым входом (п+2)-го элемента ИЛИ и вторыми входами элементов ИЛИ с первого по n-й, выход (п+1)-го элемента ИЛИ соединен с вторым входом (п+2)-го элемента ИЛИ и третьими входами элементов ИЛИ с, первого по n-й, выход пер- вой схемы сравнения и второй выход второй схемы сравнения объединены между собой и соединены с счетным входом второго счетчика, с входом сброса первого счетчика, а также с третьим входом (п+2)-го элемента ИЛИ и являются входом подтверждения состояния процессоров блока переключения процессоров, выход второго счетчика соединен с входом второго дешифратора и с первым входом третьей схемы сравнения, выход которой соединен с входом сброса второго счетчика, выход (п+2)-го элемента ИЛИ соединен с входом записи (п+2)-го регистра, информационные входы которого соединены с выходами элементов ИЛИ с первого по n-й, выходы (п+2)-го регистра являются выходами блока переключения микропроцессоров, вторые входы первой и второй схем сравнения соединены с шиной логического нуля устройства, отличающе-

вся тем, что, с целью повышения быстродействия, в него введен блок разрешения доступа к шине, включающей m узлов доступа к устройству (где m К х L, К - количество типов машинных циклов, L - количество устройств общего ресурса), каждый из которых содержит пять регистров, две схемы сравнения, элемент И, два одновибратора, шинный формирователь, причем в каждом узле доступа к устройству вход шины адреса узла доступа к устройству является информационным входом шинного формирователя и первого регистра, выход которого соединен с первым входом первой схемы сравнения, второй вход которой соединен с выходом второго регистра, выход первой схемы сравнения соединен с первым входом элемента И,.второй вход которого соединен с синхровходом блока доступа к устройству и с входом записи третьего регистра, выход которого соединен с первым входом второй схемы сравнения, второй вход которой соединен и выходом четвертого регистра, выход второй схемы сравнения соединен с третьим входом элемента И, выход которого соединен с входом первого одновибратора, выход которого соединен с входом чтения пятого регистра, со стробирующим входом шинного формирователя, а также с входом второго одновибратора, выход которого является выходом узла доступа к устройству, выход шинного формирователя является выходом шины адреса узла доступа к устройству, информационный вход пятого регистра является входом шины данных узла доступа к устройству, вход записи пятого регистра является входом записи узла доступа к устройству, информационный вход третьего регистра является входом слова состояния узла доступа к устройству.

--v i

гг / гг.ггг/Л

| Устройство приоритета | 1982 |

|

SU1080144A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР .№ 1415950, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-02-07—Публикация

1990-01-16—Подача