3150

Изобретение относится к электронике и может использоваться в быстродействующих и высоковольтных усилителях и компараторах напряже-

НИИ.

Цель изобретения - расширение диапазона входных дифференциальных сигналов.

На чертеже представлена принципи- альная электрическая схема дифференциального усилителя.

Дифференциальный усилитель содержит первый-двенадцатый транзисторы 1-12 соответственно, первый и второй нагрузочные элементы -13, 14, первый и второй делители 15, 16, первый-шестой источники тока, выполненные на транзисторах 17-22, генераторах 23-28 тока, первую и вторую шины 29, 30 источника питания.

Дифференциальный усилитель работает следующим образом.

Входной сигнал поступает на входные эмиттерные повторители, выполненные на восьмом и двенадцатом .транзисторах 8, 12, режимные токи которых задаются третьим и шее- тым источниками тока на транзисторах 19, 22. Режимные токи этих, а также первого и четвертого источников тока на транзисторах 17, 20 выбираются таким образом, чтобы обеспечить малый входной ток смещения, необходимые коэффициент передачи и быстродействие дифференциального усилителя в широком рабочем диапазоне, в т.ч. при существенном уменьшении коэффициентов передачи тока базы транзисторов и изменении питающих и входных напряжений.

Ясно, что одновременно выполнить эти условия с эмиттерным повторителем легче, чем в собственно дифференциальном каскаде. Кроме того, использование транзисторов 19, 22 и седьмого и одиннадцатого транзисторов 7, 11, режим по напряжению которых задается при помощи первого и второго делителей 15, 16 соответственно, позволяет уменьшить примерно в два раза максимальные напряжения между коллектором и эмиттером транзисторов. Это в свою очередь позволет применять транзисторы с меньшими пробивными напряжениями, но с боль

шими коэффициентами передачи тока базы, что также способствует увеличению точности дифференциального усилителя. Для этой же цели предназначены и цепи, выполненные на первом шестом, девятом, десятом транзисторах 1-6, 9, 10, а также транзисторах 24, 27, режим по току которых определяется вторым и пятым генераторами 24, 27 тока. Источник тока смещения дифференциального каскада на первом- четвертом транзисторах 1-4, выполнен на транзисторах 17, 20 с генераторам 23, 26 тока, что позволяет обеспечит допустимые напряжения на транзистора первого и четвертого источников тока смещения при различных сочетаниях синфазного и парафазного сигналов на входах дифференциального усилителя.

При анализе сделаны следующие допущения.

Допустимое напряжение на коллекторном переходе всех транзисторов изменяется в следующих пределах:

, где Е +V „ /-Vi.n/;

21,, 21,,,

где и токи генераторов тока,

( + I,, )R UV,

где R - резистор в цепи коллектора

транзистора 4(3), bV - падение напряжения на открытом эмиттерном переходе любого из транзисторов или диоде.

V V + V V ех( с-ф (f ехг

V - V J v

где V( - синфазный входной сигнал, Уяц) - половина дифференциального входного сигнала.

Транзисторы, у которых будет происходить увеличение напряжения , следующие: 1, 3, 18, 17, 9, 19, 10, 11, 12.

Поскольку .j: rV,g,,; V ,

: ,(,, , ,),

проанализируем V , , и ,, .

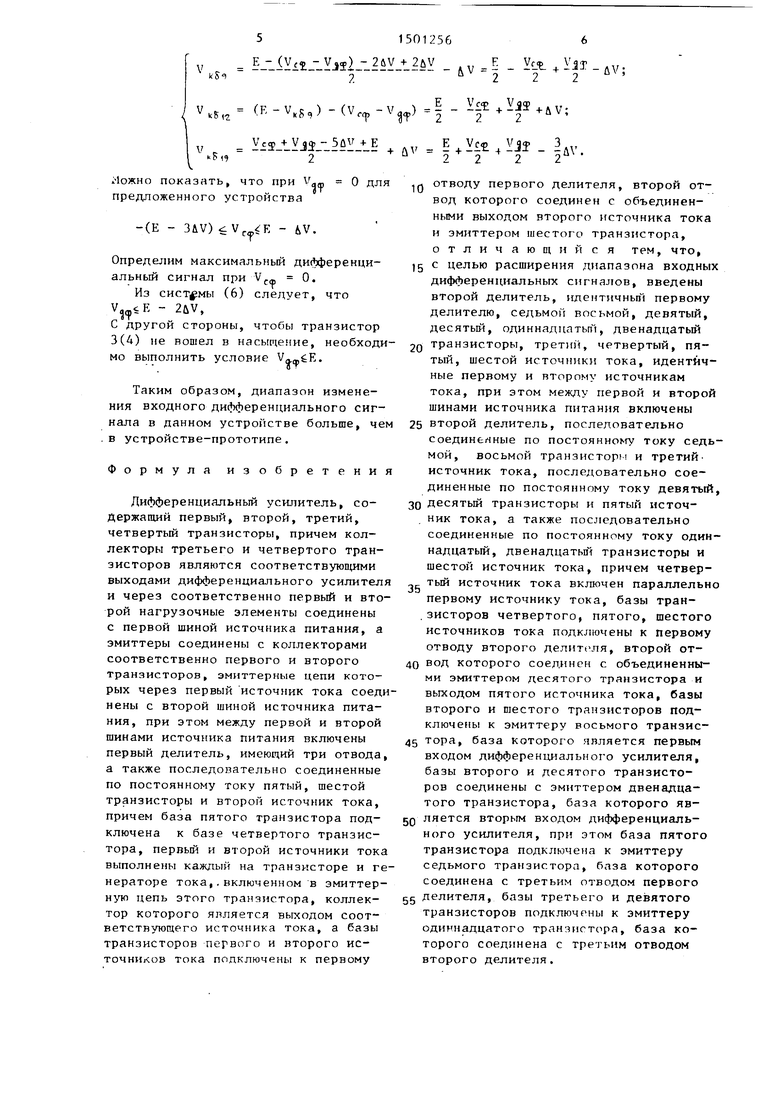

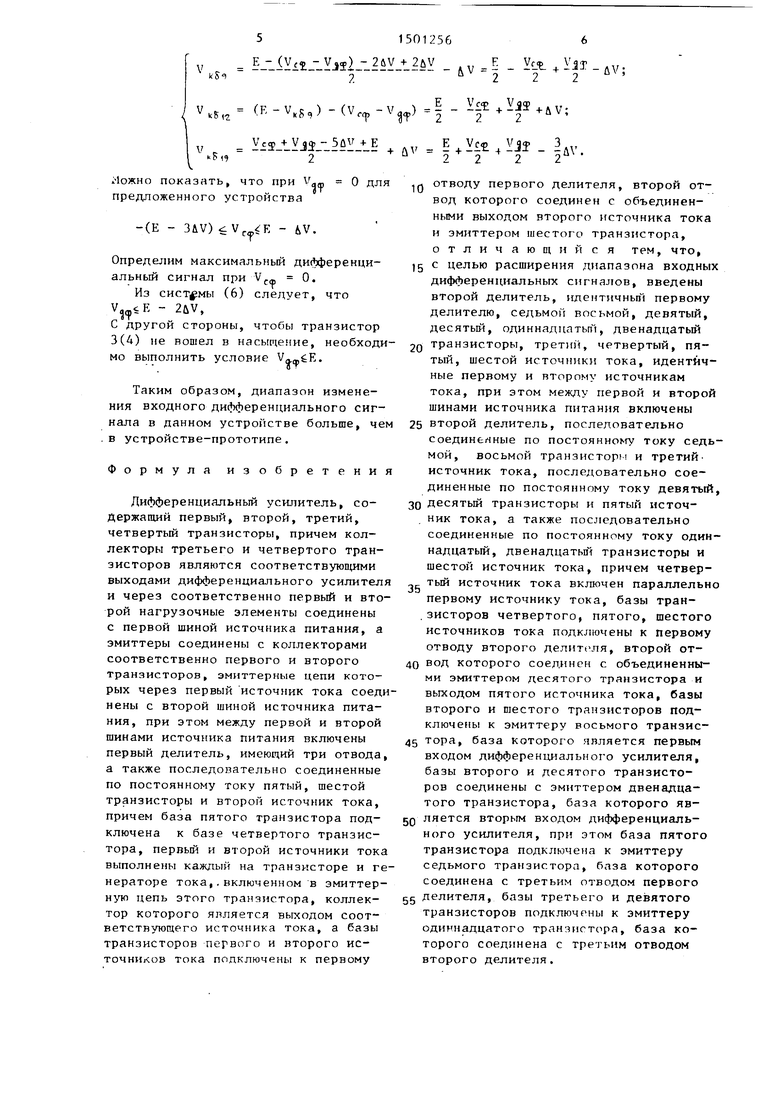

515012566

V ()--2uV t2uY v - - - uv;

V.,,, (F,-V,s,)-(V.-V) f .AV;

v ..E , ,„ I .Yf 4Yf - |uv.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дифференциальный усилитель (его варианты) | 1981 |

|

SU1045349A1 |

| Коммутатор | 1975 |

|

SU832721A1 |

| Балансный модулятор | 1980 |

|

SU907765A1 |

| Усилитель | 1980 |

|

SU987795A1 |

| Балансный модулятор | 1980 |

|

SU904197A1 |

| УСТРОЙСТВО С ОТРИЦАТЕЛЬНЫМ СОПРОТИВЛЕНИЕМ | 2000 |

|

RU2175165C1 |

| Усилитель мощности | 1989 |

|

SU1635250A1 |

| УСТРОЙСТВО ПОДДЕРЖАНИЯ РЕЖИМА РАБОТЫ ПО ПОСТОЯННОМУ ТОКУ УСИЛИТЕЛЯ | 2001 |

|

RU2207712C2 |

| Формирователь импульсов управления | 1985 |

|

SU1290501A1 |

| Устройство для интегрирования произведения двух сигналов | 1984 |

|

SU1211764A1 |

Изобретение относится к электронике. Цель изобретения - расширение диапазона входных дифференциальных сигналов. Дифференциальный усилитель содержит транзисторы 1-12, нагрузочные эл-ты 13, 14, делители 15 и 16, источники тока, выполненные на транзисторах 17-22 и г-рах 23-28 тока, источник питания с шинами 29 и 30. Цель достигается выбором режимных токов транзисторов таким образом, чтобы обеспечить малый входной ток смещения, необходимые коэф. передачи и быстродействие дифференциального усилителя в широком рабочем диапазоне, в том числе при существенном уменьшении коэф. передачи тока базы транзисторов и изменении питающих и входных напряжений. 1 ил.

Ложно показать, что при Удд, О для предложенного устройства

-(Е - 3AV) V.F - i,V.

Определим максимальный дифференциальный сигнал при Vf- О,

Из сисТ(рмы (6) следует, что V,E - 2uV,

С другой стороны, чтобы транзистор 3(4) не вошел в насыщение, необходимо выполнить условие У,бЕ.

Таким образом, диапазон изменения входного дифференциального сигнала в данном устройстве больше, чем в устройстве-прототипе.

Формула изобретения

Дифференциальный усилитель, содержащий первый, второй, третий, четвертый транзисторы, причем коллекторы третьего и четвертого транзисторов являются соответствуюпщми выходами дифференциального усилителя и через соответственно первый и второй нагрузочные элементы соединены с первой шиной источника питания, а эмиттеры соединены с коллекторами соответственно первого и второго транзисторов, эмиттерные цепи которых через первый источник тока соединены с второй шиной источника питания, при этом между первой и второй шинами источника питания включены первый делитель, имеющий три отвода, а также последовательно соединенные по постоянному току пятый, шестой транзисторы и второй источник тока, причем база пятого транзистора подключена к базе четвертого транзистора, первый и второй источники тока выполнены каждый на транзисторе и генераторе тока,.включенном в эмиттер- ную цепь этого транзистора, коллектор которого является выходом соответствующего источника тока, а базы транзисторов первого и второго источников тока подключены к первому

.,. отводу первого делителя, второй отвод которого соединен с объединенными выходом второго источника тока и эмиттером шестого транзистора, отличающийся тем, что,

15 с целью расширения диапазона входны дифференциальных сигналов, введены второй делитель, идентичньп) первому делителю, седьмой восьмой, девятый, десятый, одиннадцатьп, двенадцатый

20 транзисторы, третш ц четвертый, пятый, шестой источники тока, идентичные первому и второму источникам тока, при этом между первой и второй шинами источника питания включены

25 второй делитель, последовательно

соединенные по пocтoяннo ry току седьмой, восьмой транзисторы и третий- источник тока, последовательно соединенные по постоянному току девятый

30 десятый транзисторы и пятый источник тока, а также последовательно соединенные по постоянному току одиннадцатый, двенадцатьпЧ транзисторы и шестой источник тока, причем четвертый источник тока включен параллельн первому источнику тока, базы тран- .зисторов четвертого, пятого, шестого источников тока подключены к первому отводу второго делит(ля, второй от40 вод которого соединен с объединенными эмиттером десятого транзистора и выходом пятого источника тока, базы второго и шестого транзисторов подключены к эмиттеру восьмого транзис45 тора, база которого является первьгм входом дифференциального усилителя, базы второго и десятого транзисторов соединены с эмиттером двенадцатого транзистора, база которого яв- 5Q ляется вторым входом дифференциального усилителя, при этом база пятого транзистора подключена к эмиттеру седьмого транзистора, база которого соединена с третьим отводом первого gg делителя, базы третьего и девятого транзисторов подключены к эмиттеру одиннадцатого транзистора, база которого соединена с третьим отводом второго делтителя.

35

| Дифференциальный усилитель | 1984 |

|

SU1195415A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-08-15—Публикация

1987-06-01—Подача