1

Изобретение относится к аналоговой вычислительной технике и может быть использовано в электронной аппаратуре различного назначения, в частности в радиоприемных устройствах.

Известны балансные модуляторы, используемые в радиоприемных устройствах для преобразования спектра«сигналов, содержащие согласованные траазисторы, источники постоянного тока и нагрузочные резисторы ll.

Недостатком этих устройств является их малая линейность в диапазоне выходных токов, превьпиающих режимнь1Й ток устройства перемножения и, как следствие, маленький динамический диапазон выходных сигналов.

Наиболее близким по технической сущности к предлагаемому является балансный модулятор, содержащий первый и второй усилительные транзисторы, базы которых объединены и соединены с первым выходом дифференциального источника входного напряжения.

.третий и четвертый усилительные тран. зисторы, базы которых объединены и соединены со вторым выходом дифференциального источника входного напряжения, причем объединенные коллекторы первого н четвертого усилительных транзисторов и объединенные коллекторы второго и третьего усилительных транзисторов, являющиеся дифференциальными выходами модулятора, через

10 соответственно первый и второй нагрузочные резисторы подключены к источнику напряжения питания, причем эмиттеры первого и третьего усилительных транзисторов объединены и под15ключены к первому выходу первого дифференциального усилительного каскада, а эмиттеры второго и четвертого усилительных транзисторов объединены и подключены ко второму выхо30ду первого дифференциального усилительного каскада. Перемножаемые сигналы подаются между объединенными базами третьего и четвертого усилительных транзисторов, а также на входы первого дифференциального уси лительного каскада 2. Линейность такого балансного модулято-ра по входному сигналу, подаваемому на входы дифференциального усилительного каскада, при больших входных сигналах резко ухудшается .вследствие невозможности получить от дифференциального каскада выходной ток, превышающий его режимный ток, что значительно снижает динамический диапазон выходных сигналов увеличение динамического диапазона выходных сигналов сопряжено с повышением режимного тока модулятора и, следовательно, потребляемой им мощности. Цель изобретения - расширение динамического диапазона выходных си налов при одновременном- снижении потребляемой мощности. Поставленная цель достигается тем что в известный балансньй модулятор, содержащий дифференциальный источник входного напряжения, источник входного тока, два нагрузочных ре-зистора, источник напряжения питания, пер вый и второй усилительные транзисторы, базы которых объединены и подклю чены к первому выходу дифференциального источника входного напряжения, третий и четвертый усилительные тран зисторы, базы которых объединены и подключены ко второму выходу дифференциального источника входного напряжения, объединенные коллекторы первого и четвертого усилительных транзисторов и объединенные коллекторы второго и третьего усилительных транзисторов являются дифференциальными выходами модулятора и подключены соответственно через первый и второй нагрузочные резисторы ко входу источника напряжения питания, вве дены четырнадцать усилительных транзисторов, десять компенсационных транзисторов, четыре диодных нелинейных элемента с экспоненциальной характеристикой и шесть источников постоянного тока, причем эмиттер первого усилительного транзистора подключен к эмиттеру пятого усилительного транзистора и к эмиттеру первого компенсационного транзистора, эмиттер третьего усилительного транзистора подключен к эмиттеру шестого усилительного транзистор и к эмиттеру второго компенсационного транзистора, базы пятого усилительного транзистора и второго компенсационного транзистора объединены и подключены к коллектору второго компенсационного транзистора, базы шестого усилительного транзистора и первого компенсационного транзистора объединены и подключены к коллектору первого компенсационного транзистора, эмиттер второго усилительного транзистора подключен к эмиттеру восьмого усилительного транзистора и к эмиттеру третьего компенсационного транзистора, эмиттер четвертого усилительного транзистора подключен к эмиттеру четвеотого компенсационного транзистора и к эмиттеру седьмого усилительного транзистора, базы седьмого усилительного транзистора и третьего компенсационного транзистора объединены и подключены к коллектору третьего компенсационного транзистора, базы восьмого усилительного транзистора и четдертого компенсационного транзисто.ров объединены и подключены к коллектору четвертого компенсационного транзистора, коллекторы пятого, шестого, седьмого и восьмого усилительных транзисторов подключены к общей шине, коллекторы первого, второго, третьего и четвертого компенсационных транзисторов, соответственно, подключены к коллекторам девятого, десятого, одиннадцатого и двенадцатого усилительных транзисторов, эмиттеры девятого и десятого усилительных транзисторов объединены и подключены к эмиттеру тринадцатого усилительного транзистора и к эмиттеру пятого компенсационного транзистора, эмиттеры одиннадцатого и двенадцатого усилительных транзисторов .объединены и подключены к эмиттеру четырнадцатого усилительного транзистора и к эмиттеру шестого компенсационного транзистора, базы тринадцатого усилительного транзистора и шестого компенсационного транзистора объединены и подключены к коллектору шестого компенсационного транзистора и к первому выходу первого источника постоянного тока, базы четырнадцатого усилительного и пятого компенсационного транзисторов объединены и подключены к коллектору пятого компенсационного транзистора и к первому выходу второго источника постоянного тока, коллекторы тринадцатого и четырнадцатого усилительных транзисторов и вторые выходы первого и второго источников постоянного тока подключены к общей шине, базы девятого и десятого усилитель- 5 ных транзисторов объединены и подключены к аноду первого диодного нелинейного элемента, к катоду второго диодного нелинейного элемента и к первому выходу источника входного тока, 10 базы одиннадцатого и двенадцатого усилительных тра1зисторов объединены и подключены к аноду третьего диодного нелинейного элемента, к катоду четвертого диодного нели- 15 нейного элемента и ко второму выходу источника входного тока, катод первого диодного нелинейного элемента подключен к эмиттеру пятнадцатого усилительного транзистора и к эмит- 20 теру седьмого компенсационного транзистора, катод третьего диодного нелинейного элемента подключен к эмиттеру шестнадцатого усилительного транзистора и к эмиттеру восьмого ком-25 пенсационного транзистора, базы пятнадцатого усилительного транзистора и восьмого компенсационного транзистора объединены и подключены к коллектору во сьмого компенсационного транзис- Q тора и к первому выходу vpe- тьего источ-ника постоянного тока,

базы шестнадцатого усилительного транзистора и седьмого компенсационного транзистора объединены и ,е

VЗЭ

подключены к коллектору седьмого компенсационного транзистора и к первому выходу четвертоЬо источника постоянного тока, коллекторы пятнадцатого и шестнадцатого усилительных 40 транзисторов и вторые выходы третьего и четвертого источников постоянного напряжения подключены к общей шине, анод второго диодного нелинейного элемента подключен к эмит- ., теру семнадцатого усилительного транзистора и к эмиттеру девятого компенсационного транзистора, анод четвертого диодного нелинейного элемента подключен к э.1Siттepy восемнадцатого усилительного транзистора и к эмиттеру десятого компенсационного транзистора, базы семнадцатого усилительного транзистора и десятого, компенсационного транзистора объединены и подключены к коллектору десятого компенсационного транзистора и к первому выходу пятого источника постойного тока, базы

восемнадцатого усилительного и девятого компенсационного транзисторовобъединены и подключены к коллектору девятого компенсационного транзистора и к первому входу шестого источника постоянного тока, коллекторы семнадцатого и восемнадцатого усилительных транзисторов и вторые выходы пятого и шестого источников постоянного тока объединены и подключеш 1 к выходу источника напряжения питания.

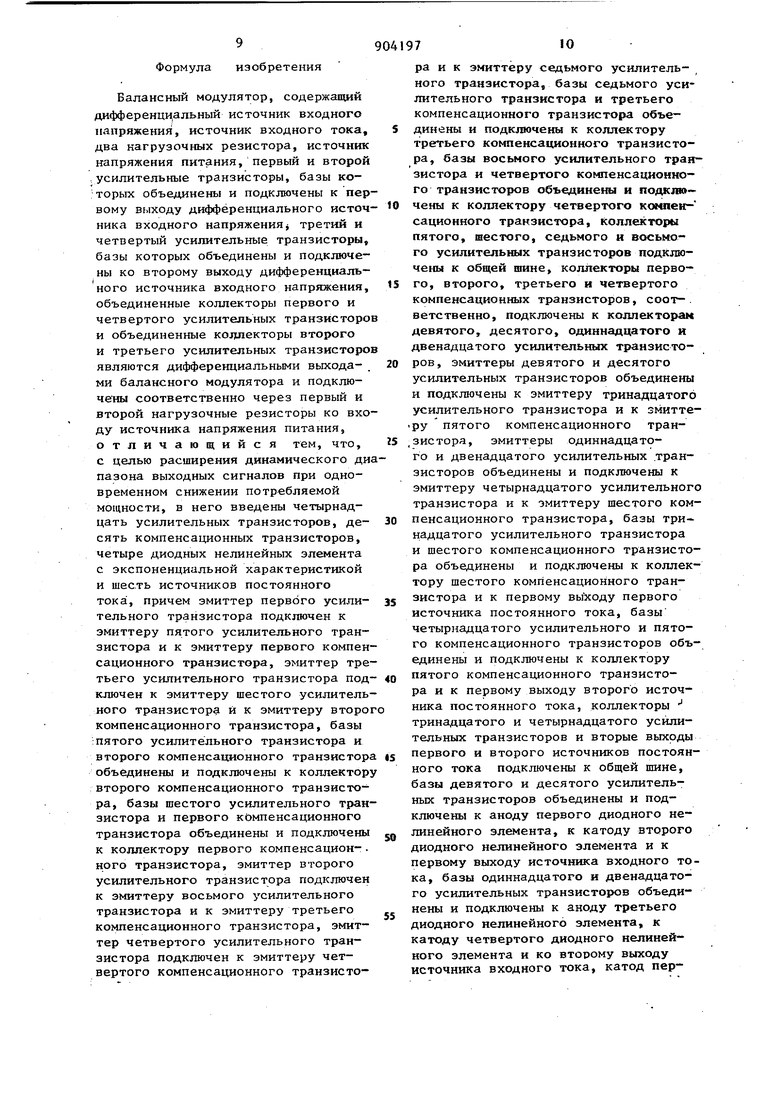

На чертеже приведена принципиальная электрическая схема балансного модулятора.

Балансный модулятор содержит усилительные транзисторы 1-18, компенсационные транзисторы 19-28, два нагрузочных резистора 29 и 30, шесть источников 31-36 постоянного тока, четыре диодных нелинейных элемента 3740, источник 41 входного тока и источник 42 входного напряжения.

Балансный модулятор работает следующим образом. Входной ток от первого источника 41 входного тока поступает на транзисторы 15-18, 21-28, диодные нелинейные элементы 37-40 и источники 33-36 постоянного тока. При этом между выходами источника 41 входного тока создается дифференциальное напряжение doutp , равное

Uau,p. U 2 f S h ( 1 )

где Зр- тепловой потенциал;

Зо(- величина режимного тока, задаваемого каждым из источников 33-36 постоянного тока.

Дифференциальное напряжение Uouqs.o, будучи приложенным между объединенными базами усилительных транзисторов 9 и 10 и объединенными базами усилительных транзисторов 11 и 12, вызывает протекание через коллекторы этих транзисторов токов, удовлетворяющих соотношения

. ; к„ к г;3кр-3ц, 3о sh

где Нт тепловой потенциал;

;jo - величина режимного тока, задаваемого каждым из источников 31 и 32 постоянного тока; ток коллектора транзистог

ikg

ра 9;

3«до

ток коллектора транзистора 10;

Формула изобретения

Балансный модулятор, содержащий дифференци альный источник входного напряжения, источник входного тока, два нагрузочных резистора, источник напряжения питания, первый и второй усилительные транзисторы, базы которых объединены и подключены к первому В 1ходу дифференциального источника входного напряженияj третий и четвертый усилительные транзисторы, базы которых объединены и подключены ко второму выходу дифференциального источника входного напряжения, объединенные коллекторы первого и четвертого усилительных транзисторов и объединенные кoJщeктopы второго и третьего усилительных транзисторов являются дифференциальными выхода- . ми балансного модулятора и подключены соответственно через первый и второй нагрузочные резисторы ко входу источника напряжения питания, отличающийся тем, что, с целью расширения динамического диапазона выходных сигналов при одновременном снижении потребляемой мощности, в него введены четырнадцать усилительных транзисторов, десять компенсационных транзисторов, четыре диодных нелинейных элемента с экспоненциальной характеристикой и шесть источников постоянного тока, причем эмиттер первого усилительного транзистора подключен к эмиттеру пятого усилительного транзистора и к эмиттеру первого компенсационного транзистора, эмиттер третьего усилительного транзистора подключей к эмиттеру шестого усилительного транзистора и к эмиттеру второг компенсационного транзистора, базы :пятого усилительного транзистора и второго компенсационного транзистора объединены и подключены к коллектору второго компенсационного транзистора, базы шестого усилительного транзистора и первого компенсационного транзистора объединены и подключены к коллектору первого компенсацион-. нрго транзистора, эмиттер второго усилительного транзистора подключен к эмиттеру восьмого усилительного транзистора и к эмиттеру третьего компенсационного транзистора, эмиттер четвертого усилительного транзистора подключен к эмиттеру четвертого компенсационного транзистора и к эмиттеру седьмого усилительного транзистора, базы седьмого усилительного транзистора и третьего компенсационного транзистора объединены и подключены к коллектору третьего компенсационного транзистора, базы восьмого усилительного транзистора и четвертого компенсационного транзисторов о6ъе;динены и подклю- чены к коллектору четвертого компен- сационного транзистора, коллекторы пятого, шестого, седьмого и восьмого усилительных транзисторов подключены к общей шине, коллекторы первого, второго, третьего и четвертого компенсационных транзисторов, соот-. ветственно, подключены к кохшекторам девятого, десятого, одиннадцатого и двенадцатого усилительных транзисторов, эмиттеры девятого и десятого усилительных транзисторов объединены и подключены к эмиттеру тринадцатого усилительного транзистора и к змиттеру пятого компенсационного тран,зистора, эмиттеры одиннадцатого и двенадцатого усилительных .транзисторов объединены и подключены к эмиттеру четырнадцатого усилительног транзистора и к эмиттеру шестого компенсационного транзистора, базы тринадцатого усилительного транзистора и шестого компенсационного транзистора объединены и подключены к коллектору шестого компенсационного транзистора и к первому выходу первого источника постоянного тока, базы четырнадцатого усилительного и пятого компенсационного транзисторов объединены и подключены к коллектору пятого компенсационного транзистора и к первому выходу второго источника постоянного тока, коллекторы тринадцатого и четырнадцатого усилительных транзисторов и вторые выходы первого и второго источников постоянного тока подключены к общей шине, базы девятого и десятого усилительных транзисторов объединены и подключены к аноду первого диодного нелинейного элемента, к катоду второго диодного нелинейного элемента и к первому выходу источника входного тока, базы одиннадцатого и двенадцатого усилительных транзисторов объединены и подключены к аноду третьего диодного нелинейного элемента, к катоду четвертого диодного нелинейного элемента и ко второму выходу источника входного тока, катод пер

| название | год | авторы | номер документа |

|---|---|---|---|

| Балансный модулятор | 1980 |

|

SU907765A1 |

| Дифференциальный усилитель (его варианты) | 1981 |

|

SU1045349A1 |

| Аналоговый перемножитель | 1989 |

|

SU1709353A1 |

| Операционный усилитель | 1983 |

|

SU1160530A1 |

| Усилитель мощности | 1989 |

|

SU1635250A1 |

| Усилитель | 1980 |

|

SU987795A1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2007 |

|

RU2349024C1 |

| Устройство для интегрирования произведения двух сигналов | 1984 |

|

SU1211764A1 |

| ГЕНЕРАТОР ХАОТИЧЕСКИХ КОЛЕБАНИЙ | 2004 |

|

RU2273088C1 |

| Программируемый приемник сигналов для коммутационных сред | 1988 |

|

SU1718236A1 |

Авторы

Даты

1982-02-07—Публикация

1980-06-30—Подача