J2) / 3

вь/ход

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножающий цифро-аналоговый преобразователь | 1985 |

|

SU1312738A1 |

| Цифроаналоговый преобразователь | 1986 |

|

SU1367159A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1398099A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1374431A1 |

| Умножающий цифро-аналоговый преобразователь | 1986 |

|

SU1441481A1 |

| Блок кодоуправляемого импеданса | 1989 |

|

SU1649571A1 |

| Устройство цифроаналогового преобразования | 1987 |

|

SU1524180A1 |

| Следящий функциональный преобразователь | 1976 |

|

SU634308A1 |

| Множительно-делительное устройство | 1980 |

|

SU902026A1 |

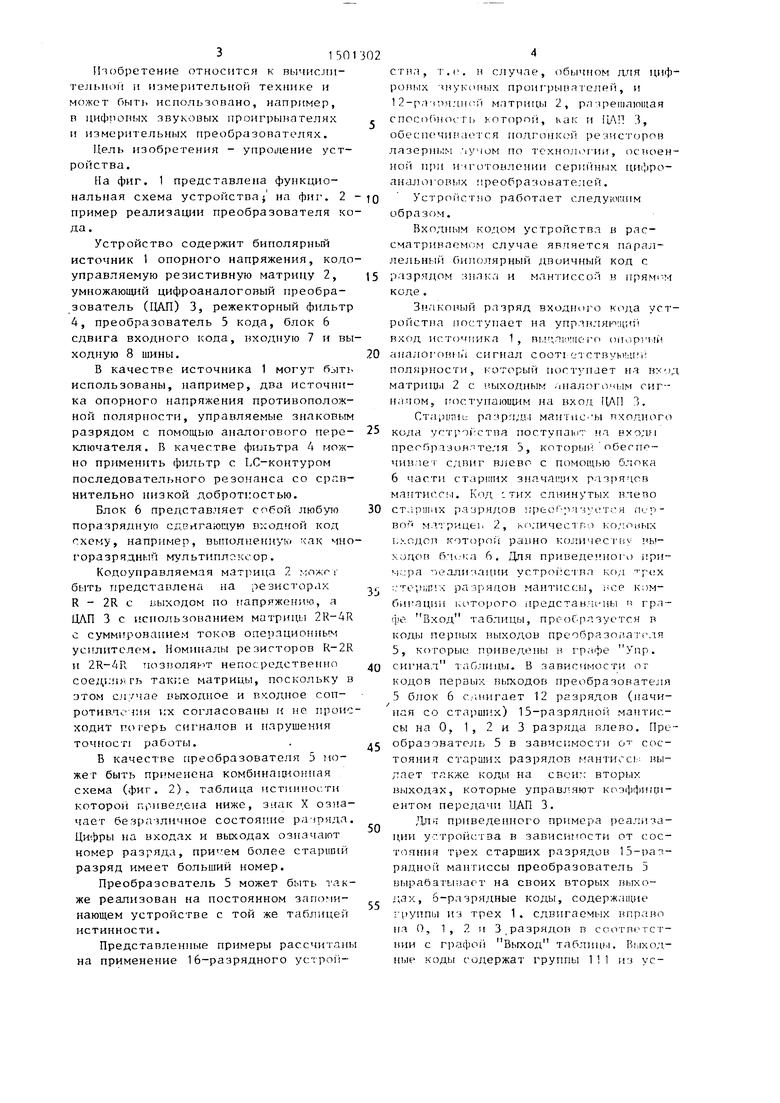

Изобретение относится к вычислительной и измерительной технике и может быть использовано, например, в цифровых звуковых проигрывателях и измерительных преобразователях. Цель изобретения - упрощение устройства. Устройство содержит биполярный источник 1 опорного напряжения, кодоуправляемую резистивную матрицу 2, умножающий цифроаналоговый преобразователь 3, режекторный фильтр 4, преобразователь 5 кода, блок 6 сдвига входного кода, входную 7 и выходную 8 шины. Цель изобретения достигается за счет получения аналогового эквивалента, начиная со старшего значащего разряда, с последующим масштабированием в зависимости от старших разрядов входного кода и фильтрацией полученного аналогового сигнала. 2 ил.

(fual

31 5П

изобретение относится к вычислительной и измерительной технике и может быть использовано, например, в ИИФТ1ОПЫХ звуковых проигрывателях и измерительных преобразователях.

Цель изобретения - упрощение устройства.

На фиг. 1 представлена функциональная схема устройства j на фиг. 2 пример реализации преобразователя кода.

Устройство содержит биполярный источник 1 опорного напряжения, кодо управляемую резистивную матрицу 2, умножающий цифроаналоговый преобразователь (ЦДЛ) 3, режекторный фильтр 4, преобразователь 5 кода, блок 6 сдвига входного кода, входную 7 и выходную 8 шины.

В качестве источника 1 могут бо1ть использованы, например, два источника опорного напряжения противоположной полярности, управляемые знаковым разрядом с помощью аналогового переключателя. В качестве фильтра А можно применить фильтр с LC-контуром последовательного резонанса со сравнительно низкой добротностью.

Блок 6 представляет собой любую поразрядную сдвигаюцую входной код схему, например, выполненную как многоразрядный yльтипл;: кcop.

Кодоуправляемая матрица 2 можгг быть представлена на резисторах R - 2R с выходом по напряжению, а ЦЛП 3 с использованием матрицы 2R-4R с суммированием токов оперзционньп усилителем. Номиналы резисторов R-2R и 2R-4R тIoзnoля lT непосредственно соед1;51 , гь такяе матрицы, поскольку в этом случае выходное и входное соп- ротивлочия их согласованы и не происходит потерь сигналов и нарушения ТОЧНОСТ1 работы.

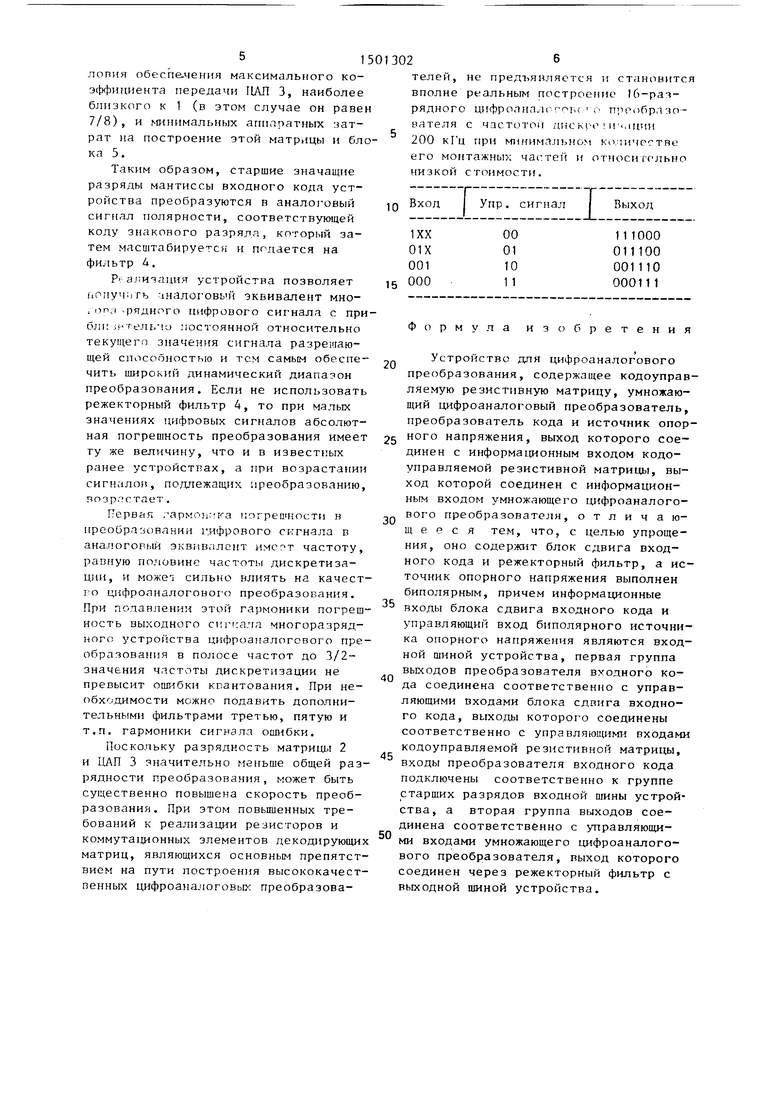

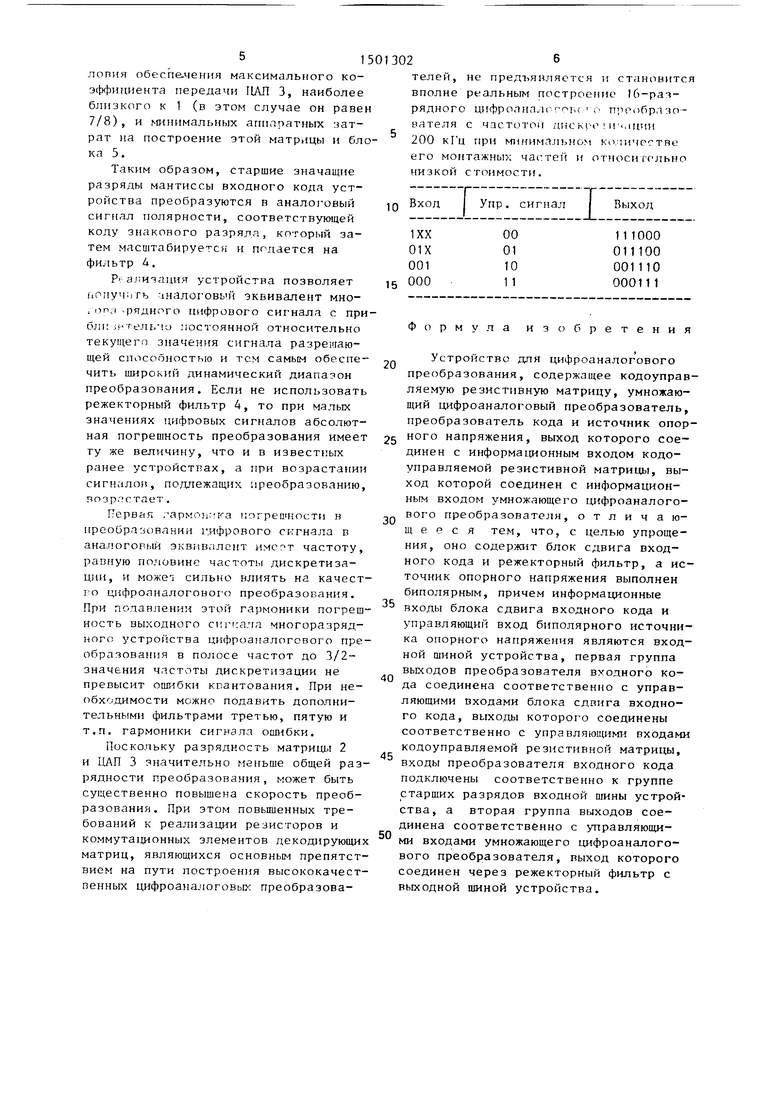

В качестве преобразователя 5 может быть применена комбинащюнцая схема (фиг. 2), таблица истинности которой Гм ивех сна ниже, знак X означает безразличное состоягше рачряда. Цифры на входах и выходах означают номер разряда, при . ем более старишй разряд имеет больший номер.

Преобразователь 5 может быть также реализован на постоянном запоминающем устройстве с той же таблицей истинности.

Представленные примеры рассчитаны на применение 16-разрядного yct-poii10

15

20

25

30

40

45

50

55

CTB. i, т, I . н случае, обычном для циф- рон1,1л чнукогилх пронг рывятелей, и 1 2-р,-гп1ПЛИ(1п матрицы 2, разрешающая способно.-П) KOTopoii, как и tlA 3, обе с ПС читается подгонк(;й резис 1 оро лазерным .чучом по тсхнсиьл ии, ной при ичготоБлении сериГшых цифро- аналоговых преобразователей.

ycTpoi fCTHO работает следу|01;(им образг)м.

Входным кодом устройства в рассматриваемом случае явпяется параллельный биполярный двоичный код с разрядом знака и ман 1 иссой в ирямг.м коде .

Знаковый разряд входного кода уст- ройстпа поступает на упрлв:1яю;Ц 11 вход источника 1, вь ;лю 11с го oiiop ri-.in аналоговый сигнал COOTI ei ствуы Я1 и полярности, который поступает на вхчд матриЩ) 2 с выходным ана.пся очым сиг-- HiuioMj, гоступаюишм на вход ЦЛП 3,

Старип е разряд,. мантис ы входного кода устрт1 стпа поступают на входи прегбразовятеля 5, который обегпе- чиплет сдвиг влево с помощью блока 6 части старших значап,нх разрядов мантиссы. Код : тих слнинутьгх влево CT ipuiiix разрядов ;peor-;i;i чуется ri jp- вом м.п рицеь 2, количесппо ко;;оиых 1;хпдоп KOTopoi i рапно KojunecTFiv рь - хидси б-и:ка 6. Для приведенного примера пеаличации устроГгс Г вл код :. е;11Я л разрядов мантиссы, к;)М- Kt Toporo 1федставл1 иы п грл-- ;е Вход таблицы, преоб11; 1зуется в коды перпьгх выходов преобразог .а гглп 5, которые приведены н графе Упр. сигнал 1;1блицы. В зависимости ог кодов первых выходов преобразователя 5 блок 6 с. Ишгает 12 разрядов (начиная со старших) 15-разрядной мантиссы на О, 1, 2 и 3 разряда влево. Преобразователь 5 в зависимости от состоянии старших разрядов ь антигс1 выдает также коды на свои:: вторых выходах, которые управляют коэффпп,п- ентом передачи ОДП 3.

Дп« приведенного примера реализации устройства в зависимости от состояния трех старших разрядов 15-т)ач- рядно мантиссы преобразователь 5 вырабатывает на своих вторых выходах, 6-рлзрядные коды, содержащие группы из трех 1. сдвигаемых вправо на О, 1, 2 1 3 разрядов п соотпегст- вии с графой Вьгход . Р)1:.1ход- пые коды содержат группы 111 из услопия обеспе-чения максимального ко- эс1)фициента передачи НАЛ 3, наиболее близкого к 1 (в этом случае он равен 7/8), и минимальных агнмпатных затрат на построение этой матрицы и блока 5.

Таким образом, старшие значащие разряды мантиссы входного кода устройства преобразуются в анало -овый сигнал полярности, соответствующей коду знакового разряда, который затем масштабируется и подается на фильтр 4.

PI а-г;изация устройства позволяет fiOiiyt jTb анадоговь й эквивалент мно- . i:in;j фядного цифрового сигнала с при- бли -тель и постоянной относительно текущего значения сигнала разрешающей способностью и тем самым обеспечить широкий динамический диапазон преобразования. Если не использовать режекторный фильтр 4, то при малых значениях цифровых сигналов абсолютная погрешность преобразования имеет ту же величину, что и в известных ранее устройствах, а цри возрастании сигналов, подлежащих преобразованию, возрлстает.

Первая гармо}1Г ка погрешности в преобразовании г.ифрового сигнала в аналоговый экв)валснт частоту, рапную половине частоты дискретизации, и может сильно влиять на качест- ро 1у1фроаналоговог о преобразования.

телеи, не предъявляется и становится вполне реальньм построение 16-разрядного цифроаHajiог ь; i о преобрлзо- вателя с частотои дискгч 200 кГ ц при минимальном количестве его монтажны : частеГ и относи 1чч7ьно низкой стоимости.

10

20

15

Формула изобретения

Устройство для цифроаналогового преобразования, содержащее кодоуправ- ляемую резистивную матрицу, умножающий цифроаналоговый преобразователь, преобразователь кода и источник опор- 25 ного напряжения, выход которого соединен с информационным входом кодо- управляемой резистивной матрицы, выход которой соединен с информационным входом умножающего гдифроаналого- вого преобразователя, о т л и ч а ю- щ е е с я тем, что, с целью упрощения, оно содержит блок сдвига входного кода и режекторный фильтр, а источник опорного напряжения выполнен биполярным, причем информационные

30

При подавлении этой гармоники погреш- входы блока сдвига входного кода и ность выходного сигсала многоразряд- управляющий вход биполярного источни- ного устройства цифроатгалогового преобразования в полосе частот до 3/240

значения частоты дискретизации не превысит ошибки квантования. При не- обхо,1химости можно подавить дополнительными фильтрами третью, пятую и т.п. гармоники сигнала оап-1бки.

Поскольку разрядность матрицы 2 и ЦАП 3 значительно меньше общей разрядности преобразования, может быть существенно повышена скорость преобразования. При этом повышенных требований к реализации резисторов и коммутадаонных элементов декодирующих матриц, являющихся основным препятствием на пути построения высококачественных цифроаналоговых преобразова45

50

ка опорного напряжения являются входной шиной устройства, первая группа выходов преобразователя входного кода соединена соответственно с управляющими Входами блока сдвига входного кода, выходы которого соединены соответственно с управляющими входами кодоуправляемой резистивной матрицы, входы преобразователя входного кода подключены соответственно к группе старших разрядов входной шины устройства, а вторая группа выходов соединена соответственно с управляющими входами умножающего цифроаналогового преобразователя, выход которого соединен через режекторный фильтр с выходной шиной устройства.

телеи, не предъявляется и становится вполне реальньм построение 16-разрядного цифроаHajiог ь; i о преобрлзо- вателя с частотои дискгч 200 кГ ц при минимальном количестве его монтажны : частеГ и относи 1чч7ьно низкой стоимости.

Формула изобретения

Устройство для цифроаналогового преобразования, содержащее кодоуправ- ляемую резистивную матрицу, умножающий цифроаналоговый преобразователь, преобразователь кода и источник опор- ного напряжения, выход которого соединен с информационным входом кодо- управляемой резистивной матрицы, выход которой соединен с информационным входом умножающего гдифроаналого- вого преобразователя, о т л и ч а ю- щ е е с я тем, что, с целью упрощения, оно содержит блок сдвига входного кода и режекторный фильтр, а источник опорного напряжения выполнен биполярным, причем информационные

входы блока сдвига входного кода и управляющий вход биполярного источни-

входы блока сдвига входного кода и управляющий вход биполярного источни-

40

45

50

ка опорного напряжения являются входной шиной устройства, первая группа выходов преобразователя входного кода соединена соответственно с управляющими Входами блока сдвига входного кода, выходы которого соединены соответственно с управляющими входами кодоуправляемой резистивной матрицы, входы преобразователя входного кода подключены соответственно к группе старших разрядов входной шины устройства, а вторая группа выходов соединена соответственно с управляющими входами умножающего цифроаналогового преобразователя, выход которого соединен через режекторный фильтр с выходной шиной устройства.

(риг.2

| Патент США № 3997892, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифроаналоговый преобразователь | 1981 |

|

SU1027811A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-08-15—Публикация

1986-08-22—Подача