ел

ел ч

со

315

Изобретение относится к г лектро- связи и может быть испо.пьгкшано в кп- налах связи информационно-вычислительных систем и сетей передачи данных .

Цель изобретения - повьпиение пропускной способности путем исключения возможности столкновения и наложения сигналов сообщений.

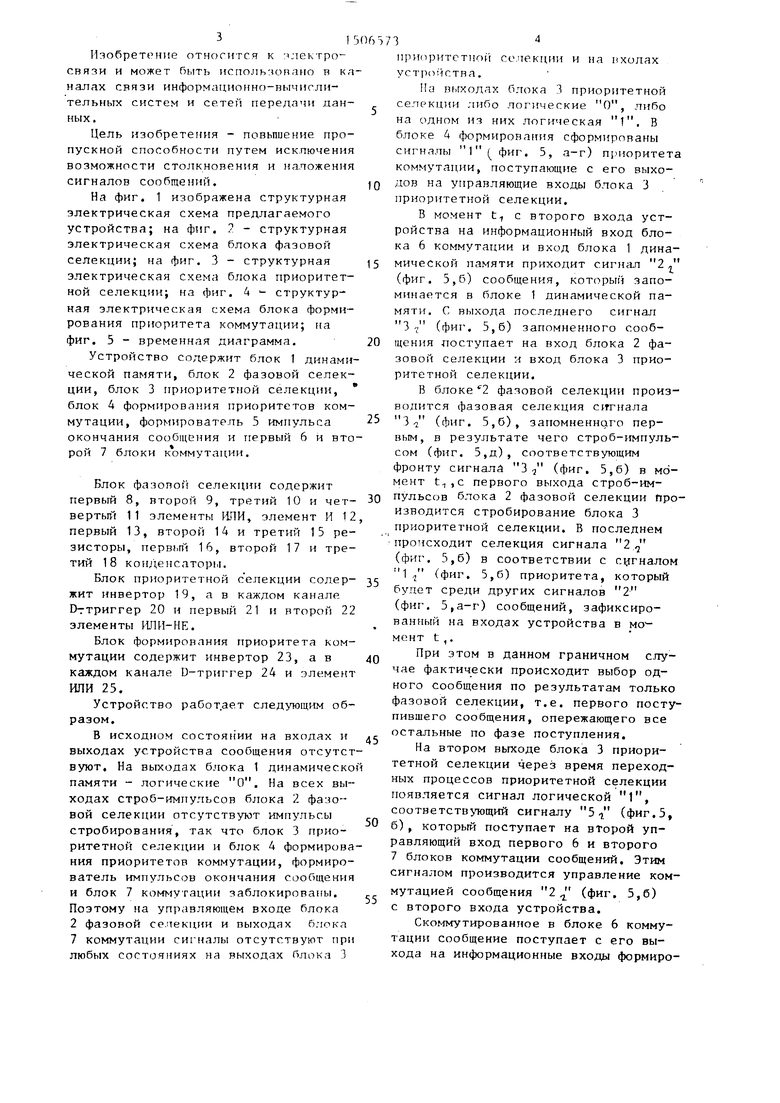

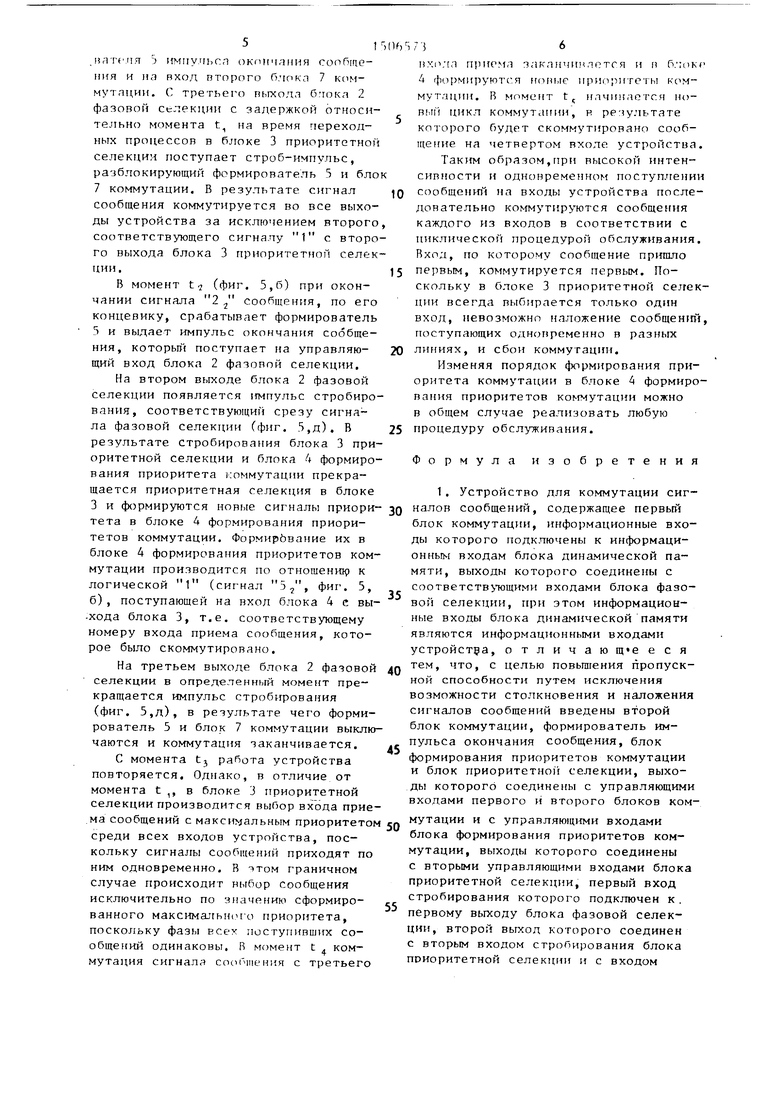

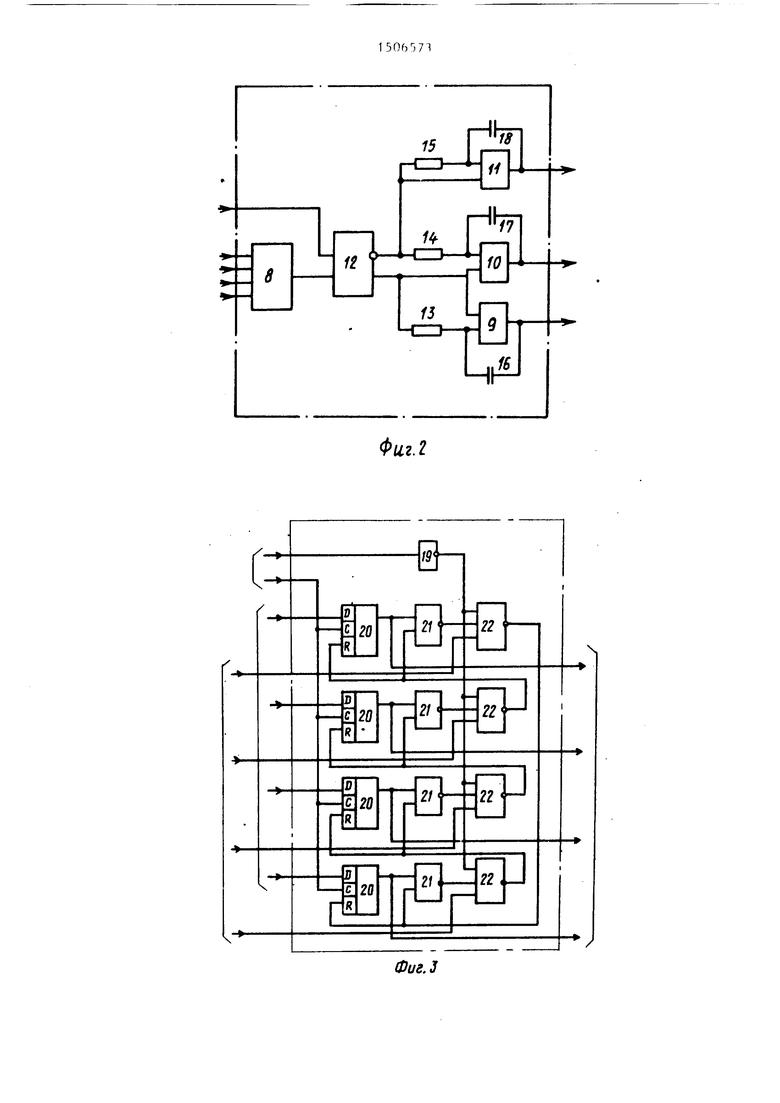

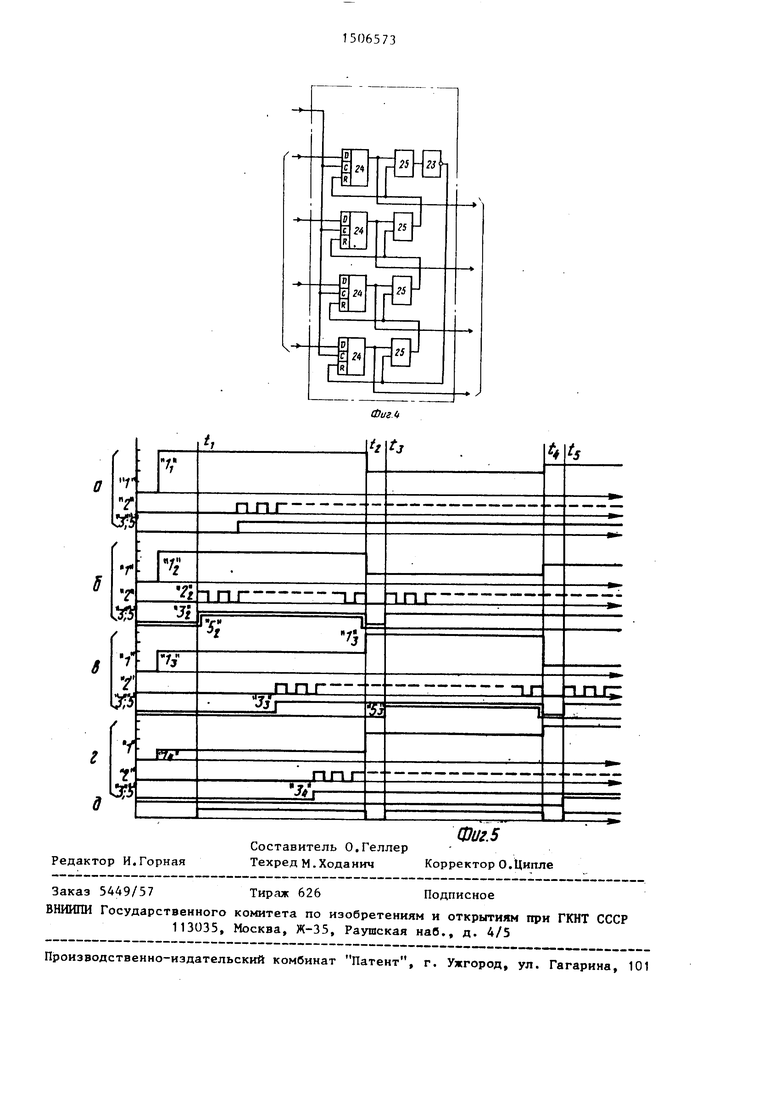

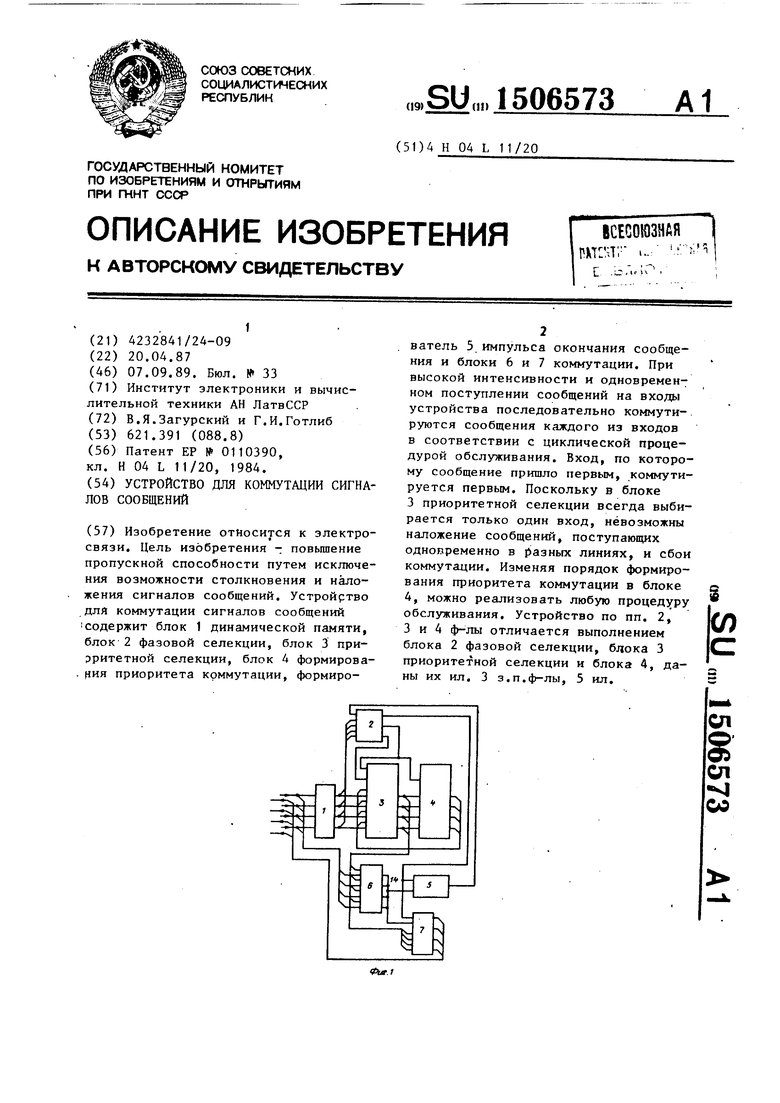

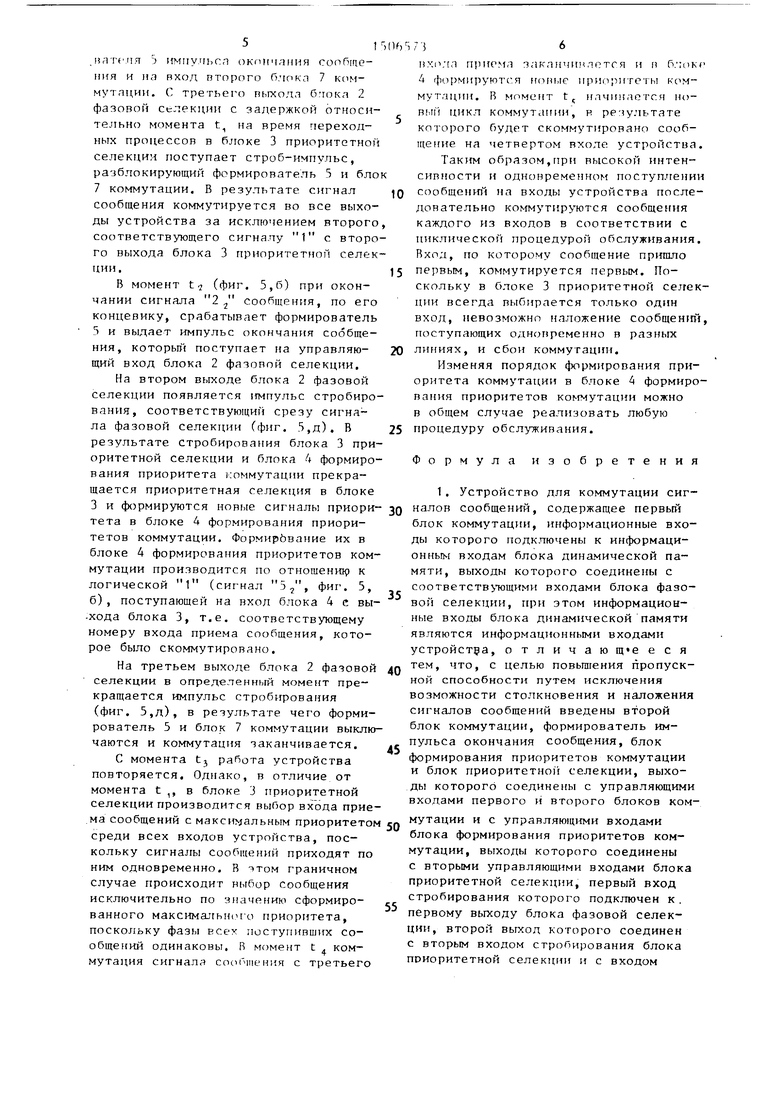

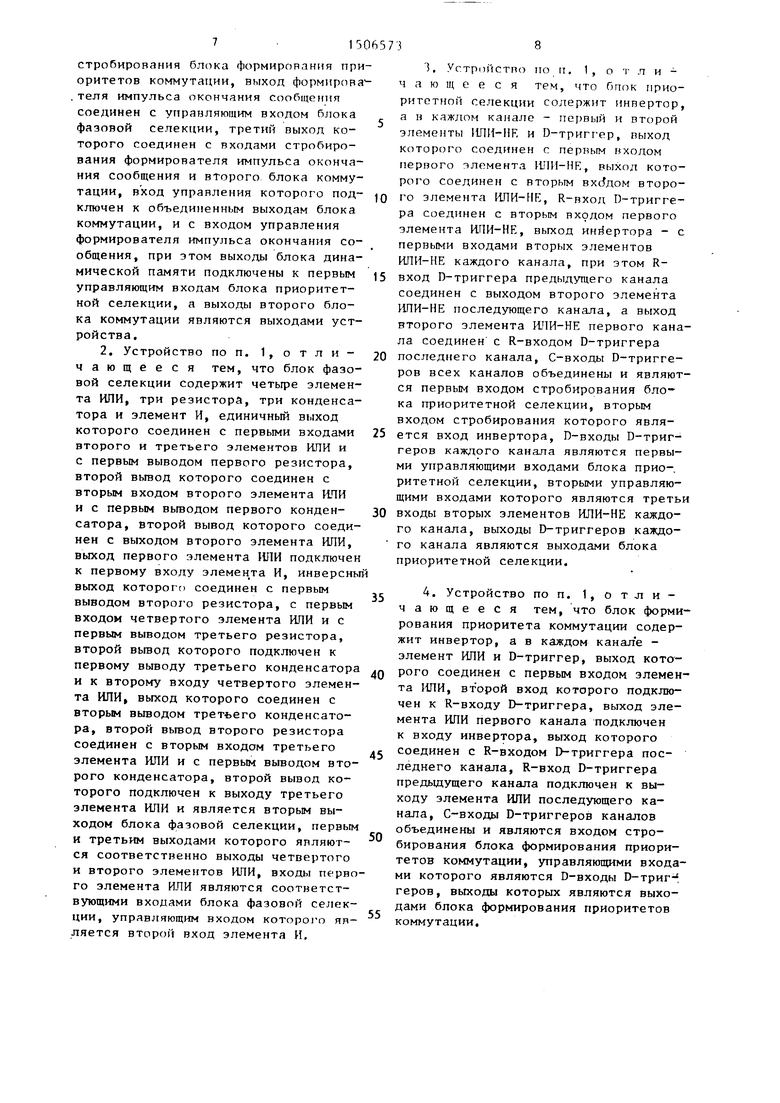

На фиг, 1 изображена структурная электрическая схема предлагаемого устройства; на фиг. 2 - структурная электрическая схема блока фазовой селекции; на фиг. 3 - структурная электрическая схема блока приоритетной селекции; на фиг. 4 структурная электрическая схема блока формирования приоритета коммутации; на фиг. 5 - временная диаграмма.

Устройство содержит блок 1 динамической памяти, блок 2 фазовой селекции, блок 3 приоритетной селекции, блок 4 формирования приоритетов коммутации, формирователь 5 импульса окончания сообщения и первый 6 и второй 7 блоки коммутации.

Блок фазопо селекции содержит первый 8, второй 9, третий 10 и чет- вертый 11 элементы Ш1И, элемент И 12 первый 13, второй 14 и третий 15 резисторы, nepBf.m 16, второй 17 и третий 18 кон/1,енсатор1.1.

Блок приоритетной с елекции содер- жит инвертор 19, а в каждом канале Вттриггер 20 и первый 21 и второй 22 элементы ИЛИ-НЕ.

Блок формирования приоритета коммутации содержит инвертор 23, а в каждом канале D-триггер 24 и элемент ИЛИ 25.

Устройство работ.ает следующим образом.

В исходном состоянии на входах и выходах устройства сообщения отсутствуют. На выходах блока 1 динамическо памяти - логические О. На всех выходах строб-импульсов блока 2 фазовой селекции отсутствуют импульсы стробирования, так что блок 3 приоритетной селекции и блок 4 формирования приоритетов коммутации, формирователь импульсов окончания сообщения и блок 7 коммутации заблокированы. Поэтому на управляющем входе блока 2 фазовой селекции и выходах б.чока 7 коммутации сигналы отсутствуют при любых состояниях на выходах блока 3

3

приоритетной селекции и на иходах устройства.

На выходах блока 3 приоритетной

на одном из них логическая Г

В

5 0

5

0

5

0

5 .

блоке 4 формирования сформированы сигналы 1 ( фиг. 5, а-г) прчюритета коммутации, поступающие с его выходов на управляющие входы блока 3 приоритетной селекции.

В момент t, с второго входа устройства на информационный вход блока 6 коммутации и вход блока 1 динамической памяти приходит сигнал 2 (фиг. 5,б) сообщения, который запоминается в блоке 1 динамической памяти, С выхода последнего сигнал 3-. (фиг. 5,6) запомненного сообщения поступает на вход блока 2 фазовой селекции и вход блока 3 приоритетной селекции.

В блоке 2 фазовой селекции производится фазовая селекция С1тгнала З-п (фиг. 5,6), запомненного первым, в результате чего строб-импульсом (фиг. 5,д), соответствующим фронту сигналй 3 (фиг. 5,6) в момент tT,c первого выхода строб-импульсов блока 2 фазовой селекции Производится стробирование блока 3 приоритетной селекции. В последнем ПРОТ1СХОДИТ селекция сигнала 2-2 (фиг. 5,6) в соответствии с сигналом 1 (фиг. 5,6) приоритета, который будет среди других сигналов 2 (фиг. 5,а-г) сообщений, зафиксированный на входах устройства в мо-- мент t,,

При этом в данном граничном случае фактически происходит выбор одного сообщения по результатам только фазовой селекции, т.е. первого поступившего сообщения, опережающего все остальные по фазе поступления.

На втором выходе блока 3 приоритетной селекции через время переходных процессов приоритетной селекции появляется сигнал логической 1, соответствующий сигналу 5, (фиг.5, б), который поступает на второй управляющий вход первого 6 и второго 7 блоков коммутации сообщений. Этим сигналом производится управление коммутацией сообщения (фиг. 5,6) с второго входа устройства.

Скоммутированное в блоке 6 коммутации Сообщение поступает с его выхода на информационные входы формиро51

Игчтсля 3 импу. гьсл «кпичания сопбщо- ния и на вход второго блока 7 коммутации. С третьего пьгходл бпокл 2 фазовой ce.ieKuiiH с задержкой относительно момента t на время переходных процессов в блоке 3 приоритетной селекции поступает строб-импульс, разблокирующий формирователь 5 и бло 7 коммутации. В результате сигнал сообщения коммутируется во все выходы устройства за исключением второго соответствующего сигналу 1 с второго выхода блока 3 приоритетной селекции.

В момент t (фиг. 5,6) при окончании сигнала сообщения, по его концевику, срабатывает формирователь 5 и выдает импульс окончания сообщения, которьш поступает на управляю- щий вход блока 2 фазовой селекции.

На втором выходе блока 2 фазовой селекции появляется импульс стробиро- вания, соответствующий срезу сигнала фазовой селекции (фиг. 5,д), В результате стробирования блока 3 приоритетной селекции и блока 4 формирования приоритета |;оммутации прекращается приоритетная селекция в блоке 3 и формируются HOBfiie сигналы приори- тета в блоке 4 формирования приоритетов коммутации. Формирование их в блоке А формирования приоритетов коммутации производится по отношении) к логической 1 (сигнал 5, фиг. 5, б), поступающей на вход блока 4 с вы- -хода блока 3, т.е. соответствующему номеру входа приема сообщения, которое было скоммутировано.

На третьем выходе блока 2 фазовой селекции в определенный момент прекращается импульс стробирования (фиг. 5,д), в результате чего формирователь 5 и блок 7 коммутации выключаются и коммутация заканчивается.

С момента tj работа устройства повторяется. Однако, в отличие от момента t ,, в блоке 3 приоритетной селекции производится выбор входа приема сообщений с максимальным приоритетом среди всех входов устройства, поскольку сигналы Сообщений приходят по ним одновременно. В граничном случае происходит выбор сообщения

исключительно по значению сформированного максимальнсЧ о приоритета, поскольку фазы всех поступивших сообщений одинаковы, R момент t коммутация сигнала соси чиения с третьего

Q 5

20

25 jg

40 .с

Q

5

5

736

iiX(i;in пlИIe ы заклнчиилотся и л 6. :i)Kf 4 ф11рмируются iKiffbie 1гриоритеты коммутации. В момент t начинается но- цикл коммутации, в результате которого будет скоммутировано сообщение на четвертом входе устройства.

Таким образом,при высокой интенсивности и одновременном поступлении сообщенш1 на входы устройства последовательно коммутируются сообщения каждого из входов в соответствии с циклической процедурой обслуживания. Вход, по которому сообщение пришло первым, коммутируется первым. Поскольку в блоке 3 приоритетной селек- Ц1п всегда выбирается только один вход, невозможно наложение сообщен1ш, поступающих однонременно в разных линиях, и сбои коммутации.

Изменяя порядок формирования приоритета коммутации в блоке 4 формирования приоритетов коммутации можно в общем случае реализовать любую процедуру обслуживания.

Формула изобретения

1. Устройство для коммутации сигналов сообщений, содержащее первый блок коммутации, информационные входы которого подключены к информаци- онньп-г входам блока динамической памяти, выходы которого соединены с соответствующими входами блока фазовой селекции, при этом информационные входы блока динамической памяти являются информационными входами устройства, отличаю щ«е е с я тем, что, с целью повьшения пропускной способности путем исключения возможности столкновения и наложения сигналов сообщений введены второй блок коммутации, формирователь импульса окончания сообщения, блок формирования приоритетов коммутации и блок приоритетно селекции, выходы которого соединены с управляющими входами первого и второго блоков коммутации и с управляющими входами блока формирования приоритетов коммутации, выходы которого соединены с вторыми управляющими входами блока приоритетной селекции, первый вход стробирования которого подключен к. первому выходу блока фазовой селекции, второй выход которого соединен с вторым входом стробирования блока приоритетной селекции и с входом

стробирования блсжа формирования приоритетов кo fмyтaции, выход формирова теля импульса окончания сообщения соединен с управляющим входом блока фазовой селекции, третий выход которого соединен с входами стробирования формирователя импульса окончания сообщения и второго блока коммутации, вход управления которого под- ключен к объединенным выходам блока коммутации, и с входом управления формирователя импульса окончания сообщения, при этом выходы блока динамической памяти подключены к первым управляющим входам блока приоритетной селекции, а выходы второго блока коммутации являются выходами устройства.

2. Устройство по п. 1, о т л и - чающееся тем, что блок фазовой селекции содержит четьфе элемента ИЛИ, три резистора, три конденсатора и элемент И, единичный выход которого соединен с первыми входами второго и третьего элементов ИЛИ и С первым выводом первого резистора, второй вьгаод которого соединен с вторым входом второго элемента ИЛИ и с первым вьтодом первого конден- сатора, второй вывод которого соединен с выходом второго элемента ИЛИ, выход первого элемента ИЛИ подключен к первому входу элемента И, инверснь выход которого соединен с первым выводом второго резистора, с первым входом четвертого элемента ИЛИ и с первым выводом третьего резистора, второй вьгеод которого подключен к первому вьтоду третьего конденсатора и к второму входу четвертого элемента ИЛИ, выход которого соединен с вторым выводом третьего конденсатора, второй вьтод второго резистора соединен с вторым входом третьего элемента ИЛИ и с первым выводом второго конденсатора, второй вывод которого подключен к выходу третьего элемента ИЛИ и является вторым выходом блока фазовой селекции, первым и третьим выходами которого являют- ся соответственно выходы четвертого и второго элементов ИЛИ, входы первого элемента ИЛИ являются соответствующими входами блока фазовой селекции, управляющим входом которого является второй вход элемента И,

5

0 5 О

5

5

1, УсТрОЙСТПО по ГТ. 1, о л и чающееся тем, что Опок приоритетной селекции содержит инвертор, а н каждом канале - первый и второй элементы 1ШИ-НЕ и D-триггер, выход которого соединен с первым входом первого элемента ИЛИ-НЕ, выход которого соединен с вторым вxdдoм второго элемента ИЛИ-МЕ, R-вход П-тригге- ра соединен с вторым входом первого элемента ИЛИ-НЕ, вьпсод инйертора - с первыми входами вторых элементов ИЛИ-НЕ каждого канала, при этом R- вход D-триггера предыдущего канала соединен с выходом второго элемента ИЛИ-НЕ последующего канала, а выход второго элемента ИЛИ-НЕ первого канала соединен с R-входом D-триггера последнего канала, С-входы D-тригге- ров всех каналов объединены и являются первым входом стробирования блока приоритетной селекции, вторым входом стробирования которого является вход инвертора, D-входы D-триг- геров каждого канала являются первыми управляющими входами блока прио-. ритетной селекции, вторьми управляющими входами которого являются третьи входы вторых элементов ИЛИ-НЕ каждого канала, выходы D-триггеров каждого канала являются выходами блока приоритетной селекции.

4. Устройство по п. 1, о т л и - чающееся тем, что блок формирования приоритета коммутации содержит инвертор, а в каждом канал е - элемент ИЛИ и D-триггер, выход которого соединен с первым входом элемента 1ШИ, вт орой вход которого подключен к R-входу D-триггера, выход элемента ИЛИ первого канала подключен к входу инвертора, выход которого соединен с R-входом D-триггера последнего канала, R-вход D-триггера предыдущего канала подключен к выходу элемента ИЛИ последующего канала, С-входы D-триггеров каналов объединены и являются входом стробирования блока формирования приоритетов коммутации, управляющими входами которого являются D-входы D-триг- геров, выходы которых являются выходами блока формирования приоритетов коммутации.

15 rCZh

Hf

18

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коммутации сигналов сообщений | 1988 |

|

SU1640832A2 |

| УСТРОЙСТВО КОММУТАЦИИ КАДРОВ | 1991 |

|

RU2048707C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2000 |

|

RU2179787C1 |

| Устройство для сопряжения цифровой вычис-лиТЕльНОй МАшиНы C КАНАлАМи СВязи | 1979 |

|

SU840876A1 |

| Многоканальное устройство для управления коммутацией сообщений | 1981 |

|

SU1012304A1 |

| Устройство для сопряжения процессоров в вычислительной системе | 1985 |

|

SU1332327A1 |

| Многоканальный коммутатор | 1981 |

|

SU963046A1 |

| Многоканальное устройство для обмена данными между модулями вычислительной системы | 1985 |

|

SU1256037A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ПАКЕТНОЙ ИНФОРМАЦИИ ПО РАДИОКАНАЛУ | 1999 |

|

RU2168282C1 |

| Устройство для связи процессоров в вычислительной системе | 1988 |

|

SU1515170A1 |

Изобретение относится к электросвязи. Цель изобретения - повышение пропускной способности путем исключения возможности столкновения и наложения сигналов сообщений. Устройство для коммутации сигналов сообщений содержит блок 1 динамический памяти, блок 2 фазовой селекции, блок 3 приоритетной селекции, блок 4 формирования приоритета коммутации, формирователь 5 импульса окончания сообщения и блоки 6 и 7 коммутации. При высокой интенсивности и одновременном поступлении сообщений на входы устройства последовательно коммутируются сообщения каждого из входов в соответствии с циклической процедурой обслуживания. Вход, по которому сообщение пришло первым, коммутируется первым. Поскольку в блоке 3 приоритетной селекции всегда выбирается только один вход, невозможны наложение сообщений, поступающих одновременно в разных линиях, и сбои коммутации. Изменяя порядок формирования приоритета коммутации в блоке 4, можно реализовать любую процедуру обслуживания. Устройство по пп. 2, 3 и 4 ф-лы отличается выполнением блока 2 фазовой селекции, блока 3 приоритетной селекции и блока 4, даны их ил. 3 з.п. ф-лы, 5 ил.

8

И

Н

17

15

Фиг.2

Фиг.З

| Вибрационная установка с переменными дебалансами | 1956 |

|

SU110390A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-09-07—Публикация

1987-04-20—Подача