ел

сл

о

00

Изобретение относится к технике телевидения и может быть использовано для кодирования телевизионного сигнала.

Цель изобретения - уменьшение избыточной информации.

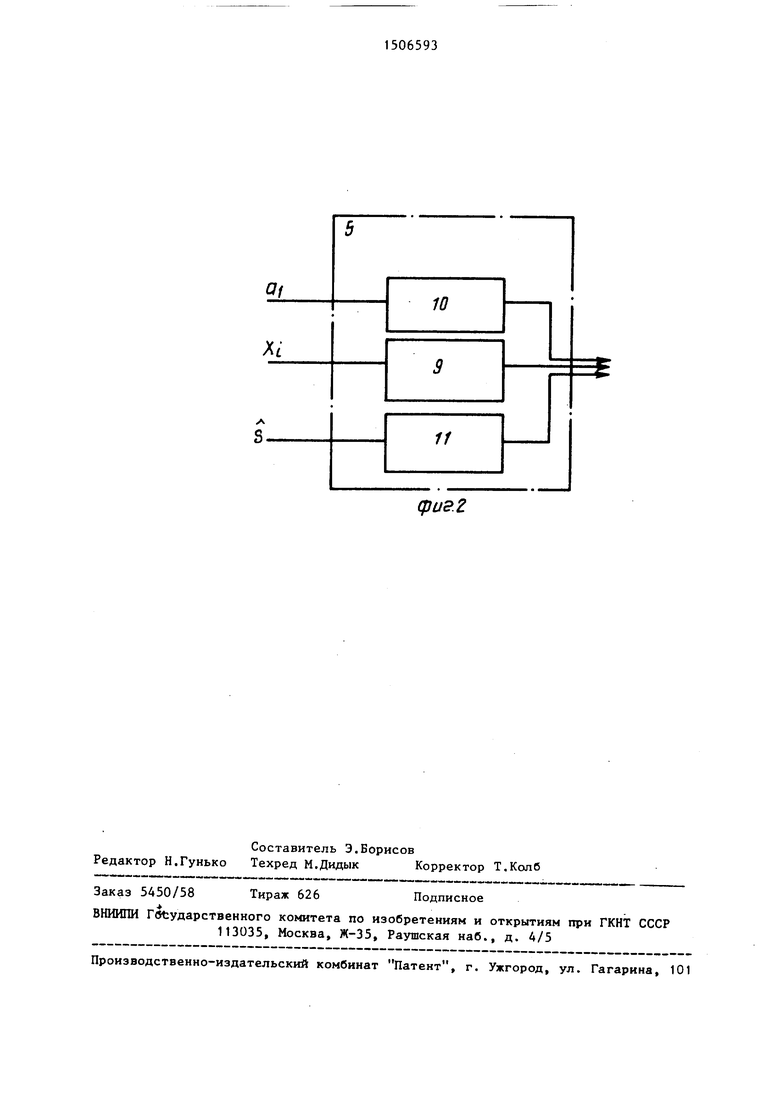

На фиг. 1 представлена электрическая структурная схема кодирующего устройства телевизионного сигнала; на фиг. 2 - блок кодирования.

Кодирующее устройство телевизионного сигнала (фиг. 1) содержит аналого-цифровой преобразователь (ЛЦП) 1, блок 2 памяти, умножитель 3, сумматор 4, блок 5 кодирования, коммутатор 6, блок 7 сравнения кодов, преобразователь 8 кодов.

Блок 5 кодирования (фиг. 2) содержит преобразователи 9 и 10 кодов, блок 11 задержки.

Кодирующее устройство телевизионного сигнала работает следующим образом.

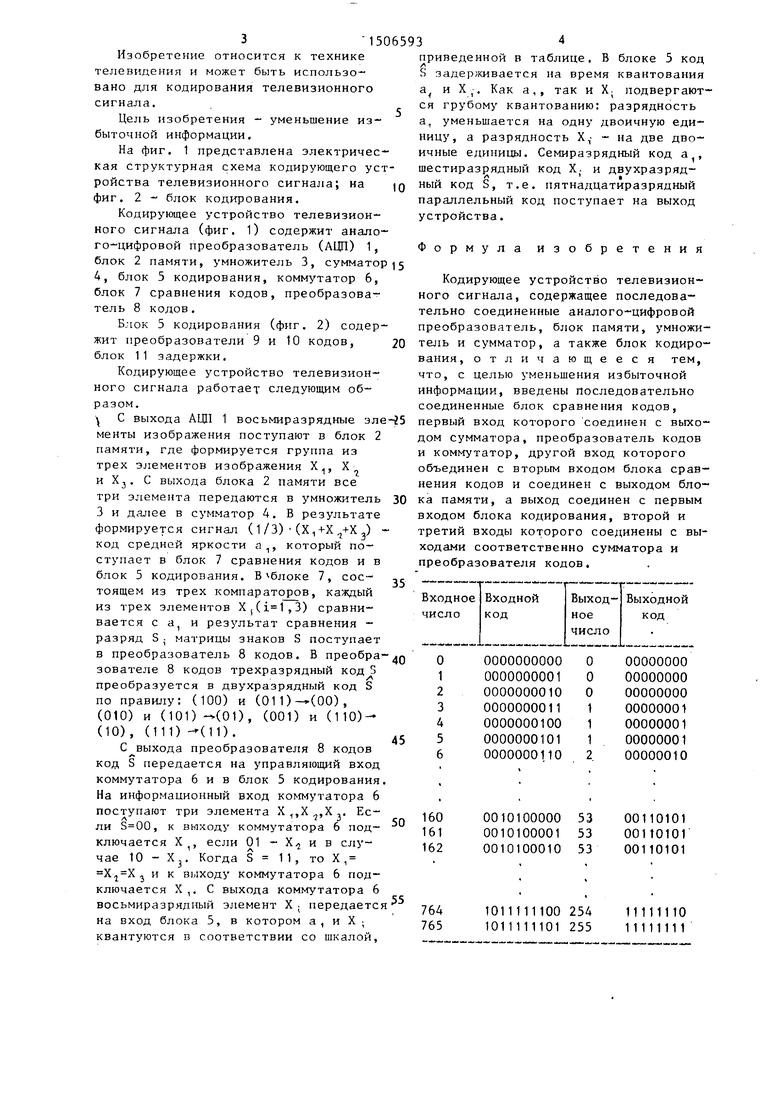

приведенной в таблице. В блоке 5 код S задерживается на время квантования а и Х|. Как а,, так и Х; подвергаются грубому квантованию; разрядность а, уменьшается на одну двоичную единицу, а разрядность X,- - на две двоичные единицы. Семиразрядный код а, шестиразрядный код X; и двухразрядный код S, т.е. пятнадцатиразрядный параллельный код поступает на выход устройства.

Формула изобретения

Кодирующее устройство телевизионного сигнала, содержащее последовательно соединенные аналого-цифровой преобразователь, блок памяти, умножитель и сумматор, а также блок кодирования, отличающееся тем, что, с целью уменьшения избыточной информации, введены последовательно соединенные блок сравнения кодов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодер сигнала изображения | 1989 |

|

SU1644389A1 |

| Кодер телевизионного сигнала | 1990 |

|

SU1753596A2 |

| Устройство для кодирования и декодирования телевизионного сигнала | 1988 |

|

SU1649674A1 |

| Кодер телевизионного сигнала | 1988 |

|

SU1569990A1 |

| Кодер сигнала изображения | 1988 |

|

SU1518922A1 |

| Дифференциальный импульсный кодер телевизионного сигнала | 1986 |

|

SU1424125A1 |

| Устройство передачи и приема цифрового телевизионного сигнала | 1987 |

|

SU1506592A2 |

| Дифференциальный импульсный кодер телевизионного сигнала | 1987 |

|

SU1481900A2 |

| Кодер видеосигнала | 1987 |

|

SU1506554A1 |

| Дифференциальный импульсный кодер телевизионного сигнала | 1986 |

|

SU1358111A2 |

Изобретение относится к технике телевидения. Цель изобретения - уменьшение избыточной информации. Устройство содержит АЦП 1, блок 2 памяти, умножитель 3, сумматор 4, блок 5 кодирования. Цель достигается введением в устройство коммутатора 6, блока 7 сравнения кодов и преобразователя 8 кодов. В блоке 7, состоящем из трех компараторов, каждый из трех элементов изображения XI сравнивается с кодом средней яркости A1 и результат сравнения - разряд SI матрицы знаков S поступает в преобразователь 8. В преобразователе 8 трехразрядный код S преобразуется в двухразрядный код S по правилу: (100) и (011) → (00), (010) и (101) → (01), (001) и (110) → (10), (111) → (11). С выхода преобразователя 8 код S передается на управляющий вход коммутатора 6 и в блок 5. В блоке 5 код задерживается на время квантования A1 и XI. Как A1, так и XI подвергаются грубому квантованию: разрядность A1 уменьшается на одну двоичную единицу, а разрядность XI - на две двоичные единицы. 2 ил., 1 табл.

у С выхода АЩ1 1 восьмиразрядные первый вход которого соединен с выхо30

35

менты изображения поступают в блок 2 памяти, где формируется группа из трех элементов изображения Х, X и Xj. С выхода блока 2 памяти все три элемента передаются в умножитель 3 и далее в сумматор 4. В результате формируется сигнал (1/3)( - код средней яркости а,, который поступает в блок 7 сравнения кодов и в блок 5 кодирования. В блоке 7, состоящем из трех компараторов, каждый из трех элементов Х,(,3) сравнивается с а и результат сравнения - разряд S ; матрицы знаков S поступает в преобразователь 8 кодов. В преобра- Q

зователе 8 кодов трехразрядный код S

преобразуется в двухразрядный код S

по правилу: (100) и (011)-(00), (010) и (101)-(01), (001) и (110)- (10), (111) - (И).

С выхода преобразователя 8 кодов код § передается на управляющий вход коммутатора бив блок 5 кодирования На информационный вход коммутатора 6 поступают три элемента Х,Х,,,Х2. Если , к выходу ког-{мутатора 6 подключается Х, если 01 - Х и в слудом сумматора, преобразователь кодов и коммутатор, другой вход которого объединен с вторым входом блока сравнения кодов и соединен с выходом блока памяти, а выход соединен с первым входом блока кодирования, второй и третий входы которого соединены с выходами соответственно сумматора и преобразователя кодов.

45

50

160 161 162

чае 10 - Xj. Когда S 11, то Х, J и к выходу коммутатора 6 подключается X,. С выхода коммутатора 6 восьмиразрядный элемент Xj передается на вход блока 5, в котором а, и X ; у квантуются в соответствии со шкалой,

0010100000 0010100001 0010100010

53 53 53

1011111100254

1011111101255

00110101

001 toior

00110101

11111110 11111111

дом сумматора, преобразователь кодов и коммутатор, другой вход которого объединен с вторым входом блока сравнения кодов и соединен с выходом блока памяти, а выход соединен с первым входом блока кодирования, второй и третий входы которого соединены с выходами соответственно сумматора и преобразователя кодов.

35

Q

45

160 161 162

у

0010100000 0010100001 0010100010

53 53 53

00110101

001 toior

00110101

1011111100254

1011111101255

11111110 11111111

а/

)(L

/

S.

10

//

(риг. г

| Дифференциальный импульсный кодер телевизионного сигнала | 1986 |

|

SU1358111A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-09-07—Публикация

1987-04-06—Подача