Изобретение относится к вычислительной технике и предназначено для использования в асинхронных вычисли- -тельных системах, в которых осуществляется независимый доступ к общей многосекционной памяти от источников и приемников информации.

Цель изобретения - повышение быстродействия устройства.

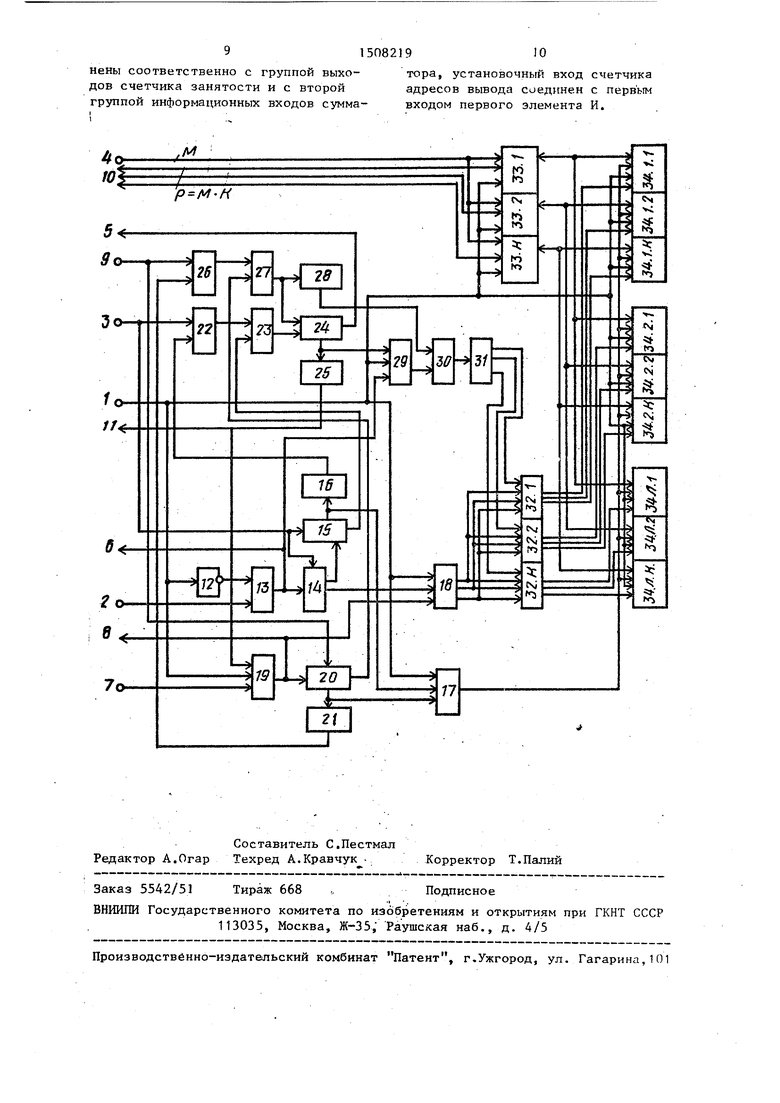

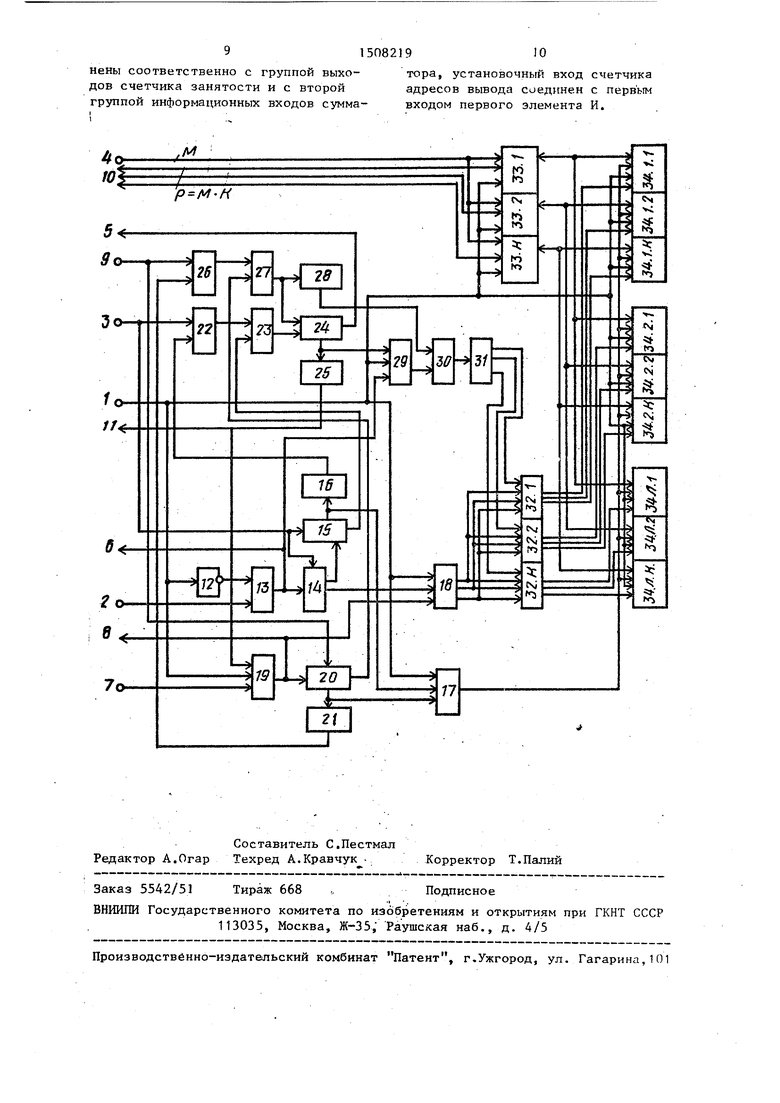

На чертеже представлена функциональная схема устройства.

Устройство содержит (фиг.1) вход 1, тактовый вход 2 признака ввода, , вход 3 признака конца ввода, М-раз- рядный информационный вход 4, где М - разрядность вводимых данных,, выход 5 разрешения ввода, выход 6 разрешения установки признака ввода, вход 7 признака вывода, выход 8 разрешения установки признака вывода, вход 9 признака конца вывода, Р-разрядный информационный выход 10, Р , К 2, И 0,1,2..., где Р - разрядность выводимых данных, выход 11 разрешения вывода, элемент НЕ 12, второй триггер 13, кольцевой сдвиговый регистр 14, счетчик 15 адресов ввода, пятый элемент ИЛИ 1-6, коммутатор 17 адресов, коммутатор 18 выбора блока памяти, первый триггер 19, счетчик 20 адресов вывода, второй элемент ИЛИ 2, второй элемент И 22, четвертый элемент ИЛИ 23, счет-- чик 24.занятости, первый элемент ИЛИ 25, первый элемент И 26, третий элемент ИЛИ 27, счетчик 28 выбора блока памяти, вторую.группу элементов И 29, сумматор 30, шифратор 31, первую группу из Л элементов И 32, коммутатор 33 данных и Л блоков 34 памяти, каждый из которых содержит К узлов памяти.

315

Устройство работает следующим образом..В начальный момент производится установка триггеров 13 и 19, счетчиков 15, 20, 24 и 28 в нулевое состоя кие, кольцевого сдвигового регистра 14 в состояние единичного потенциала на первом выходе и нулевого во всех остальных К-1 выходах (цепи установк на схеме не указаны). При этом .на выходах 5, 6 и 8 устройства формируются нулевыЬ уровни, разрешающие обращение к устройству. Установка счетчиков 24 и 28 в нулевое состояни приводит к подаче на выходы сумматора 30 нулевых кодов, при этом на нулевом выходе шифратора 31, преобг- разующего двоичный код-в унитарный, формируется единичный сигнал, кото- рый устанавливает режим записи в пер вом блоке 34.1 памяти во время дей-

ствия положительных импульсов на

1 входе 1 устройства.

Ввод информации в устройство про- изводится М-разрядными словами, а вывод информации - Р-разрядными словами, - причем Р МхК, где К 2, Н О,1,2,... Управление, процессами ввода и вывода Осуществляется такто- вой частотой по входу , при 1 - ввод, при О - вывод.

При наличии свободных блоков 34 памяти (на выходе 5 устройства - нулевой потенциал) на информационном йходе 4 устанавливается входная информация, а на вход -2. подается стро бирующий отрицательный сигнал, длительность которого равна циклу записи данных в блок 34 памяти. В момент действия стробирующего сигнала признака ввода на входе 2 производится .установка триггера 13 в единичное состояние. При этом на выходе 6 устройства формируется единичный сиг- нал, запрещающий смену входной информации и установку следующего строб-сигнала признака ввода. Если строб-сигнал признака ввода формируется в начале или середине единичног импульса записи на входе или во вре мя действия импульсов -чтения (нулевой сигнал) на входе 1, то установка триггера 13 в нулевое состояние осуществляется ближайщин отрицательным .фронтом тактового импульса, При этом ка выходе 6 разрешения установки признака вьгеода формируется нулевой потенциал, разрешакнций изменение ин9. 4

формации на входе 4 и установку следующего стробирующЬго импульса на входе 3, а задним фронтом единичного сигнала с выхода триггера 13 производится сдвиг в кольцевом сдвиговом регистре 14, задающем узел (34.1.1 - 34,1.К) памяти, в который будет вводиться информация по данному адресу первого блока 34 памяти. Если строб-сигнал признака ввода формируется во время отрицательного перепада на тактовом входе, то установка триггера 13 в нулевое состояние осз ществляется отрицательным фронтом тактового импульса, следующего после окончания строб-сигнала признака ввода.

Время действия сигнала на входах разрешения блоков 34, памяти определяется длительностью импульсов на входе 1 устройства и на выходе триггера 3 и в любом случае не может быть меньше длительности сигналов признака ввода, определяющих длительность цикла записи.

Количество разрядов кольцевого сдвигового регистра 14 равно К, при этом единичный сигнал в каждый момент времени может быть сформирован только на одном выходе, поэтому во время положительных импульсов на входе 1 устройства сигнал разрешения может быть подан только на один из К узлов 34.1.1-34,1.К памяти первого блока 34 памяти. Каждый блок 34 памяти содержит.К узлов памяти разрядностью М каждьй, запись инфермации в узлы 34.1,1-34.1,К во время цикла ввода производится через коммутаторы 33.1- 33 К данных поочередно по сигналам разрешения с выхода коммутатора. 18. При записи информации по данному адресу в .узел 34,1.К на К-выходе кольцевого сдвигового регистра 14 формируется единичный сигнал, задним фронтом которого увеличивается на единицу содержимое счетчика 15 адресов ввода.таким образом следующее М-разрядное слово будет записано в узел 34.1,1 первого блока 34 памяти, но по следующему адресу,

В момент -окончания цикла записи массива в первый блок 34 памяти на входе 3 формируется сигнал признака конца ввода, который увеличивает содержимое счетчика 24 занятости на единицу. Это приводит к тому, что следующий массив данных в циклах

ввода будет записываться во второй - блок 34 памяти, так как единичный сигнал в циклах ввода будет формироваться на втором выходе шифратора 31,

Если длина записываемого массива - больше емкости одного блока Зf памяти, то в момент заполнения емкости одного блока 34 памяти на выходе переполэом, все К узлов 34 выбранного блока памяти одновременно считывают информацию на выход 10 устройства. При этом данные стробируются сигналом с входа 7 устройства. Задним фронтом сигнала с триггера 19 содержимое, счетчика 20, задающего адрес ячейки вывода блока 34 памяти, изменяется

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сопряжения | 1987 |

|

SU1425691A1 |

| Устройство для сопряжения N абонентов с М ЭВМ | 1988 |

|

SU1564635A1 |

| Устройство для ввода - вывода информации | 1989 |

|

SU1672430A1 |

| Устройство для ввода-вывода информации | 1988 |

|

SU1536366A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1456963A1 |

| Устройство для сопряжения вычислительной машины с магистралью обмена | 1986 |

|

SU1381519A1 |

| Устройство для сопряжения ЭВМ с внешним абонентом | 1988 |

|

SU1594553A1 |

| Устройство для сопряжения абонентов с ЭВМ | 1986 |

|

SU1410041A1 |

| Устройство для сопряжения двух электронных вычислительных машин (ЭВМ) | 1983 |

|

SU1265781A1 |

Изобретение относится к вычислительной технике и предназначено для использования в асинхронных вычислительных системах, в которых осуществляется независимый доступ к общей многосекционной памяти от источников и приемников информации. Целью изобретения является повышение быстродействия. Устройство содержит группу блоков памяти, коммутатор данных, коммутатор адресов, коммутатор выбора блока памяти, шифратор, сумматор, счетчик выбора блока памяти, счетчик занятости, счетчик адресов ввода, счетчик адресов вывода, два триггера, две группы элементов И, два элемента И, пять элементов ИЛИ, элемент НЕ. 1 ил.

нения счетчика 15 формируется сигнал,Q на единицу. Наличии единичного сигкоторый через элемент ИЛИ 23 поступает иа вход счетчика 24 и увеличивает его содержимое на единицу, В случае равенства длины записываемого массива и емкости блока 34 памяти с целью исключения двойного срабатывания счетчика 24 введена блокировка входа 3 за счет формирования нулевого сигнала на выходе элемента ШШ 16, поступающего на второй вход элемента И 22, Занятие хотя бы одного блока 34 памяти массивом данных характеризуется наличием единичного сигнала на выходе 11 и указывает на необходимость вывода данных из занятого блока 34 памяти.

Процесс вывода данных осуществляется следующим образом.

Во время цикла вывода (нулевой сигнал на входе l) выходы данных вСех К узлов 34 данного блока памяти через коммутаторы 33,1-33,К данных подключаются к выходу 10 устройства. Выходы элемента И 29 заблокированы, поэтому номер блока 34 памяти определяется кодом счетчика 28, После записи массива данных в первый блок 34 памяти на входы шифратора 31 в циклах вывода будет поступать нулевой код, т,е. вывод будет осуществляться из Первого блока 34 памяти, В момент поступления сигнала на вход 7 ос-уществляется установка триггера 19 в единичное состояние. Если признак вывода с входа 7 устройства поступает в середине цикла ( или ввода), то сброс триггера 19 осуществляется задним фронтом сигнала вывода, если признак вывода поступает в момент изменения режима, то сброс триггера 19 осуществляется задним фронтом сигнала по входу 1, следующего после окончания сигнала на входе 7 устройства.

Импульс с выхода триггера 19 поступает на К первых входов коммутатора 18 и во время цикла вывода на все К входы выборки блоков 34 памяти подается сигнал разрешения, таким обранала на выходе 8 служит запретом установки следующего сигнала признака вывода на входе 7,

В момент окончания вывода данных

t5 из данного блока 34 памяти на вход 9 поступает сигнал, увеличивающий содержимое счетчика 28 и уменьшающий содержимое счетчика 24 на единицу. Это означает, что чтение следующего

20 массива будет осуществляться из следующего блока 34 памяти. Если длина выводимого массива больше емкости одного блока 34, то в момент переполнения емкости счетчика 20 на вы25 ходе переполнения данного счетчика формируется сигнал, который изменяет содержимое счетчиков 24 и 28, Если все блоки 34 памяти будут заняты, то на выходе переполнения счетчика 24

3Q (выход 5 устройства) сформируется сигнал, которь Й запретит ввод очередного массива данных, .пока не осво бодится хотя бы один блок 34 памяти. Емкость счетчика 28 равна числу блоков 34 памяти. После чтения массива данных из последнего блока 34.А осуществляется обнуление счетчика.28 т,е, чтение следующего массива данных будет осуществляться из первого блока 34,1 памяти.

35

40

Сумматор 30 выполняется следующим образом. Если число блоков 34 памяти

Н

45

50

55

кратно Z, где Н l,ii,J,,,j то cytматор 30 является сумматором по модулю два, В общем случае модуль суммирования определяется числом бло ков 34 памяти. Например, для десяти блоков 34 памяти сумматор 30 является десятичным сут-шатором.

Формула изобретения

Устройство для управления обменом информацией, содержап;ее группу блоков памяти, коммутатор данных, сумматор, шифратор, счетчик выбора блока памяти, счетчик занятости, счетчи адресов ввода, счетчик адресов вына единицу. Наличии единичного сигнала на выходе 8 служит запретом установки следующего сигнала признака вывода на входе 7,

В момент окончания вывода данных

из данного блока 34 памяти на вход 9 поступает сигнал, увеличивающий содержимое счетчика 28 и уменьшающий содержимое счетчика 24 на единицу. Это означает, что чтение следующего

массива будет осуществляться из следующего блока 34 памяти. Если длина выводимого массива больше емкости одного блока 34, то в момент переполнения емкости счетчика 20 на выходе переполнения данного счетчика ормируется сигнал, который изменяет содержимое счетчиков 24 и 28, Если все блоки 34 памяти будут заняты, то на выходе переполнения счетчика 24

(выход 5 устройства) сформируется сигнал, которь Й запретит ввод очередного массива данных, .пока не освободится хотя бы один блок 34 памяти. Емкость счетчика 28 равна числу блоков 34 памяти. После чтения массива данных из последнего блока 34.А осуществляется обнуление счетчика.28, т,е, чтение следующего массива данных будет осуществляться из первого блока 34,1 памяти.

Сумматор 30 выполняется следующим образом. Если число блоков 34 памяти

Н

5

0

5

кратно Z, где Н l,ii,J,,,j то cyti- матор 30 является сумматором по модулю два, В общем случае модуль суммирования определяется числом блоков 34 памяти. Например, для десяти блоков 34 памяти сумматор 30 является десятичным сут-шатором.

Формула изобретения

Устройство для управления обменом информацией, содержап;ее группу блоков памяти, коммутатор данных, сумматор, шифратор, счетчик выбора блока памяти, счетчик занятости, счетчик адресов ввода, счетчик адресов вывода, коммутатор адресов, два триггера, пять элементов {ШИ, два элемента И, элемент НЕ, причем группы информационных входов и выходов коммутатора данных образуют группы входов и выходов устройства для подклю чения соответственно к группам информационных выходов и входов ЭВМ, выход переполнения счетчика занято- сти является выходом устройства для подключения к входу разрешения ввода ЭВМ, выход первого элемента ИЛИ соединен с информационным входом первого триггера и является выходом устройства для подключения к входу разрешения вывода ЭВМ, выход второго триггера является выходом устройства для подключения к входу разрешения установки признака ввода ЭВМ, выход первого триггера соединен со счетным входом счетчика адресов вывода и является выходом устройства для подключения к входу разрешения установки признака вывода ЭВМ, первый вход первого элемента И является входом устройства для подключения к выходу признака конца вывода ЭВМ, первый вход второго элемента И соединен с установочным входом счетчика адресов ввода и является входом устройства для подключения к выходу признака конца ввода ЭВМ, вход элемента НЕ соединен с нулевым входом первого триггера, с управляющим входом ком- мутатора адресов, с управляющими входами коммутатора данных, с входами записи-чтения блоков памяти группы и является входом устройства для подключения к тактовому выходу ЭВМ, еди ничный вход второго триггера и син- хровход первого триггера являются входами устройства для подключения соответственно к выходу признака ввода ЭВМ и к выходу признака вывода ЭВМ, при этом группы информационных входов-выходов коммутатора данных соединены с ш формационными входами- выходами блоков памяти группы, адресные входы которых соединены с груп- пой информационных выходов коммутатора адресов, первая группа информационных входов которого соединена с группой выходов счетчика адресов вывода с с группой входов второго эле- мента ИЛИ, выход которого соединен с вторым входом первого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, выход

которого соединен 9 входом вычитания счетчика занятости и со счетным входом счетчика выбора блока памяти, группа выходов которого соединена с первой группой информационных входов сумматора, группа информационных выходов которого соединена с группой информационных входов шифратора, група входов первого элемента ИЛИ соединена с группой выходов счетчика занятости, вход сложения которого содинен с выходом четвертого элемента ИЛИ, первый вход которого соединен с выходом второго элемента И, второй вход которого соединен с выходом пятго элемента ИЛИ, группа входов которого соединена с второй группой информационных входов коммутатора адрсов и с группой выходов счетчика адресов ввода, выход переполнения которого соединен с вторым входом четвертого элемента ИЛИ, второй вхо третьего элемента ШМ соединен с выходом Переполнения счетчика адресов вывода, выход элемента НЕ соединен с н левьгм входом второго триггера, отличающееся тем, что, с целью повышения быстродействи в Него вверены кольцевой сдвиговый регистр, коммутатор выбора блока памяти, две группы элементов И, при этом разрешаювще входы блоков памяти группы соединены с соответствующими выходами элементов И первой группы, первые входы которых соединены с соответствующими выходами шифратора, разрядные входы элементов И первой группы соединены с соответствующими разрядными выходами коммутатора выбора блока памяти, управляющий вход которого соединен с первыми входами элементов И второй группы и с управляющим входом коммутатора адресов, выход первого триггера соединен с первой группой информационных входов коммутатора выбора блоков памяти, вторая группа информационных входов которого соединена с группой выходов кольцевого сдвигового регистра, выход старшего разряда которого соединен со счетным входом счетчика адресов ввода, установочный вход котрого соединен с установочным входом кольцевого сдвигового регистра, вход сдвига которого соединен с выходом второго триггера и с вторыми входами элементов И второй группы, третьи входы и выходы которых соеди915П821910

йены соответственно с группой выхо- тора, установочный вход счетчика

дов счетчика занятости и с второй группой информационных входов суммаадресов вывода соединен с перв ым входом первого элемента И.

.м

ю

адресов вывода соединен с перв ым входом первого элемента И.

| Авторское свидетельство СССР № 1177818, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство сопряжения | 1987 |

|

SU1425691A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| , | |||

Авторы

Даты

1989-09-15—Публикация

1987-12-29—Подача