Изобретение относится к вычислительной технике и может быть исполь зовано для сопряжения двух вычислительных машин с различными интерфейсами.

Целью изобретения является расширение класса решаемых задач для обеспечения функциональной возможности сопряжения двух разнотипных ЭВМ.

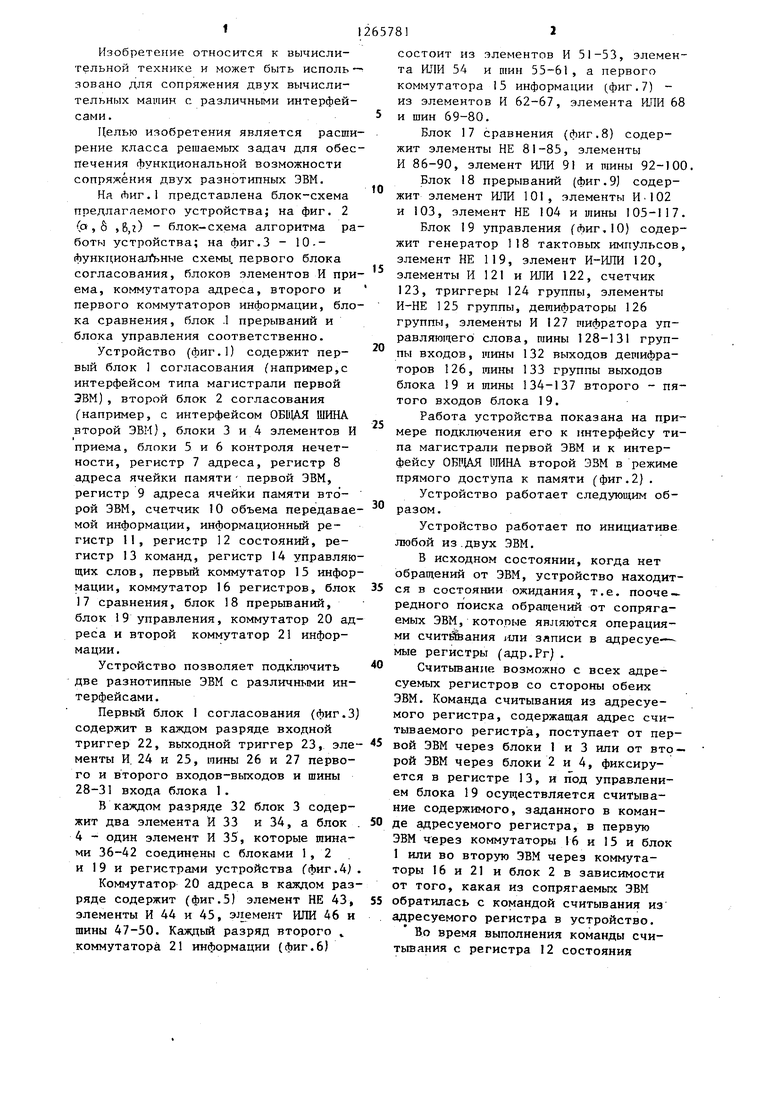

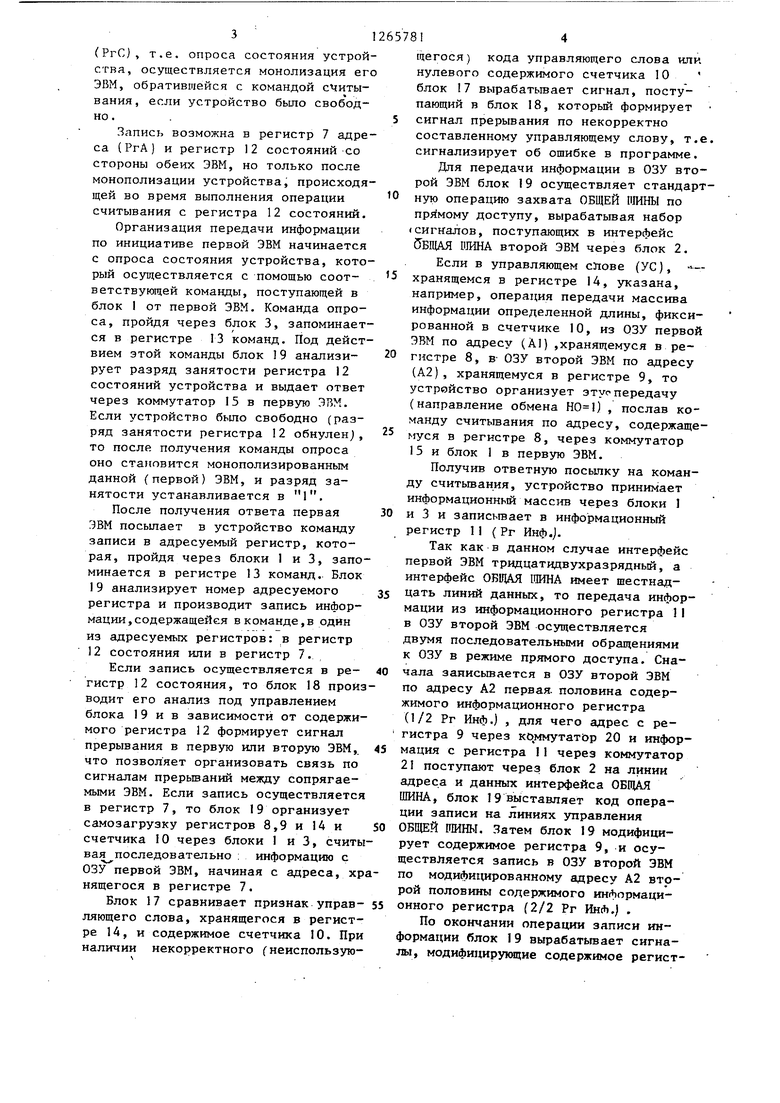

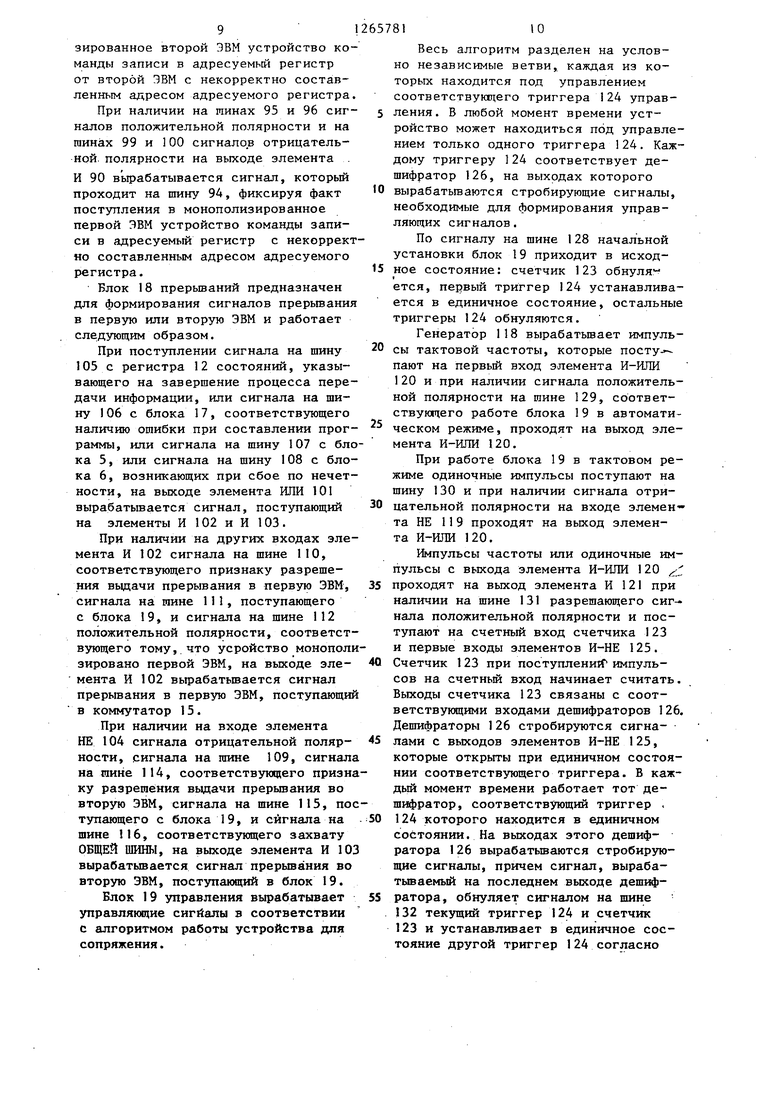

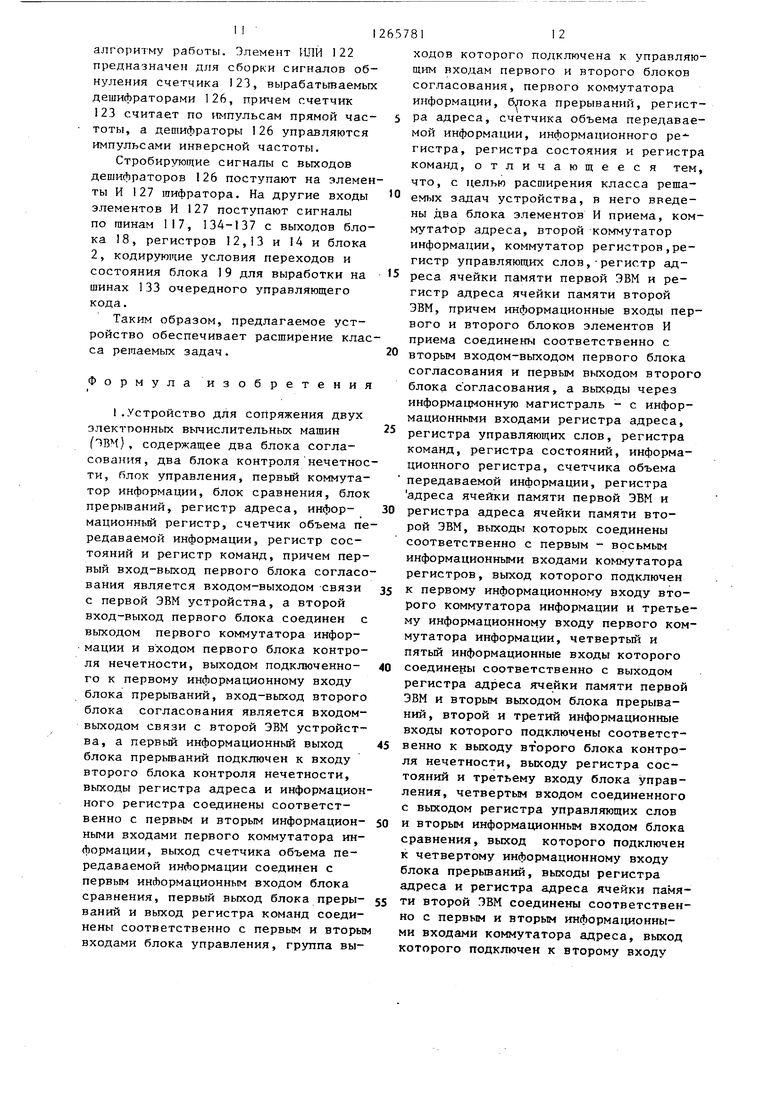

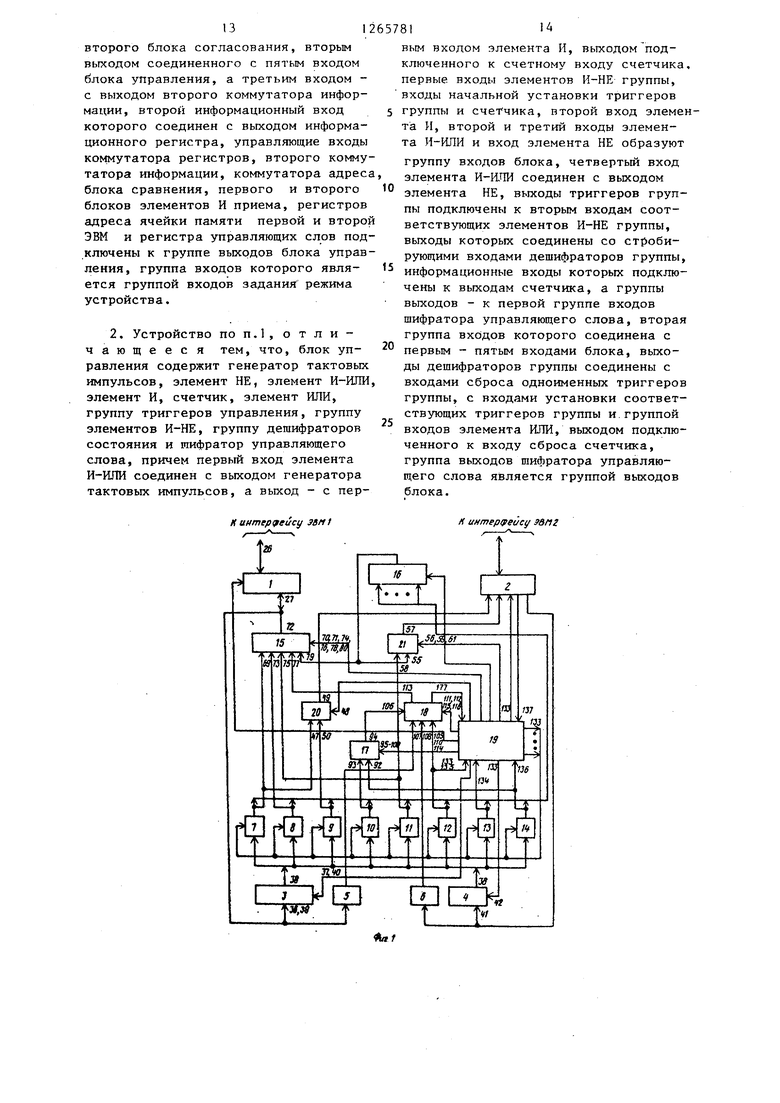

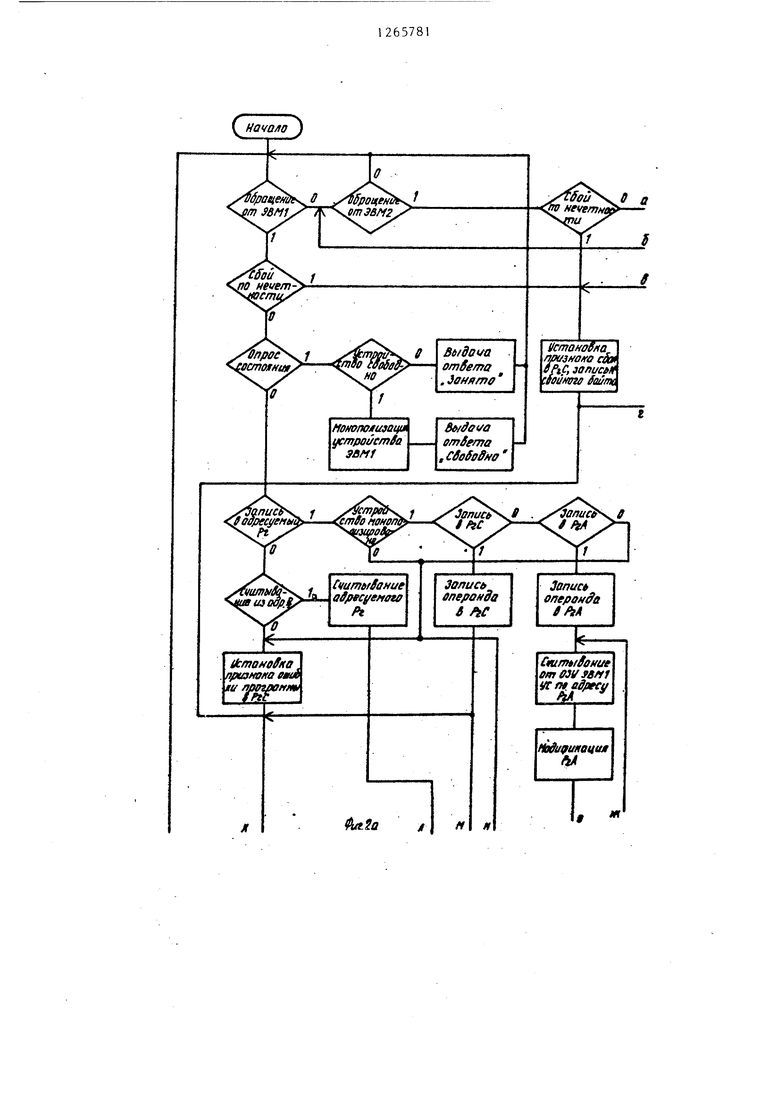

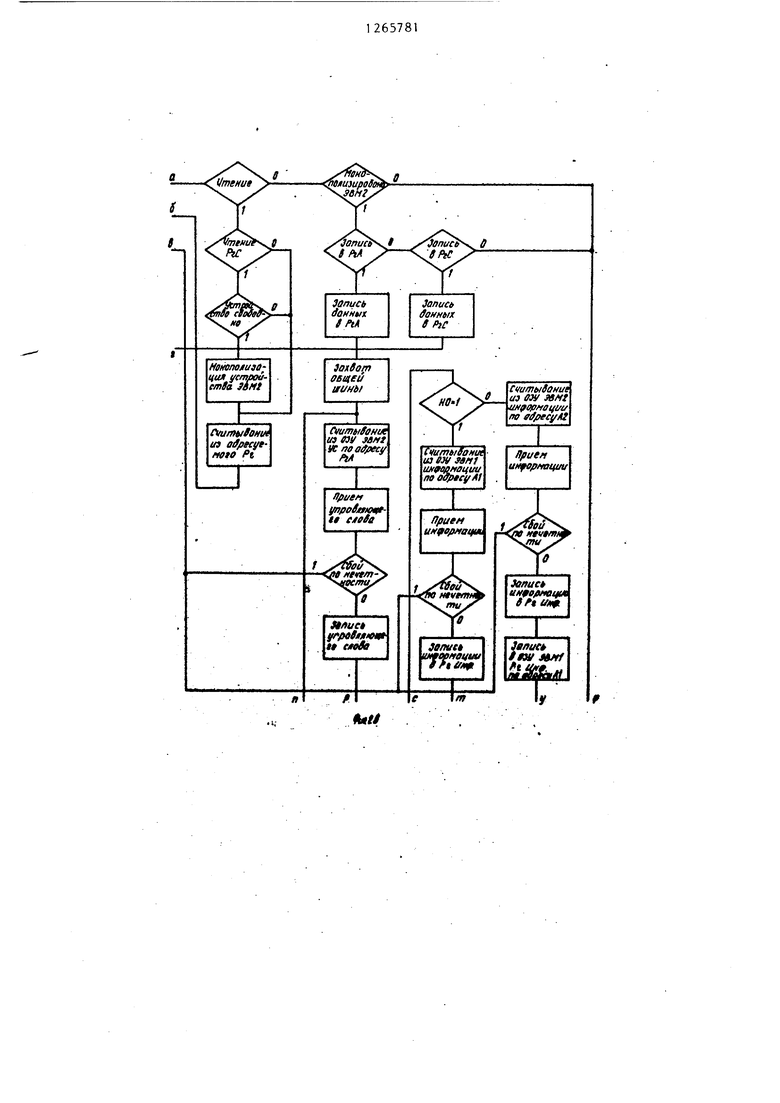

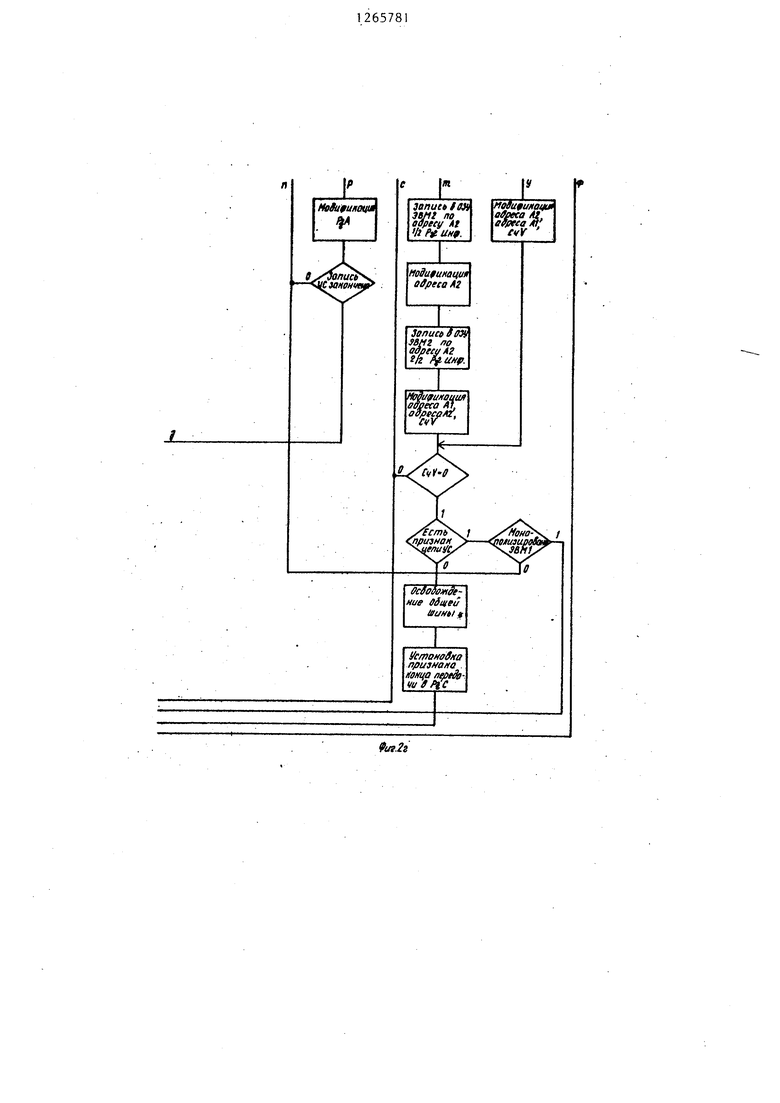

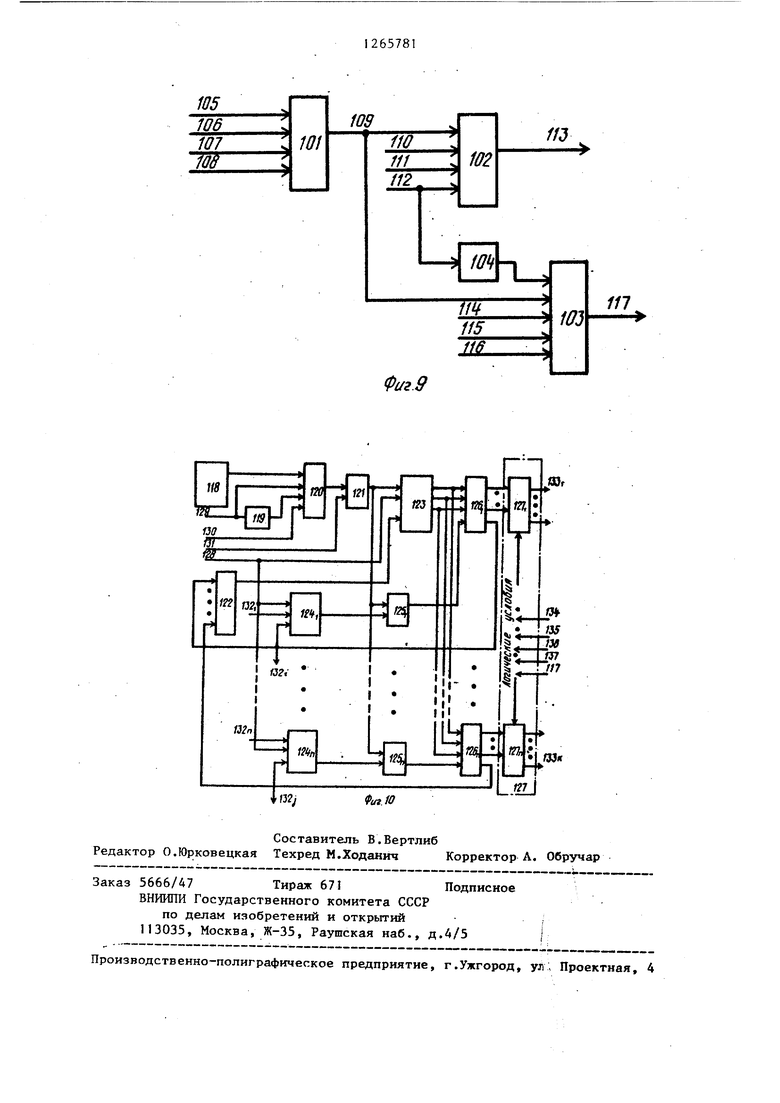

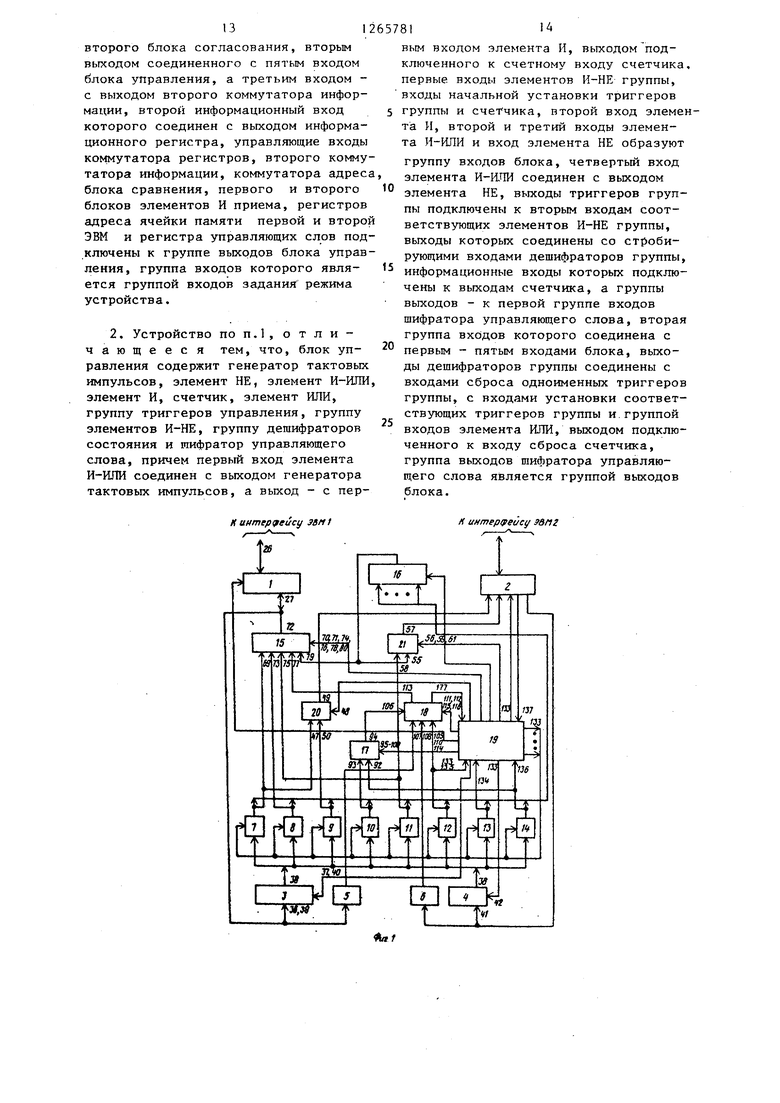

На Лиг.1 представлена блок-схема предлагаемого устройстваj на фиг. 2 (о, S ,6,г) блок-схема алгоритма работы устройства; на фиг.З - 10.функционал ные схемы, первого блока согласования, блоков элементов И приема, коммутатора адреса, второго и первого коммутаторов информации, блока сравнения, блок .1 прерываний и блока управления соответственно.

Устройство {фиг.1) содержит первый блок 1 согласования (например,с интерфейсом типа магистрали первой ЭВМ), второй блок 2 согласования (например, с интерфейсом OBDIAJI ШИНА второй ЭВМ), блоки 3 и 4 элементов И приема, блоки 5 и 6 контроля нечетности, регистр 7 адреса, регистр 8 адреса ячейки памяти - первой ЭВМ, регистр 9 адреса ячейки памяти второй ЭВМ, счетчик 10 объема передаваемой информации, информационный регистр 11, регистр 12 состояний, регистр 13 команд, регистр 14 управляющих слов, первый коммутатор 15 информации, коммутатор 16 регистров, блок 17 сравнения, блок 18 прерьгоаний, блок 19 управления, коммутатор 20 адреса и второй коммутатор 21 информации.

Устройство позволяет подключить две разнотипные ЭВМ с различными интерфейсами.

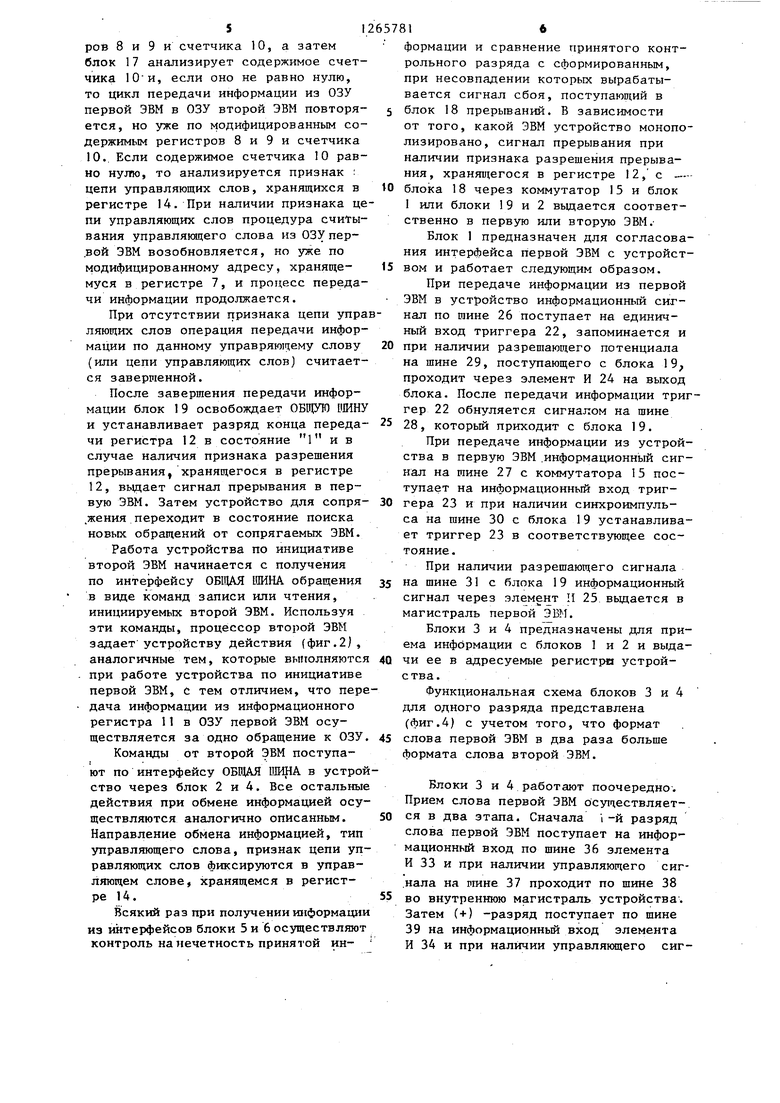

Первый блок 1 согласования (фиг.З) содержит в каждом разряде входной триггер 22, выходной триггер 23, элементы И. 24 и 25, шины 26 и 27 первого и второго входов-выходов и шины 28-31 входа блока 1.

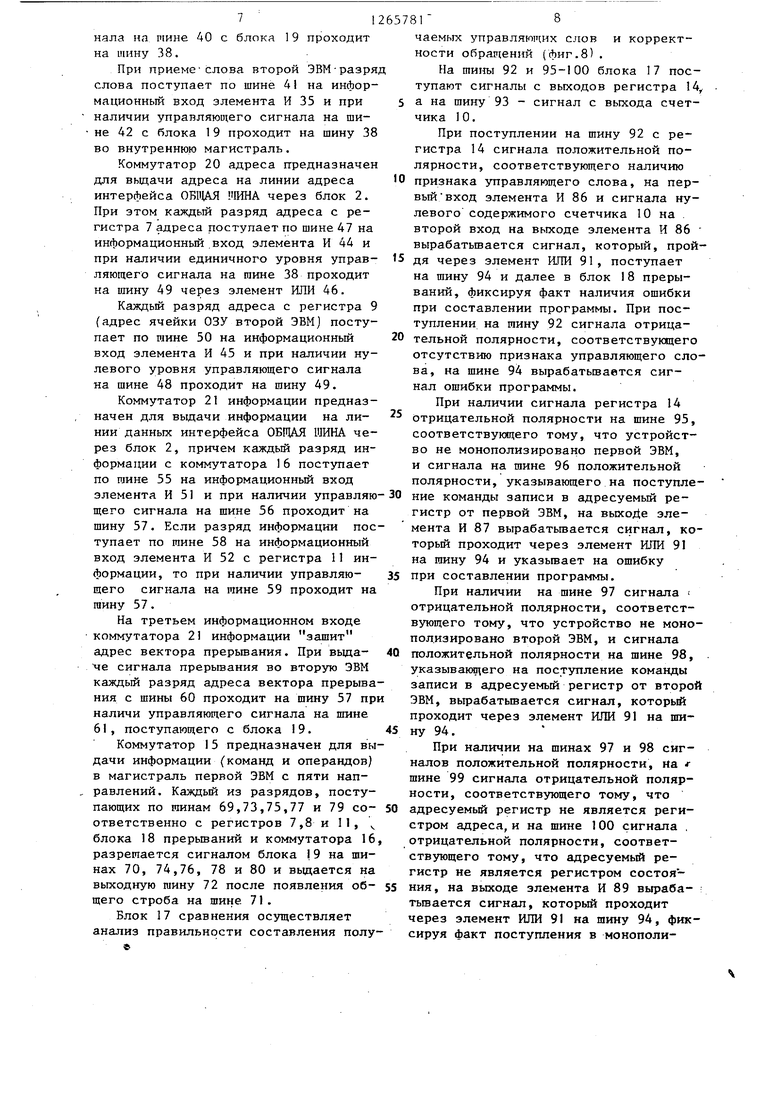

В каждом разряде 32 блок 3 содержит два элемента И 33 и 34, а блок 4 - один элемент И 35, которые шинами 36-42 соединены с блоками 1,2 и 19 и регистрами устройства fфиг.4 Коммутатор- 20 адреса в каждом разряде содержит (фиг.5) элемент НЕ 43, элементы И 44 и 45, элемент ИЛИ 46 и шины 47-50. Каждый разряд второго коммутатора 21 информации (фиг.6)

состоит из элементов И 51-53, элемента ИЛИ 54 и шин 55-61, а первого коммутатора 15 информации (фиг.7) из элементов И 62-67, элемента ИЛИ 68 и шин 69-80.

Блок 17 сравнения (фиг.8) содержит элементы НЕ 81-85, элементы И 86-90, элемент ИЛИ 91 и шины 92-100

Блок 18 прерываний (фиг.9) содержит элемент ИЛИ 101, элементы И102 и 103, элемент НЕ 104 и шины 105-117

Блок 19 управления (фиг,10) содержит генератор 118 тактовых импульсов элемент НЕ 119, элемент И-ИЛИ 120, элементы И 121 и ИЛИ 122, счетчик 123, триггеры 124 группы, элементы И-НЕ 125 группы, дешифраторы 126 группы, элементы И 127 шифратора управляющего слова, шины 128-131 группы входов, шины 132 выходов дешифраторов 126, шины 133 группы выходов блока 19 и шины 134-137 второго - пятого входов блока 19.

Работа устройства показана на примере подключения его к интерфейсу типа магистрали первой ЭВМ и к интерфейсу ОБР1АЯ иМНА второй ЭВМ в режиме прямого доступа к памяти (фиг.2).

Устройство работает следуювхим образом.

Устройство работает по инициативе любой из.двух ЭВМ.

В исходном состоянии, когда нет обращений от ЭВМ, устройство находится в состоянии ожидания, т.е. поочередного поиска обращений от сопрягаемых ЭВМ, которые являются операциями считйЬания Jши злписи в адресуе- мые регистры (адр.Рг).

Считьтание возможно с всех адресуемых регистров со стороны обеих ЭВМ. Команда считывания из адресуемого регистра, содержащая адрес считываемого регистра, поступает от первой ЭВМ через блоки 1 и 3 или от второй ЭВМ через блоки 2 и 4, фиксируется в регистре 13, и под управлением блока 19 осуществляется считывание содержимого, заданного в команде адресуемого регистра, в первую ЭВМ через коммутаторы 16 и 15 и блок I или во вторую ЭВМ через коммутаторы 16 и 21 и блок 2 в зависимости от того, какая из сопрягаемых ЭВМ обратилась с командой считывания из адресуемого регистра в устройство.

Во время выполнения команды считьюания с регистра 12 состояния 3 (РгС), т.е. опроса состояния устрой ства, осуществляется монолизация ег ЭВМ, обратившейся с командой считывания, если устройство было свободно. Запись возможна в регистр 7 адре са (РгА ) и регистр 12 состояний со стороны обеих ЭВМ, но только после монополизации устройства, происходя щей во время выполнения операции считывания с регистра 12 состояний. Организация передачи информации по инициативе первой ЭВМ начинается с опроса состояния устройства, кото рый осуществляется с помощью соответствующей команды, поступающей в блок I от первой ЭВМ. Команда опроса, пройдя через блок 3, запоминает ся в регистре 13 команд. Под дейст вием этой команды блок 19 анализирует разряд занятости регистра 12 состояний устройства и вьщает ответ через коммутатор 15 в первую ЭВМ. Если устройство было свободно (разряд занятости регистра 12 обнулен), то после получения команды опроса оно становится монополизированным данной (первой) ЭВМ, и разряд занятости устанавливается в 1. После получения ответа первая ЭВМ посылает в устройство команду записи в адресуемый регистр, которая, пройдя через блоки 1 и 3, запо минается в регистре 13 команд. Блок 19 анализирует номер адресуемого регистра и производит запись информации, содержащейся в команде,в один из адресуемых регистров: в регистр 12 состояния или в регистр 7. Если запись осуществляется в регистр 12 состояния, то блок 18 произ водит его анализ под управлением блока 19 и в зависимости от содержимого регистра 12 формирует сигнал прерывания в первую или вторую ЭВМ, что позволяет организовать связь по сигналам прерьшаний между сопрягаемыми ЭВМ. Если запись осуществляется в регистр 7, то блок I9 организует самозагрузку регистров 8,9 и 14 и счетчика 10 через блоки 1 и 3, считы вая последовательно : информацию с хОЗУ первой ЭВМ, начиная с адреса, хр нящегося в регистре 7. Блок 17 сравнивает признак управляющего слова, хранящегося в регистре 14, и содержимое счетчика 10. При наличии некорректного (неиспользую- 8 щегося) кода управляющего слова или нулевого содержимого счетчика 10 блок 17 вырабатьгоает сигнал, поступающий в блок 18, который формирует сигнал прерывания по некорректно составленному управляющему слову, т.е. сигнализирует об ошибке в программе. Для передачи информации в ОЗУ второй ЭВМ блок I9 осуществляет стандартную операцию захвата ОБЩЕЙ ПШНЫ по доступу, вырабатывая набор (сигналов, поступающих в интерфейс БЩАЯ гаИНА второй ЭВМ через блок 2. Если в управляющем слове (УС), хранящемся в регистре 14, указана, например, операция передачи массива информации определенной длины, фиксированной в счетчике 10, из ОЗУ первой ЭВМ по адресу (AI),хранящемуся в регистре 8, в- ОЗУ второй ЭВМ по адресу (А2), хранящемуся в регистре 9, то устройство организует эту передачу (направление обмена ) , послав команду считывания по адресу, содержащемуся в регистре 8, через коммутатор 15 и блок 1 в первую ЭВМ. Получив ответную посыпку на команду считьшания, устройство принимает информационный массив через блоки 1 и 3 и записьгеает в информационный регистр 11 (Рг Инф.. Так как в данном случае интерфейс первой ЭВМ тридцатидвухразрядный, а интерфейс ОБЩАЯ ИМНА имеет шестнадцать линий данных, то передача информации из информационного регистра 1I в ОЗУ второй ЭВМ осуществляется двумя последовательными обращениями к ОЗУ в режиме прямого доступа. Сначала записьшается в ОЗУ второй ЭВМ по адресу А2 первая- половина содержимого информационного регистра (1/2 Рг Инф.) , для чего адрес с регистра 9 через ко.ммутатор 20 и информация с регистра 11 через коммутатор 21 поступают через блок 2 на линии адреса и данных интерфейса ОБЩАЯ ШИНА, блок 19 выставляет код операции записи на линиях управления ОБЩЕЙ ПШНЫ. Затем блок 19 модифицирует содержимое регистра 9, и осуществляется запись в ОЗУ второй ЭВМ по модифицированному адресу А2 второй половины содержимого информационного регистра (2/2 Рг ИнЛ.) . По окончании операции записи информации блок 19 вырабатьгеает сигналы, модифицирующие содержимое регистов 8 и 9 и счетчика 10, а затем лок 17 анализирует содержимое счетика 10и, если оно не равно нулю, о цикл передачи информации из ОЗУ ервой ЭВМ в ОЗУ второй ЭВМ повторя- 5 тся, но уже по модифицированным соержимым регистров 8 и 9 и счетчика 10.. Если содержимое счетчика 10 раво нулю, то анализируется признак : цепи управляющих слов, хранящихся в tO регистре 14. При наличии признака цепи управляющих слов процедура считывания управлякнцего слова из ОЗУ первой ЭВМ возобновляется, но уже по модифицированному адресу, храняще- 15 муся в регистре 7, и процесс передачи информации продолжается.

При отсутствии признака цепи управляющих слов операция передачи информации по данному управряющему слову 20 (или цепи управляющих слов) считается завершенной.

После завершения передачи информации блок 19 освобождает ОБЩУЮ ШИНУ и устанавливает разряд конца переда- 25 чи регистра 12 в состояние 1 и в случае наличия признака разрешения прерывания, хранящегося в регистре 12, выдает сигнал прерывания в первую ЭВМ. Затем устройство для сопря- 30 жения переходит в состояние поиска новых обращений от сопрягаемых ЭВМ. Работа устройства по инициативе второй ЭВМ начинается с получения по интерфейсу ОБЩАЯ ИННА обращения 35 в виде команд записи или чтения, инициируемых второй ЭВМ. Используя эти команды, процессор второй ЭВМ задает устройству действия (фиг.2), аналогичные тем, которые выполняются 40 при работе устройства по инициативе первой ЭВМ, с тем отличием, что передача информации из информационного регистра 11 в ОЗУ первой ЭВМ осуществляется за одно обращение к ОЗУ. 45

Команды от второй ЭВМ поступают по интерфейсу ОБВ1АЯ UJMHA в устройство через блок 2 и 4. Все остальные действия при обмене информацией осуществляются аналогично описанным. 50 Направление обмена информацией, тип управляющего слова, признак цепи управляющих слов фиксируются в управляющем слове, хранящемся в регистре 14.55

Всякий раз при получении информации из интерфейсов блоки 5 и 6 осуществляют контроль на нечетность принятой информации и сравнение принятого контрольного разряда с сформированным, при несовпадении которых вырабатывается сигнал сбоя, поступающий в блок 18 прерываний. В зависимости от того, какой ЭВМ устройство монополизировано, сигнал прерывания при наличии признака разрешения прерывания, храняи1егося в регистре 12, с -блока 18 через коммутатор 15 и блок 1 или блоки 19 и 2 вьщается соответственно в первую или вторую ЭВМ.Блок 1 предназначен для согласования интерфейса первой ЭВМ с устройством и работает следующим образом.

При передаче информации из первой ЭВМ в устройство информационный сигнал по шине 26 поступает на единичный вход триггера 22, запоминается и при наличии разрешающего потенциала на шине 29, поступающего с блока 19 проходит через элемент И 24 на выход блока. После передачи информации триггер 22 обнуляется сигналом на шине 28, который приходит с блока 19.

При передаче информации из устройства в первую ЭВМ .информационный сигнал на шине 27 с коммутатора 15 поступает на информационный вход триггера 23 и при наличии синхроимпульса на шине 30 с блока 19 устанавливает триггер 23 в соответствующее состояние.

При наличии разрешающего сигнала на шине 31 с блока 9 информационный сигнал через элемент И 25 вьщается в магистраль первой ЭВМ.

Блоки 3 и 4 предназначены для приема информации с блоков I и 2 и выдачи ее в адресуемые регистри устройства.

Функциональная схема блоков 3 и 4 для одного разряда представлена (фиг.4) с учетом того, что формат слова первой ЭВМ в два раза больше формата слова второй ЭВМ.

Блоки 3 и 4 работают поочередно-. Прием слова первой ЭВМ осу11ествляется в два зтапа. Сначала i-и разряд слова первой ЭВМ поступает на информационный вход по шине 36 злемента И 33 и при наличии управляющего сиг.нала на гаине 37 проходит по шине 38 во внутреннюю магистраль устройства. Затем (+) -разряд поступает по шине 39 на информационньм вход злемента И 34 и при наличии управлякядего сигнала на шиие 40 с блока 19 проходит на шину 38. При приемеслова второй ЭВМ-разря слова поступает по шине 41 на информационный вход элемента И 35 и при наличии управляюи;его сигнала на шине 42 с блока 19 проходит на шину 38 во внутреннюю магистраль. Коммутатор 20 адреса предназначен для вьщачи адреса на линии адреса интерфейса ОБЩАЯ ШИНА через блок 2. При этом каждый разряд адреса с регистра 7 адреса поступает по шине 47 на информационный.вход элемента И 44 и при наличии единичного уровня управляющего сигнала на шине 38 проходит на шину 49 через элемент ИЛИ 46. Каждый разряд адреса с регистра 9 (адрес ячейки ОЗУ второй ЭВМ) поступает по шине 50 на информационный вход элемента И 45 и при наличии нулевого уровня управляющего сигнала на шине 48 проходит на шину 49. Коммутатор 21 информации предназначен для вьщачи информации на линии данных интерфейса ОБЩАЯ ШИНА через блок 2, причем каждый разряд информации с коммутатора 16 поступает по шине 55 на информационный вход элемента И 51 и при наличии управляю

щего сигнала на шине 56 проходит на шину 57. Если разряд информации поступает по шине 58 на информационный вход элемента И 52 с регистра 11 информации, то при наличии управляющего сигнала на шине 59 проходит на шину 57.

На третьем информационном входе коммутатора 21 информации зашит адрес вектора прерьюания. При вьща е сигнала прерьшания во вторую ЭВМ каждый разряд адреса вектора прерывания с шины 60 проходит на шину 57 при наличи управляющего сигнала на шине 6I, поступающего с блока 19.

Коммутатор 15 предназначен для выдачи информации (команд и операндов) в магистраль первой ЭВМ с пяти направлений. Каждый из разрядов, поступающих по шинам 69,73,75,77 и 79 соответственно с регистров 7,8 и П, блока 18 прерьтаний и коммутатора 16, разрепается сигналом блока 9 на шинах 70, 74,76, 78 и 80 и вьщается на выходную шину 72 после появления общего строба на шине 71.

Блок 17 сравнения осуществляет анализ правильности составления полуе

гистр от первой ЭВМ, на выхоДе элемента И 87 вырабатьгоается сигнал, который проходит через элемент ИЛИ 91 на шину 94 и указывает на ошибку при составлении программы.

При наличии на шине 97 сигнала отрицательной полярности, соответствующего тому, что устройство не монополизировано второй ЭВМ, и сигнала положительной полярности на шине 98, указывающего на поступление команды записи в адресуемый регистр от второ ЭВМ, вырабатьтается сигнал, который проходит через элемент ИЛИ 91 на шину 94.

При наличии на шинах 97 и 98 сигналов положительной полярности, на f шине 99 сигнала отрицательной полярности, соответствующего тому, что адресуемьй регистр не является регистром адреса, и на шине 100 сигнала . отрицательной полярности, соответствующего тому, что адресуемый регистр не является регистром состояния, на выходе элемента И 89 вырабатьшается сигнал, который проходит через элемент ИЛИ 91 на шину 94, фиксируя факт поступления в монополичаемых управляющих слов и корректности обращений (фиг.8). На шины 92 и 95-100 блока 17 поступают сигналы с выходов регистра 14 а на шину 93 - сигнал с выхода счетчика 10. При поступлении на шину 92 с регистра 14 сигнала положительной полярности, соответствующего наличию признака управляющего слова, на первый вход элемента И 86 и сигнала нулевого содержимого счетчика 10 на . второй вход на выходе элемента И 86 вырабатьшается сигнал, который, пройдя через элемент ИЛИ 91, поступает на щину 94 и далее в блок 18 прерываний, фиксируя факт наличия ошибки при составлении программы. При поступлении на шину 92 сигнала отрицательной полярности, соответствующего отсутствию признака управляющего слова, на шине 94 вырабатывается сигнал ощибки программы. При наличии сигнала регистра 14 отрицательной полярности на шине 95, соответствующего тому, что устройство не монополизировано первой ЭВМ, и сигнала на шине 96 положительной полярности, указывающего на поступление команды записи в адресуемый ре9зированное второй ЭВМ устройство команды записи в адресуемый регистр от второй ЭВМ с некорректно составленным адресом адресуемого регистра При наличии на гаинах 95 и 96 сигналов положительной полярности и на гаинах 99 и 100 сигналов отрицательной, полярности на выходе элемента . И 90 вырабатывается сигнал, которьш проходит на шину 94, фиксируя факт поступления в монополизированное первой ЭВМ устройство команды записи в адресуемый регистр с некоррект но составленным адресом адресуемого регистра. Блок 18 прерьшаний предназначен для формирования сигналов прерьгоания в первую или вторую ЭВМ и работает следующим образом. При поступлении сигнала на шину 105 с регистра 12 состояний, указывающего на завершение процесса передачи информации, или сигнала на шину I 06 с блока 17, соответствующего наличию ошибки при составлении программы , или сигнала на шину 107 с бло ка 5, или сигнала на шину 108 с блока 6, возникающих при сбое по нечетности, на вькоде элемента ИЛИ 101 вырабатывается сигнал, поступающий на элементы И 102 и И 103. При наличии на других входах эле мента И 102 сигнала на шине 110, соответствующего признаку разрешения выдачи прерывания в первую ЭВМ, сигнала на шине 1П, поступающего с блока 19, и сигнала на шине 112 положительной полярности, соответст вующего тому, что усройство монопол зировано первой ЭВМ, на выходе элемента И 102 вьфабатьшается сигнал прерьтания в первую ЭВМ, поступающи в коммутатор 15. При наличии на входе элемента НЕ 104 сигнала отрицательной полярности, сигнала на шине 109, сигнал на иине 114, соответствующего призн ку разрешения вьщачи прерывания во вторую ЭВМ, сигнала на шине 115, по тупающего с блока 19, и сигнала на шине 116, соответствующего захвату ОБЩЕЙ ШИНЫ, на выходе элемента И 10 вырабатьтается сигнал прерывания во вторую ЭВМ, поступающий в блок 19. Блок 19 управления вырабатывает управляющие сигйалы в соответствии с алгоритмом работы устройства для сопряжения. 81 Весь алгоритм разделен на условно независимые ветви, каждая из которых находится под управлением соответствующего триггера I24 управления. В любой момент времени устройство может находиться под управлением только одного триггера 124. Каждому триггеру 124 соответствует дешифратор 126, на выходах которого вырабатьшаются стробирующие сигналы, необходимые для формирования управляющих сигналов. По сигналу на шине 128 начальной установки блок 19 приходит в исходное состояние: счетчик 123 обнуля-ется, первый триггер 124 устанавливается в единичное состояние, остальные триггеры 124 обнуляются. Генератор 118 вырабатьшает импульсы тактовой частоты, которые посту- пают на первый вход элемента И-ИЛИ 120 и при наличии сигнала положительной полярности на шине 129, соответствующего работе блока 19 в автоматическом режиме, проходят на выход элемента И-ИЛИ 120. При работе блока 19 в тактовом режиме одиночные импульсы поступают на шину 130 и при наличии сигнала отрицательной полярности на входе элемента НЕ 119 проходят на выход элемента И-ИЛИ 120. Импульсы частоты или одиночные импульсы с выхода элемента И-ИЛИ 120 . проходят на выход элемента И 121 при наличии на шине 131 разрешающего сиг-нала положительной полярности и поступают на счетный вход счетчика 123 и первые входы элементов И-НЕ 125. Счетчик 123 при поступлений импульсов на счетньй вход начинает считать. Выходы счетчика 123 связаны с соответствующими входами дешифраторов 126. Дешифраторы 126 стробируются сигналами с выходов элементов И-НЕ 125, которые открыты при единичном состоянии соответствующего триггера. В каждый момент времени работает тот дешифратор, соответствующий триггер . 124 которого находится в единичном состоянии. На выходах этого дешифратора 126 вырабатьшаются стробирующие сигналы, причем сигнал, вырабатываемый на последнем выходе дешифратора, обнуляет сигналом на шине 132 текущий триггер 124 и счетчик 123 и устанавливает в единичное состояние другой триггер 124 согласно 11 алгоритму работы. Элемент ИЛИ 122 предназначен для сборки сигналов об нуления счетчика 123, вырабатьшаемы дешифраторами 126, причем счетчик 123 считает по импульсам прямой час тоты, а дешифраторы 126 управляются импульсами инверсной частоты. Стробирующие сигналы с выходов дешифраторов 126 поступают на элеме ты И 127 шифратора. На другие входы элементов И 127 поступают сигналы по гаинам 117, 134-137 с выходов бло ка 18, регистров 12,13 и 14 и блока 2, кодирующие условия переходов и состояния блока 19 для выработки на шинах 133 очередного управляющего кода. Таким образом, предлагаемое устройство обеспечивает расширение клас са решаемых задач. Формула изобретения I.Устройство для сопряжения двух электронных вычислительных машин ), содержащее два блока согласования, два блока контролянечетнос ти, блок управления, первый коммутатор информации, блок сравнения, блок прерываний, регистр адреса, информационный регистр, счетчик объема пе редаваемой информации, регистр состояний и регистр команд, причем первый вход-выход первого блока согласо вания является входом-выходом -связи с первой ЭВМ устройства, а второй вход-выход первого блока соединен с выходом первого коммутатора информации и входом первого блока контроля нечетности, выходом подключенного к первому информационному входу блока прерываний, вход-выход второго блока согласования является входомвыходом связи с второй ЭВМ устройства, а первый информационный выход блока прерываний подключен к входу второго блока контроля нечетности, выходы регистра адреса и информацион ного регистра соединены соответственно с nepBbtM и вторым информационньми входами первого коммутатора информации, выход счетчика объема передаваемой инЛормации соединен с первым информационным входом блока сравнения, первый выход блока прерываний и выход регистра команд соединены соответственно с первым и вторы входами блока управления, группа вы81ходов которого подключена к управляющим входам первого и второго блоков согласования, первого коьжутатора информации, блока прерываний, регистра адреса, счетчика объема передаваемой информации, информационного регистра, регистра состояния и регистра команд, отличающееся тем, что, с целью расширения класса решаемых задач устройства, в него введены два блока элементов И приема, коммутафор адреса, второй коммутатор информации, коммутатор регистров,регистр управляющих слов,регистр адреса ячейки памяти первой ЭВМ и регистр адреса ячейки памяти второй ЭВМ, причем информационные входы первого и второго блоков элементов И приема соединены соответственно с вторым входом-выходом первого блока согласования и первым выходом второго блока согласования, а выхрды через информацмонную магистраль - с информационными входами регистра адреса, регистра управляющих слов, регистра команд, регистра состояний, информационного регистра, счетчика объема передаваемой информации, регистра адреса ячейки памяти первой ЭВМ и регистра адреса ячейки памяти второй ЭВМ, выходы которых соединены соответственно с первым - восьмым информационными входами коммутатора регистров, выход которого подключен к первому информационному входу второго коммутатора информации и третьему информационному входу первого коммутатора информации, четвертый и пятый информационные входы которого соединены соответственно с выходом регистра адреса ячейки памяти первой ЭВМ и вторым выходом блока прерываний, второй и третий информационные входы которого подключены соответственно к выходу второго блока контроля нечетности, выходу регистра состояний и третьему входу блока управления, четвертым входом соединенного с выходом регистра управляющих слов и вторым информационным входом блока сравнения, выход которого подключен к четвертому информационному входу блока прерьшаний, выходы регистра адреса и регистра адреса ячейки памяти второй ЭВМ соединены соответственно с первым и вторым информационными входами коммутатора адреса, выход которого подключен к второму входу второго блока согласования, вторым выходом соединенного с пятым входом блока управления, а третьим входом с выходом второго коммутатора информации, второй информационный вход которого соединен с выходом информационного регистра, управляющие входы коммутатора регистров, второго комму татора информации, коммутатора адреса блока сравнения, первого и второго блоков элементов И приема, регистров адреса ячейки памяти первой и второй ЭВМ и регистра управляющих слов подключены к группе выходов блока управ ления, группа входов которого является группой входов задания режима устройства. 2. Устройство по П.1, о т л и чающееся тем, что, блок управления содержит генератор тактовых импульсов, элемент НЕ, элемент И-ИЛИ элемент И, счетчик, элемент ИЛИ, группу триггеров управления, группу элементов И-НЕ, группу дешифраторов состояния и шифратор управляющего слова, причем первый вход элемента И-ШТИ соединен с выходом генератора тактовых импульсов, а выход - с перКинтерфейсу 38fit 12

л интерфейсу вт 11ым входом элемента И, выходом подлюченного к счетному входу счетчика, входы элементов И-НЕ группы, ходы начальной установки триггеров группы и счетчика, второй вход элемента И, второй и третий входы элемента И-ИЛИ и вход элемента НЕ обраэуют группу входов блока, четвертый вход элемента И-ИЛИ соединен с выходом элемента НЕ, выходы триггеров группы подключены к вторым входам соответствующих элементов И-НЕ группы, выходы которых соединены со стробирующими входами дешифраторов группы, информационные входы которых подключены к выходам счетчика, а группы выходов - к первой группе входов шифратора управляющего слова, вторая группа входов которого соединена с первым - пятым входами блока, выходы дешифраторов группы соединены с входами сброса одноименных триггеров группы, с входами установки соответствующих триггеров группы и.группой входов элемента ИЛИ, выходом подключенного к входу сброса счетчика, группа выходов шифратора управляющего слова является группой выходов блока.

j/ava ffj W ftevemft l/cmoHoSHO пмзнот cS iPiC, aanuctit cSoufone Soumu a

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1596341A1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Имитатор канала | 1987 |

|

SU1467556A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1501077A1 |

| Устройство для сопряжения ЭВМ с периферийной системой | 1989 |

|

SU1635188A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1988 |

|

SU1605241A1 |

| Устройство для сопряжения ЭВМ с магистралью внешних устройств | 1985 |

|

SU1408440A1 |

| Устройство для сопряжения двух электронных вычислительных машин (эвм) | 1984 |

|

SU1187172A1 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

Изобретение относится к области вычислительной техники и может быть использовано для сопряжения двух ЭВМ с различньми интерфейсами. Ц&лью изобретения является расширение класса регааемых .задач для обеспечения функциональной возможности сопряжения двух разнотипных ЭВМ. Цель достигается тем, что в устройство, содержащее два блока согласования, /(ва блока контроля нечетности, блок управления, первый коммутатор информации, блок сравнения, блок прерываний, регистр адреса, информационный регистр,, счетчик объема передаваемой информации, регистр состояний и регистр команд, введены два блока эле ментов И приема, коммутатор адреса, второй коммутатор информации, жоммутатор регистров, регистр управляющих (Л слов, регистры адреса ячейки памяти первой и второй ЭВМ. I з.п. ф-лы, 10 ил.

Фиг Л

Фи2.д

57

ffff

Ж.

Pt/z.ff

Фиг. 8

Фиг.9

Авторы

Даты

1986-10-23—Публикация

1983-12-07—Подача