сл

с

Изобретение относится к вычислительной технике и может быть ясполь зовано при построении систем пакшти ЭВМ и информационно-справочных устройств .

Целью изобретения является повышение пропускной способности устройства за счет увеличения числа подключаемых блоков памяти и умань- шение аппаратурных затрат.

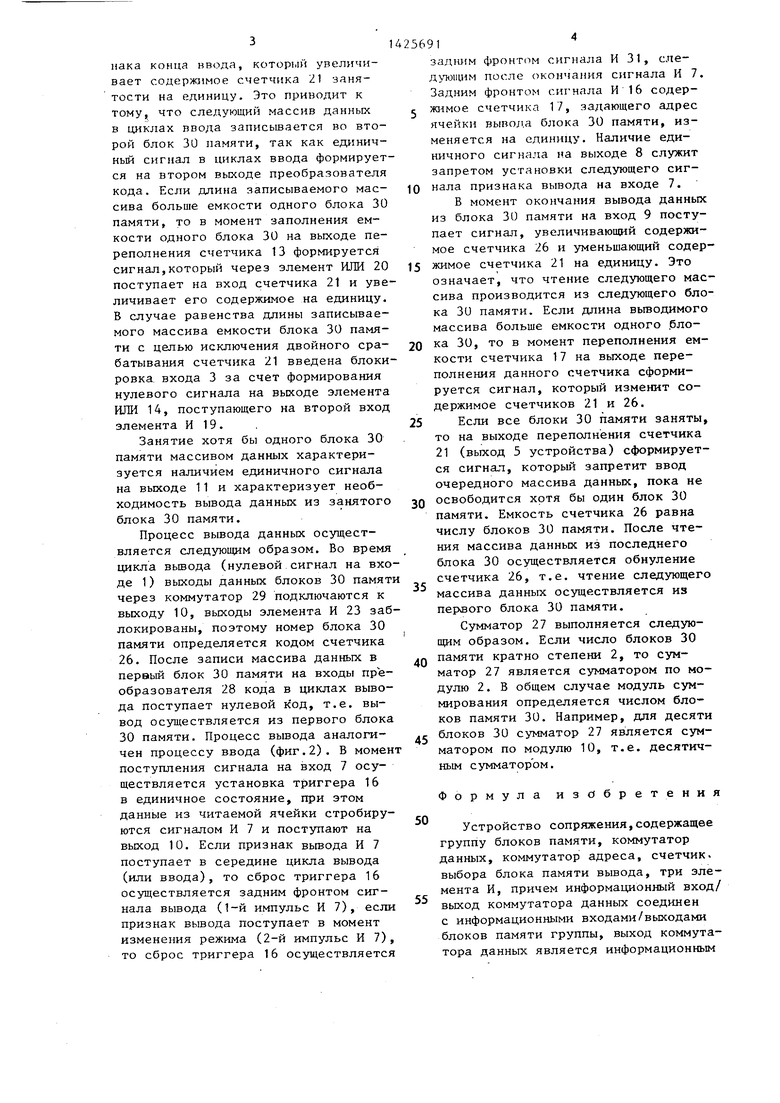

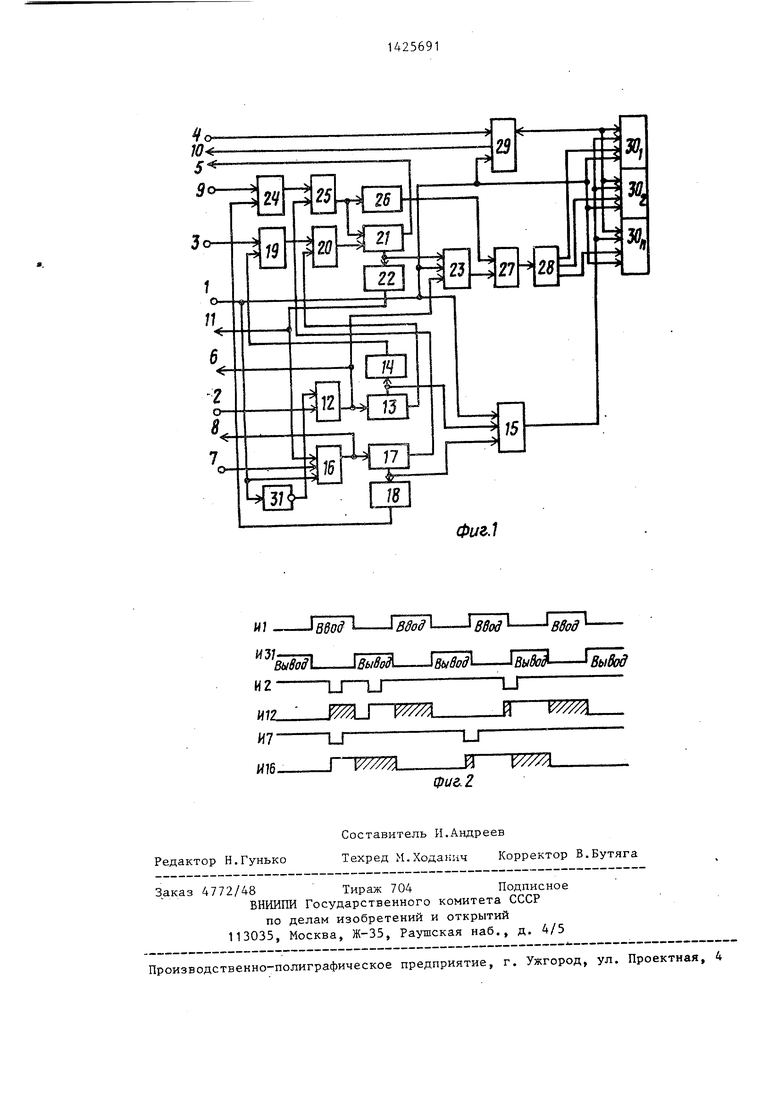

На фиг, 1 представлена функциональная схема устройства; на фиг„2- Бременные диаграмм™ работы устройства,

х Устройство сопряжения содержт-гг тактовый вход 1,, вход 2 признака ввода, вход 3 признака, конца ввода информационньй вход 4,, выход 5 разрешения ввода, выход 6 разрешения установки признака ввода;, вход 7 признака вьшода выход 8 разрешения установки признака вьгоода., вход 9 признака конца вывода, информационный выход 10, выход 11 разрешения вывода S, первый триггер 12, счетчик 13 адресов ввода, первьй элемент

ИЛИ 14д коммутатор 15 адресаj второ триггер 16, счетчик 17 адресов вывода, второй элемент ИЖ 18,, первый элемент И 19., третий элемент ИЖ 20 счетчик 21 занятости} пятый элемент ИЛИ 22.. третий элемент И 23,, второй элемент И 24 четвертый элемент

ИЛИ 25, счетчик 26 выбора блока памяти вывода,, сумматор 27 преобразователь 28 кода5 коммутатор 29 данных, г,руппу 30 блоков памяти, элемент НЕ 31,

Устро.йство работает следующим образом.

В начальный момент производится установка триггеров 12 и 16, счет-- чиков 13., 17, 21J 26 в нулевое состояние (цепи установки не показаньг) При этом на выходах 5 6 8 формируются нулевые уровни,, разррша ющие обращение к устройству, Установка счетчиков 21 и 26 в нулевое состояние приводит к подаче на в ходы cim матора 27 нулевых кодов,, при этом на- первом выходе преобразователл 28 кода, преобразующего двоичньй код в унитарньш, формируется е,циничнь:1й сигналJ который устанавливает режи:м записи в первом блоке 30 памяти во время действия положительных импульсов на входе 1 устройс1 ва.

Процессы ввода и вывода, управляемые тактовой частотой по входу 1, :ш1люстрируются временной диаграммой,

приведенной на фиг.2, При наличии свободных блоков Зи памяти (на выходе .5 устройства - нулевой потен- 1щал) на информационном входе 4 устанавливается входная информация,

а. на вход 2 подается стробир тощий отрицательный сигнал длительность которого равна циклу записи данных в блок 30 памяти. В момент действия стробирующего сигнала признака вво5 ДД на входе 2 производится установка триггера 12 в единичное состояние,, при этом на выходе 6 устройства, формируется единичный сигнал, запрещающий смену входной информа0 дни и установку след тощего строб- сигнала признака ввода. Если строб- сигнал признака ввода формируется в начале или середине импульса записи на входе 1(1-й импульс И2) или

5 во время действия импульсов чтения на входе 1 (2-й импульс И2), то установка триггера 12 в нулевое состояние осуществляется ближайшим от- рицатеЛьным фронтом тактового им0 пульса, при этом на выходе 6 разрешения установки признака вывода формируется нулевой потенциал, разреша- Ю1ЦИЙ изменение информации на входе 4 и установку следующего стробирую- щего импульса ка входе 2j а задним

5

0

5

0

5

фронтом импульса с выхода триггера 12 производится увеличение на единицу содержимого счетчика 13, задающего адрес сле,цующей ячейки первого блока 30 памяти. Если строб-сигнал признака ввода формируется отрицательного перепада на тактовом входе 1 (3-й импульс И2), то установка триггера 12 в нулевое состояние осуществляется отрицательным фронтом тактового импульса, следующего после окончания строб-сигнэ,ла признака ввода,, Время действия сигнала на входе выборки блоков 30 памяти определяется д штельностью импульсов на входе 1 устройства и на выходе триггера 12 (заштриховано на временной диаграмме) и в любом случае не может быть меньше длительности сигналов признака ввода, определяюш;их длительность цикла записи. I

В .момент окончания цикла записи массива в первьш блок 30 памяти на входе 3 формируется сигнал приз- .

пака конца ввода, который увеличивает содержимое счетчика 21 занятости на единицу. Это приводит к тому, что следующий массив данных в циклах ввода записьшается во второй блок 30 памяти, так как единичный сигнал в циклах ввода формируется на втором выходе преобразователя кода. Если длина записываемого массива больше емкости одного блока 30 памяти, то в момент заполнения емкости одного блока 30 на выходе переполнения счетчика 13 формируется сигнал,который через элемент ИЛИ 20 поступает на вход счетчика 21 и увеличивает его содержимое на единицу. В случае равенства длины записываемого массива емкости блока 30 памяти с целью исключения двойного срабатывания счетчика 21 введена блокировка входа 3 за счет формирования нулевого сигнала на выходе элемента ИЛИ 14, поступающего на второй вход элемента И 19.

Занятие хотя бы одного блока 30 памяти массивом данных характеризуется наличием единичного сигнала на выходе 11 и характеризует необходимость вывода данных из занятого блока 30 памяти.

Процесс вывода данных осуществляется следующим образом. Во время цикла вьшода (нулевой сигнал на входе 1) выходы данных блоков 30 памят через коммутатор 29 подключаются к выходу 10, выходы элемента И 23 заблокированы, поэтому номер блока 30 памяти определяется кодом счетчика 26. После записи массива данных в первый блок 30 памяти на входы преобразователя 28 кода в циклах вывода поступает нулевой код, т.е. вывод осуществляется из первого блока 30 памяти. Процесс вывода аналогичен процессу ввода (фиг.2). В момен поступления сигнала на вход 7 осуществляется установка триггера 16 в единичное состояние, при этом данные из читаемой ячейки стробиру- ются сигналом И 7 и поступают на выход 10. Если признак вьгеода И 7 поступает в середине цикла вывода (или ввода), то сброс триггера 16 осуществляется задним фронтом сигнала вывода (1-й импульс И 7), если признак вывода поступает в момент изменения режима (2-й импульс И 7), то сброс триггера 16 осуществляется

25691

задш1м фронтом сигнала И 31, следующим после окончания сигнала И 7. Задним фронтом сигнала И 16 содер- с жимое счетчика 17, задающего адрес ячейки вывода блока 30 памяти, изменяется на единицу. Наличие единичного сигнала на выходе 8 служит запретом установки следующего сиг10 нала признака вывода на входе 7.

В момент окончания вывода данных из блока 30 памяти на вход 9 поступает сигнал, увеличивающий содержимое счетчика 26 и уменьшающий содер15 жимое счетчика 21 на единицу. Это означает, что чтение следующего массива производится из следующего блока 30 памяти. Если длина вьгеодимого массива больше емкости одного бло20 ка 30, то в момент переполнения емкости счетчика 17 на выходе переполнения данного счетчика сформируется сигнал, который изменит содержимое счетчиков 21 и 26.

25 Если все блоки 30 памяти заняты, то на выходе переполнения счетчика 21 (выход 5 устройства) сформируется сигнал, который запретит ввод очередного массива данных, пока не

30 освободится хотя бы один блок 30 памяти. Емкость счетчика 26 равна числу блоков 30 памяти. После чтения массива данных из последнего блока 30 осуществляется обнуление счетчика 26, т.е. чтение следующего массива данных осуществляется из первого блока 30 памяти.

Сумматор 27 выполняется следующим образом. Если число блоков 30

MQ памяти кратно степени 2, то сумматор 27 является сумматором по модулю 2. В общем случае модуль суммирования определяется числом блоков памяти 30. Например, для десяти

дс блоков 30 сумматор 27 является сумматором по модулю 10, т.е. десятичным сумматором.

35

Формула изобретения

Устройство сопряжения,содержащее группу блоков памяти, коммутатор данных, коммутатор адреса, счетчик, выбора блока памяти вывода, три элемента И, причем информационный вход/ выход коммутатора данных соединен с информационными входами/выходами блоков памяти группы, выход коммутатора данных является информационным

выходом устройства, выход коммутятс.)- ра адреса соединен с адресными вхоами блоков памяти группы, о т л и- чающееся тем, что с целью повышения пропускной способности устройства за счет увеличения числа подключаемых блоков памяти и сокращения аппаратурных затрат, в него введены пять элементов ИЛИ, два триггера, сумматор, преобразователь кода, элемент НЕ, счетчик адресов ввода, счетчик адресов, вывода и счетчик занятости,, причем первый вход первого элемента И является входом признака конца вввода устройства, второй вход первого элемента И соединен с выходом первого элемента ИЛИ, входы которого соединены с выходами счетчика адреса ввода и с разрядами входа первого направления коммутатора адреса, разряды .входа второго направления которого соединены с выходами счетчика адреса вывода и с входами второго элемента , выход которого соединен с первым входом второго элемента И, второй вход которого является входом Iпризнака конца вывода устройства, Iвыход первого элемента И соединен с Iпервым входом третьего элемента ИЛИ |второй вход которого соединен с выходом переполнения счетчика адреса ввода, счетньй вход которого соеди- 1нен с первым входом третьего эле- |мента И, с выходом разрешения ус- тановки признака ввода устройства и с вькодом первого триггера, вход |установки которого является входом |признака ввода устройства, вход сброса первого триггера соединен с выходом элемента НЕ, вход которого

соединен с входсда сброса второго, триггера, с тактовым входом устройства, с входом управления коммутатора адреса, с BTOpt.D-j входом третьего элемента И, с входами записи/чтения блоков памяти группы и с управляющим входом коммутатора данньсх, информационный вход которого является

информационным входом устройства, выход второго элемента И соединен с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом переполнения счетчика адреса вывода, счетный вход которого соединен с выходом разрешения установки признака вывода устройства и с выходом второго триггера, счетный вход которого является входом

признака вывода устройства, информационный вход второго триггера соединен с выходом разрешения вывода устройства и с выходом пятого элемента HJM, вход которого соединен

с третьим входом третьего элемента И и с выходом счетчика занятости, вычитающий вход которого соединен с выходом четвертого элемента ИЛИ и со счетным входом счетчика выбора

блока памяти вывода, выход которого соединен с первым входом сумматора, второй вход которого соединен с выходом третьего элемента И, выход третьего элемента ИЛИ соединен с суммирующим входом счетчика занятости, выход переполнения которого является вькодом разрешения ввода устройства, выход сумматора соединен с входом преобразователя кoд,oвJ выходы которого соединены с входами выборки блока соответствующих блоков памяти группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления обменом информацией | 1987 |

|

SU1508219A1 |

| Устройство для ввода - вывода информации | 1989 |

|

SU1672430A1 |

| Устройство для ввода-вывода информации | 1988 |

|

SU1536366A1 |

| Устройство для сопряжения N абонентов с М ЭВМ | 1988 |

|

SU1564635A1 |

| Таймер | 1985 |

|

SU1357939A1 |

| Устройство для сопряжения вычислительной машины с магистралью обмена | 1986 |

|

SU1381519A1 |

| Устройство для контроля сбоев псевдослучайного испытательного сигнала | 1987 |

|

SU1540025A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1985 |

|

SU1287170A1 |

| Многоканальное устройство для сопряжения источников информации с вычислительной машиной | 1985 |

|

SU1259274A1 |

| Многоканальное устройство для сопряжения источников информации с вычислительной машиной | 1983 |

|

SU1116423A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении систем памяти ЭВМ и информационно-справочных устройств. Целью изобретения является повьшение пропускной способности устройства за счет увеличения числа подключаемых блоков памяти и сокращения аппаратурных затрат. Изобретение позволяет повысить пропускную способность системы памяти для случая разноскоростных входных и выходные потоков данных, а также для потоков различной интенсивности в мрменты пиковых нагрузок со стороны ввода или вывода. 2 нл.

| Устройство управления доступом к общей памяти | 1977 |

|

SU750490A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР 1177818, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-23—Публикация

1987-02-16—Подача