Изобретение относится к вычис гя- тельной технике, в частности к устройствам сопряжения ЭВМ с абонентами, работающньш по каналам передачи данных, п авто татизированных системах управления, и предназначено для обеспечения автоматического сбора и обработки информации.

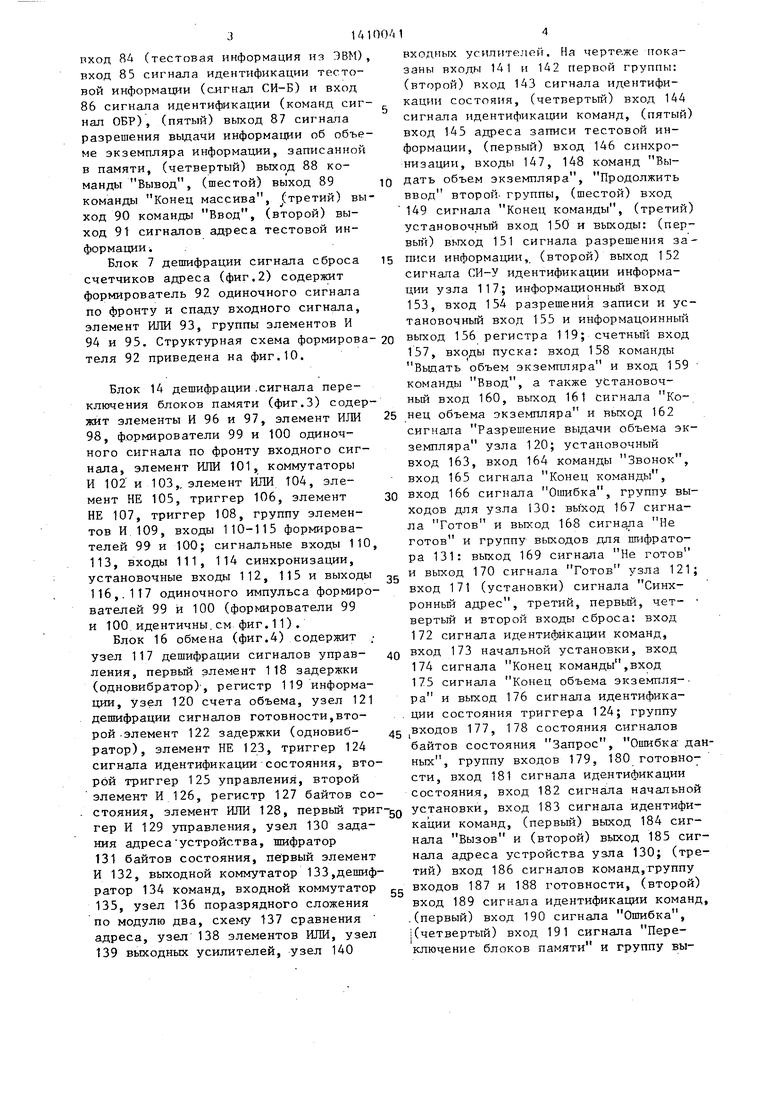

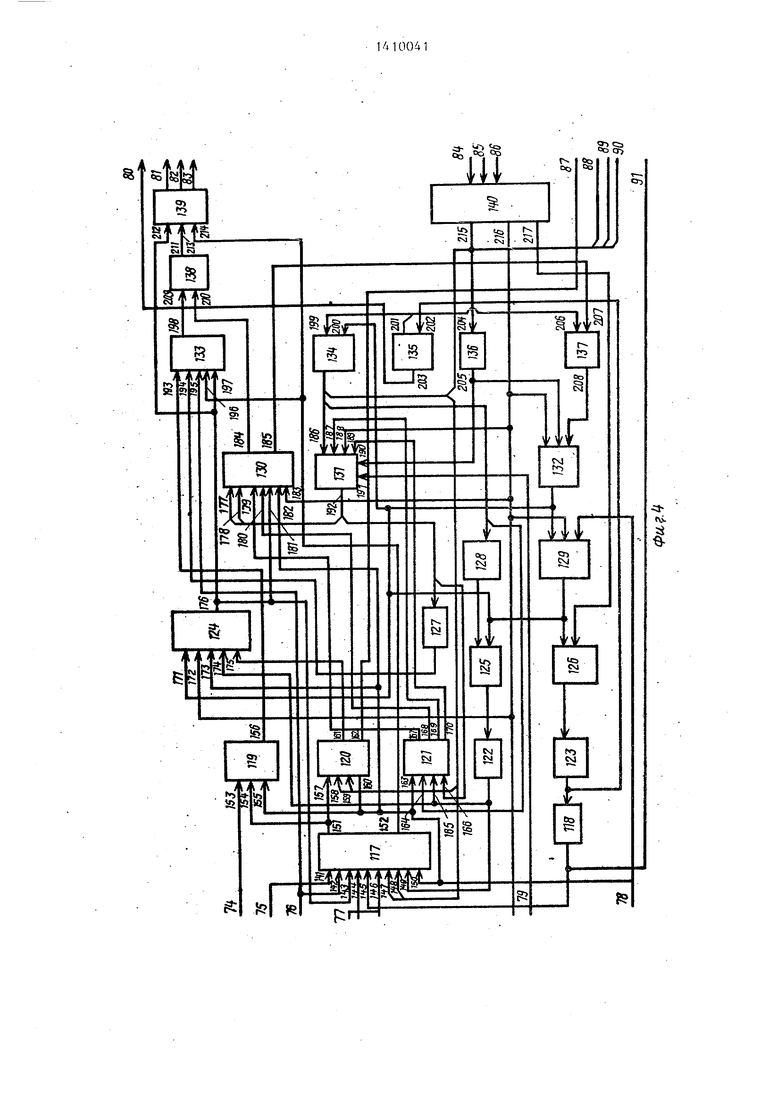

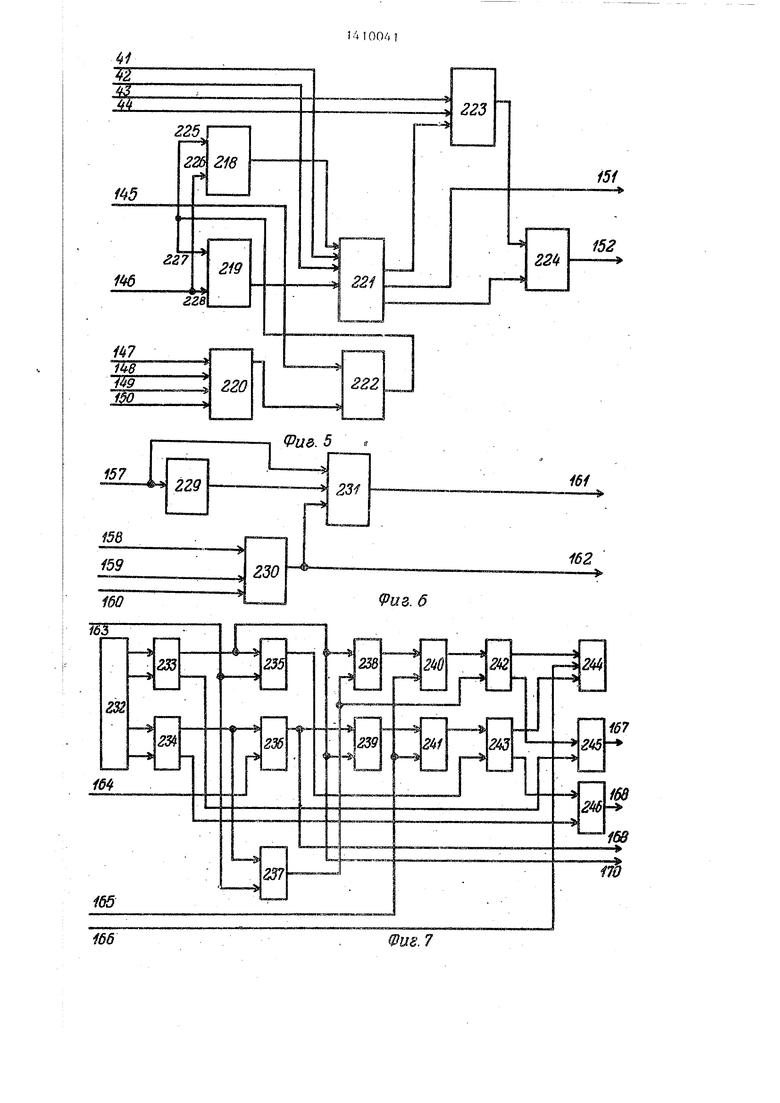

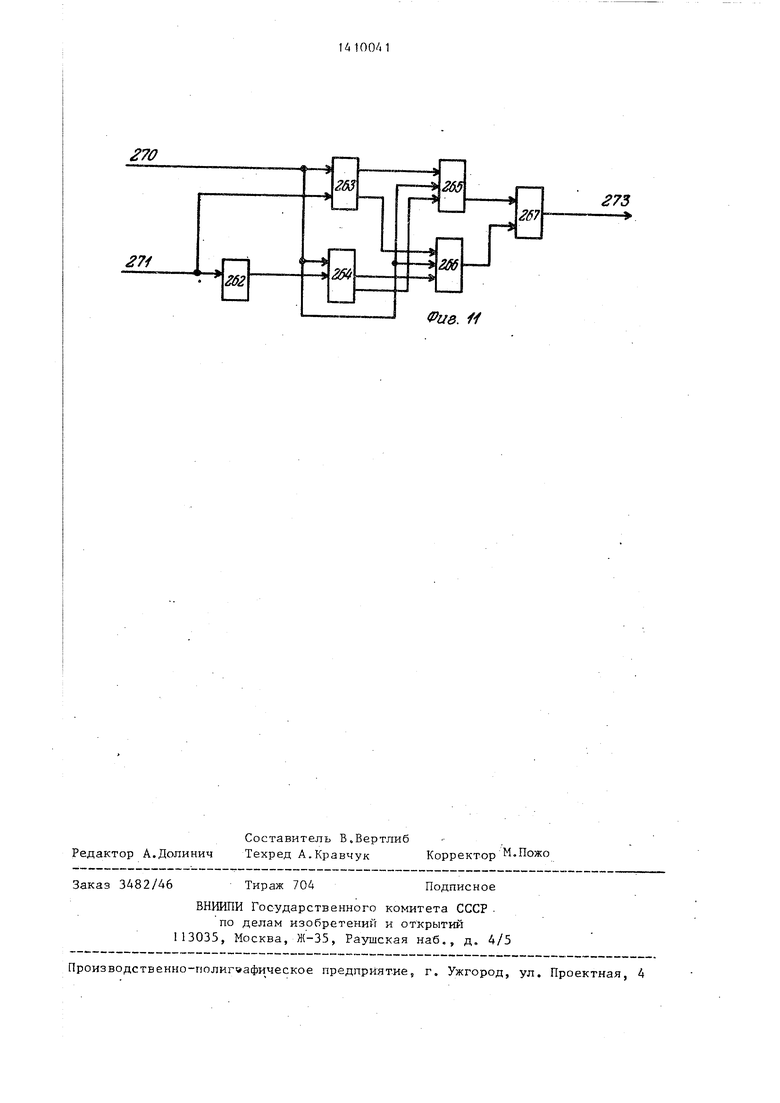

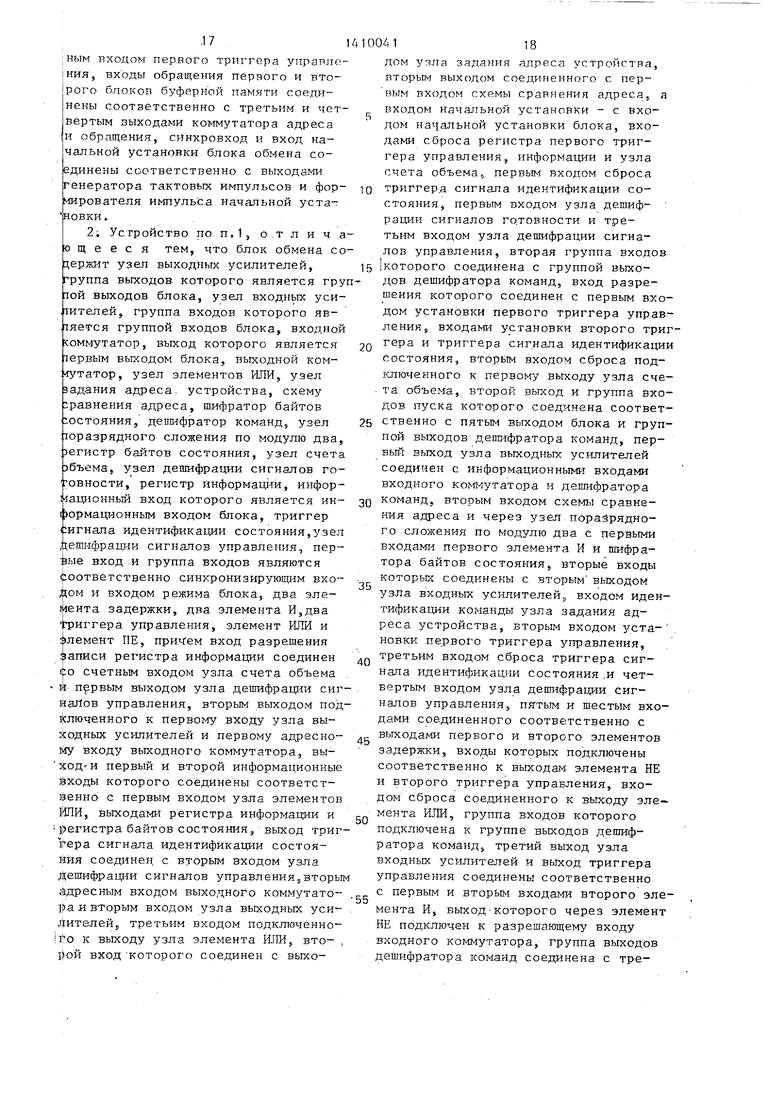

Целью изобретения является повы- шение скорости обмена информацией. На фиг.1 представлена структурная блок-схема устройства;на фиг.2 - 4 - функциональные схемы блока дешифрации сигнала сброса счетчиков адресй, блок дешифрации сигнала переключения блоков памяти и блока обмена; на фиг.5-9 - функциональные схемы узла дешифрации сигналов управления, узла счета объема, узла дешифрации сигналов готовности, триггера сигнала идентификации состояния (ест) и узла задания адреса устройства;на фиг. 10-1 1 - схемы формирователя одиночного сигнала по фронту и спаду входного сигнала и I формирователя одиночного сигнала по I фронту входного сигнала. I Устройство (фиг.1) -содержит блок дешифрации, блок 2 входных усилите- I лей, формирователь 3 импульса началь 1 ной установки, генератор 4 тактовых I импульсов, первый триггер 5 управле- I ния, второй триггер 6 управления,бло I 7 дешифрации сигнала сброса счетчи- I ков адреса, коммутатор 8 адреса и I обращения, коммутатор 9 входной ин- I формации, первый и второй счетчики ; 10, 11 адреса, первый блок 12 буферной памяти, второй блок 13 буферной памяти, блок 14 дешифрации сигнала переключения блоков памяти, комму- татор 15 выходной информации, блок 16 обмена, переключающие входы 17, 18 и вход 19 сброса триггера 5, установочный вход 20, входы 21, 22 и 23 сброса триггера 6; группа входов блока 7 включает: вход 24 команды Вы- вод, вход 23 сигнала Начало текста, вход 26 синхронизации,входы 27 и 28 адреса, коммутации, вход 29 команды Ввод .ход 30 сигнала начальной установки.

. Входы KOMMyTatopa 8 содержат: вхо 31 адреса записи, вход 32 адреса считывания, входы 33, 34 разрешения записи информации в первый или второй блоки памяти (управляющие входы),вхо ды 35 и 36 задания режима работы устройства (адресные входы) (режима

s 0 5 о ,, г

5

0

приема информации от источника информации или режима тестоного контроля) и выходы - выход 37 адреса для блока 12 памяти, выход 38 адреса для блока 13 памяти, выход 39 сигнала обращения для блока 12 памяти, выход 40 сигнала обращения для блока 13 памяти. Входы коммутатора 9 содержат: вход 41 тестовой информации, адресные входы 42 и 43 для задания режима ра--- боты устройства (режима приема информации от источника информации или режима тестового контроля), входы 44, 45 разрешения записи в первой или вто- второй блоки памяти, второй информационный вход 46 (информация от источника информации) ,а также выходы 47, 48 информации в первый и второй блоки памяти. На фиг.1 показаны также информационный вход 49,адресньй вход 50, вход 51 сигнала обращения и выход 52 блока 12 памяти, информационный вход 53, адресный вход 54, вход 55 обращения и информационный выход 56 второго блока 13 памяти, группа входов блока 14, информационные входы 57 и 58 (информация о состоянии разрядов счетчиков 10 и 11), управлякщие входы 59 и 60, вход 61 сигнала Начало текста, установочный вход 62, вход 63 сигнала Конец текста, вход 64 .синхронизации и выход 65 сигнала переключения блоков памяти. Входы коммутатора 15 содержат: информационные входы 66, 67 от первого и второго блоков 12 и 13 памяти, адресные вхо- ды 68 и 69 (разрешения считывания информации из первого или второго блоков памяти), информационные входы 70 и 71 (информация о состоянии первого и второго счетчиков -10 и 11), управ--- ляющий вход 72 разрешения считывания информации об объеме информации, находящейся в памяти,и информационный выход 73. Входы блока 16 содержат: информационный вход 74, входы 73 и 76 режима (разрешение обработки тестовой информации или от источника информации) , вход 77 синхронизации, установочный вход 78. вход 79 состояния и выходы:(первый) информационный выход

80(тестовой информации), группу выходов 81-83; информационный выход

81(в ЭВМ), выход 82 сигнала идентификации информации (сигнал CPf-У) и выход 83 сигнала идентификации состояния устройства (сигнал ССТ), группу входов 84-86; информационньй

3141

вход 84 (тестовая информация из ЭВМ), вход 85 сигнала идентификации тестовой информации (сигнал СИ-Б) и вход 86 сигнала идентификации (команд сиг- нал ОБР), (пятый) выход 87 сигнапа разрешения выдачи информации об объеме экземпляра информации, записанной в памяти, (четвертый) выход 88 команды Вывод , (шестой) выход 89 команды Конец массива, J третий) выход 90 команды Ввод, (второй) выход 91 сигналов адреса тестовой информации .

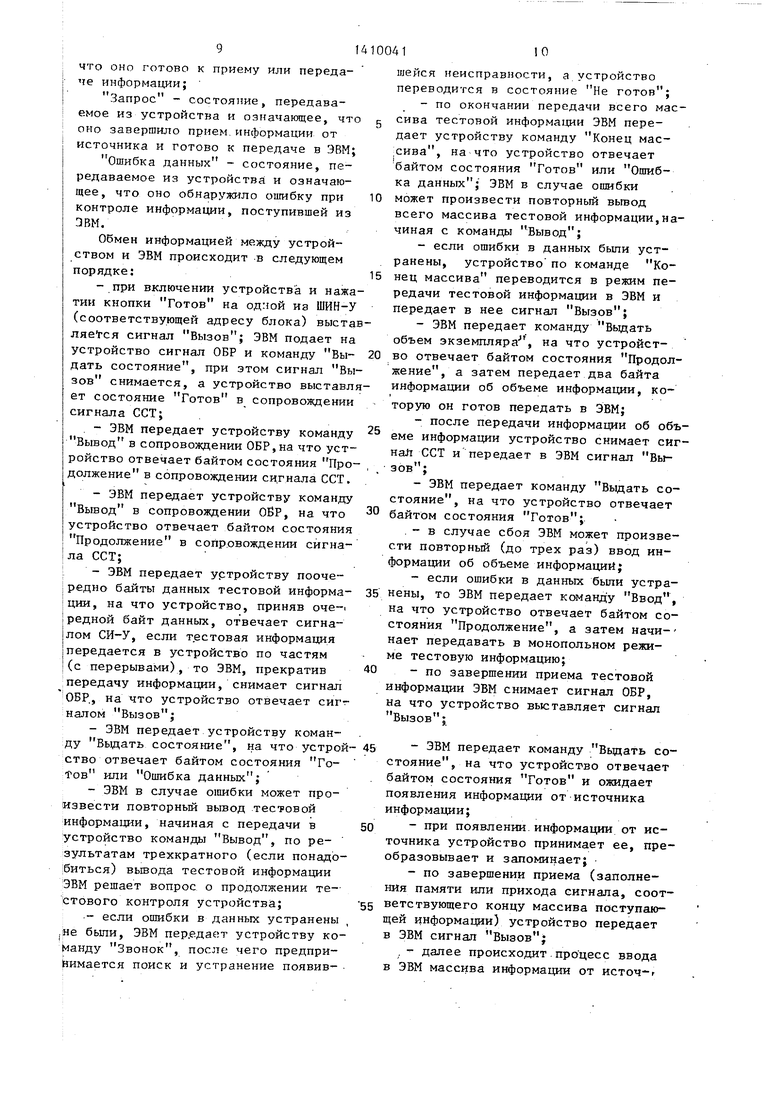

Блок 7 дешифрации сигнала сброса счетчиков адреса (фиг,2) содержит формирователь 92 одиночного сигнала по фронту и спаду входного сигнала, элемент ИЛИ 93, группы элементов И 94 и 95. Структурная схема формирова- теля 92 приведена на фиг.10.

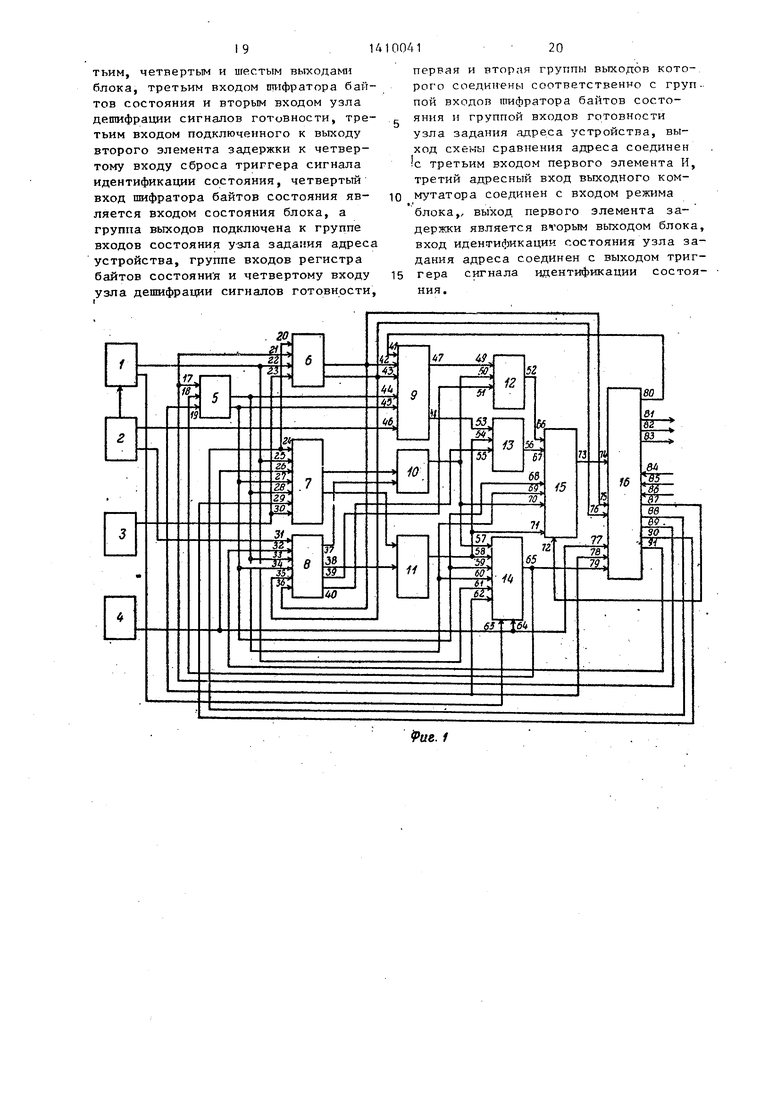

Блок 14 дешифрации .сигнала переключения блоков памяти (фиг.З) содержит элементы И 96 и 97, элемент ИЛИ 98, формирователи 99 и 100 одиночного сигнала по фронту входного сигнала, элемент ИЛИ 101, коммутаторы И 102 и 103,. элемент И ЛИ 104, элемент НЕ 105, триггер 106, элемент НЕ 107, триггер 108, группу элементов И 109, входы 110-115 формирователей 99 и 100; сигнальные входы 110, 113, входы 111, 114 синхронизации, установочные входы 112, 115 и выходы 116,,117 одиночного импульса формирователей 99 и 100 (формирователи 99 и 100 идентичны,см фиг.11).

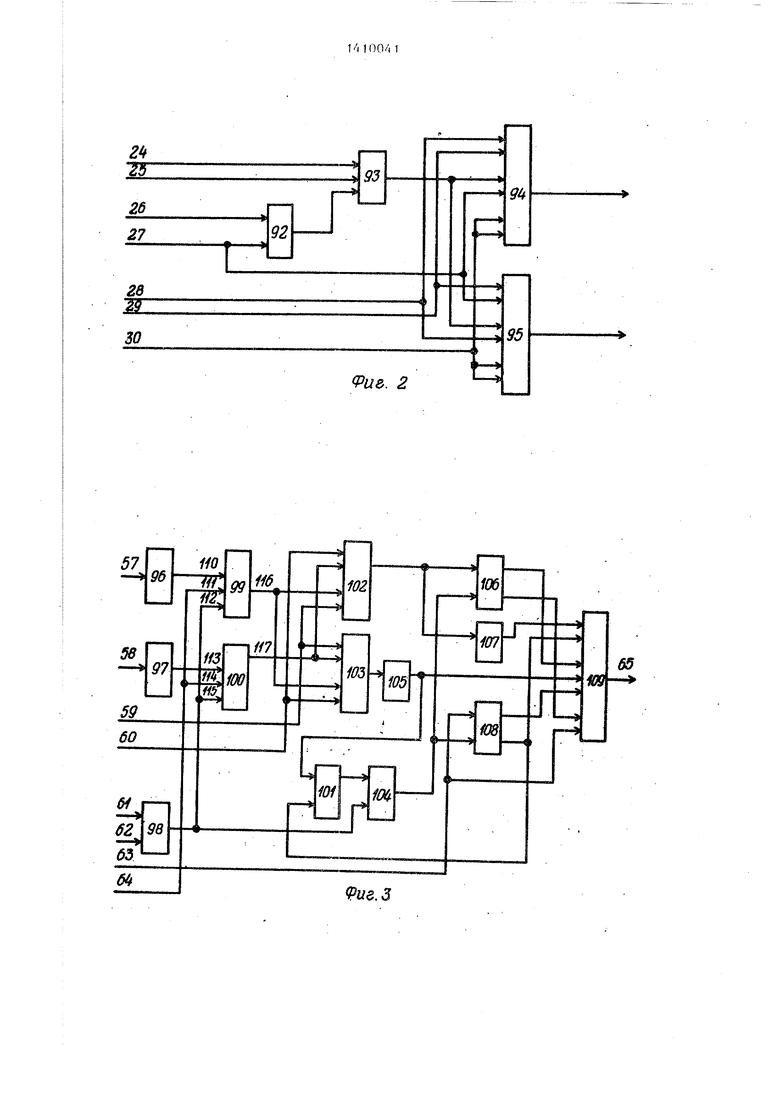

БЛОК 16 обмена (фиг.4) содержит ; узел 117 дешифрации сигналов управ- ления, первый элемент 118 задержки (одновибратор), регистр 119 информации, узел 120 счета объема, узел 121 дешифрации сигналов готовности,второй -элемент 122 задержки (одновиб- ратор), элемент НЕ 123, триггер 124 сигнала идентификации состояния, второй триггер 125 управления, второй элемент И 126, регистр 127 байтов состояния, элемент ИЛИ 128, первый триг гер И 129 управления, узел 130 задания адреса устройства, шифратор 131 байтов состояния, первый элемент И 132, выходной коммутатор 133,дешифратор 134 команд, входной коммутатор 135, узел 136 поразрядного сложения по модулю два, схему 137 сравнения адреса, узел 138 элементов ИЛИ, узел 139 выходных усилителей, узел 140

14

входных усилителей. На чертеже показаны входы 141 и 142 первой группы: (второй) вход 143 сигнала идентификации состояия, (четвертый) вход 144 сигнапа идентификации команд, (пятый) вход 145 адреса записи тестовой информации, (первый) вход 146 синхронизации, входы 147, 148 команд Выдать объем экземпляра, Продолжить ввод второй, группы, (шестой) вход 149 сигнала Конец команды, (третий) установочный вход 150 и выходы: (пер- вьп О выход 151 сигнала разрешения записи информации, (второй) выход 152 сигнала СИ-У идентификации информации узла 117.; информационньш вход 153, вход 154 разрешения записи и установочный вход 155 и информацоинньш выход 156 регистра 119; счетный вход 157, входы пуска: вход 158 команды Вьщать объем экземпляра и вход 159 команды Ввод, а также установочный вход 160, выход 161 сигнала Конец объема экземпляра и выхо/i 162 сигнала Разрешение выдачи объема экземпляра узла 120; установочный вход 163, вход 164 команды Звонок, вход 165 сигнала Конец команды, вход 166 сигнапа Ошибка, группу выходов для узла 130: выход 167 сигнала Готов и выход 168 сигнала Не готов и группу вькодов для шифратора 131: выход 169 сигнала Не готов и выход 170 сигнала Готов узла 121; вход 171 (установки) сигнала Синх- ронньм адрес, третий, первый, чет- вертый и второй входы сброса: вход 172 сигнапа идентификации команд, вход 173 начальной установки, вход

174сигнала Конец команды,вход

175сигнала Конец объема экземпля- ра и выход 176 сигнала идентификации состояния триггера 124; группу входов 177, 178 состояния сигналов байтов состояния Запрос, Оишбка даных, группу входов 179, 180 готовности, вход 181 сигнала идентификации состояния, вход 182 сигнала начальной установки, вход 183 сигнала идентификации команд, (первый) выход 184 сигнала Вызов и (второй) выход 185 сигнала адреса устройства узла 130; (третий) вход 186 сигналов команд,группу входов 187 и 188 готовности, (второй) вход 189 сигнала идентификации команд

.(первый) вход 190 сигнала Ошибка, I (четвертый) вход 191 сигнала Переключение блоков памяти и группу выходов 192 шифратора 131; информационные входы 193 (информация из блоков памяти) и 194 (байты состояния), третий, первый и второй адресные входы 195-197 и выход 198 выходного коммутатора 133; информационный вход 199 (вход 2-8 разрядов входной информации) , вход 200 сигнала разрешения при- приема команд дешифратора 134; информационный вход 20.1 н вход 202 разрешения приема информации и информационньй выход 203 входного коммута тора 135; вход 204 информации и выход 205 контрольного разряда узла 136; (второй) вход 206 (1-3 разрядов) входной информации и первый вход 207 (сигнала адреса устройства), выход 208 схемы 137 сравнения, входы 209, 210 и выход 2 1 1 узла 138; второй, третий и первый входы 212-214 узла 139 и пер- вый-третий входы 215-217 узла 140.

Узел 117 дешифрации сигналов управления (фиг.5) содержит формирователь 218 одиночного сигнала по фронту входного сигнала, формирователь 219 одиночного сигнала по спаду входного сигнала, триггер 220, группу элементов И 221, элемент ИЛИ 222,элемент И 223, триггер 224, входы 225 228: сигнальные входы 225, 227 и входы 226, 228 синхронизации формирователей 218, 219. Структурные схемы формирователей 218, 219 приведены на фиг ЛО и 11.

Узел 120 счета объема (фиг.6) содержит двухразрядный счетчик 229, триггер 230, элемент И 231.

Узел 121 дешифрации сигналов го- товнсоти (фиг.7) содержит наборное поле 232, триггеры 233, 234, элементы ИЛИ 235, 236, 237, триггеры 238, 239, элементы И 240, 241, триггеры 242, 243,. индикатор 244, элементы И 245, 246. Наборное поле 232 состоит из двух кнопок, расположенных на передней панели устройства. Индикатор 244 содержит усилитель на микросхеме и три лампочки индикации (н показаны), регистрирующие наличие сигналов Готов, Не готов, Ошибка.

Триггер 124 сигнала идентификации состояния (фиг,8) состоит из элемента НЕ 247, элемента ИЛИ 248 и триггера 249.

Узел 130 задания адреса устройства (фиг.9) содержит элементы ИЛИ 250, 251, наборное поле 252, триггер 253, элемент И 254, группу элементов И 255.

5

0

5

0

5

0

5

0

5

Наборное поле 252 состоит из восьми тумблеров (не показаны). При включении каждого тумблера выдается сигнал на одну из восьми выходных шин устройства в зависимости от адреса, присвоенного данному устройству в системе, в которую входит указанное устройство;

Формирователь 218 одиночного сигнала по фронту и спаду входного сигнала (фиг.10) содержит элемент НЕ 256, триггеры 257, -258, элементы И 259, 260 и 261.

Формирователь 219 одиночного сигнала по фронту входного сигнала содержит элемент НЕ 262, триггеры 263, 264, элементы И 265, 266, 267.

На чертежах фиг.10, 11 показаны входы 268-271: сигнальные входы 268, 270 формирователей, входы 269, 271 синхронизации, выходы 272, 273.

Устройство выполняет следунлдие функции:

-прием информации от источника информации;

-преобразование п-разрядного параллельного кода, поступающего от источника информации, в восьмиразрядный параллельный код с контрольным разрядом ;

-накопление принятой от источника информации в буферном устройстве памяти;

-передачу накопленной; и|{формации в ЭВМ.

Устройство может работать в двух режимах: тестового контроля; приема информации от источника информации.

Работа устройства происходит в следующем порядке:

а)включение устройства;

б)контроль его работоспособности путем вьгоода в устройство массива тестовой информации из ЭВМ и последукще- го ее ввода в ЭВМ для сравнения с исходной; при положительных результатах контроля устройство готово к работе в режиме приема информации от источника информации;

в)при появлении на входе устройства информации от источника происходит ее автоматический прием (по сигналу начала текста) с последующим преобразованием и записью в память ;

г)по заполнении памяти (или по сигналу конца текста) устройство сопряжения связьшается с ЭВМ и .передает туда накопленный массив йнфор- ма1щи, одновременно осуществляя прием информации от источника и записывая ее в память, этот процесс может длиться до тех пор, пока источник не прекратил передачу информации;

д) если работа с источником информации закончена .и нового поступления информации не ожидается, устройство ю может быть выключено.. j

Обмен информацией между устройством и ЭВМ происходит, например, в соответствии со стандартом ОСТ 4.ГО 304202. На основе указанного ОСТа 15 разработаны диaгpaмм J, определяющие процесс обмена между данным устройством и ЭВМ.

Связь между устройством и ЭВМ осуществляется по 22 шинам, 11 из кото- 20 рых служат для передачи информации от устройства с ЭВМ (называемые ШИН-У), а. другие 11 служат для передачи информации от ЭВМ (называемые ШИН-Б ) в устройство, при этом 18 шин 25 используются для передачи информации, а 4 - для передачи сигналов идентификации.

Сигналы идентификации (называемые СИ-Б, ОБР, СИ-У, ест) используются ЗО для определения вида информации, имеющейся на шинах ШИН-Б и ШИН-У, а также для взаимной блокировки сигналов устройства и ЭВМ.

Сигналы СИ-Б и ОБР определяют тип g информации, передаваемой по 1ИИН-Б. Наличие сигнала ОБР указывает, что на ШИН-Б имеется код адреса устройства, который присвоен ему как абоненту ЭВМ и с которым устанавливается 40 связь и код команды. Передача адреса осуществляется по шинам ШИН-Б1 - ШИН-БЗ (1-3 разряды), передача команды по ШИН. Б4 - ШИН Б8 (4-8 разряды) .- Наличие сигнала СИ-Б в присут- ствии ОБР указывает, что на ШИН-Б имеется код данных.

Сигналы СИ-У и ССТ определяют тип информации, передаваемой по ШИН-У, Наличие сигнала ССТ указывает, что gQ на ШИН-У имеется код состояния. Наличие сигнала СИ-У в присутствии ССТ указывает, что на ШИН-Б имеется код данных. Сигналы ОБР и ССТ, СИ-Б и СИ-У взаимосвязаны: появление сиг- нала ОБР вызывает ответный сигнал ССТ, снятие сигнала ОБР приводит к снятию сигнала ССТ, появление сигнала СИ-Б приводит к появлению сигнала СИ-У и, наоброт, снятие сигнала СИ-Б приводит к снятию сигнала СИ-У. В процессе обмена устройства сопряжения и ЭВМ используются следующие команды и состояния:

Ввод - команда из ЭВМ, по которой устройство начинает ввод информации в ЭВМ;

Продолжить команда из ЭВМ, по которой Устройство возобновляет ввод информации,если был .перерыв по инициативе ЭВМ;

Вывод - команда из ЭВМ, по которой устройство подготавливается к прему тестовой информации и начинает прием данных;

Продолжить вывод - команда из ЭВМ, по которой устройство возобновляет прием тестовой информации, если был перерыв по инициативе ЭВМ;

Конец массива - команда из ЭВМ, по которой устройство завершает прием тестовой информации и подготавливается к ее передаче в ЭВМ;

Вьщать объем экземпляра - команда,, по которой устройство должно передать в ЭВМ данные об объеме информации, находящейся в его памяти и подлежащей передаче в ЭВМ;

Выдать состояние - команда из ЭВМ, по которой устройство должно передать в ЭВМ информацию о своем состоянии;

Звонок - команда из ЭВМ, передаваемая в случае появления ошибок в передаваемой информации, которые не могут быть исправлены автоматически, при условии, что ЭВМ проводит тестовый контроль устройства или закончило прием информации от источника информации; по этой команде устройство прекращает все операщи до вмешательства оператора;

Готов - состояние, передаваемое из устройства и означающее что оно готово к выполнению операции.к к продолжению обмена с ЭВМ после вьтолне- ния предыдущей команды;

,Не готов - состояние, .передаваемое из устройства и означающее,что оно закончило выполнение всех операций; это состояние возникает при поступлении на устройство команды Звонок и при переводе его в это состояние оператором с целью проверки или выключения;

Продолжение - состояние, передаваемое из устройства и означающее.

что оно готово к приему или передаче информации;

Запрос - состояние, передаваемое из устройства и означающее, что оно завершило прием.информации от источника и готово к передаче в ЭВМ;

Ошибка данных - состояние, передаваемое из устройства и означающее, что оно обнаружило оигибку при контроле информации, поступившей из ЭВМ...

Обмен информацией между устройством и ЭВМ происходит в следующем порядке:

-при включении устройства и нажатии кнопки Готов на одной из ШИН-У (соответствующей адресу блока) высталяется сигнал Вызов ; ЭВМ подает на устройство сигнал ОБР и команду Вы- дать состояние, при этом сигнал Вызов снимается, а устройство выставлет состояние Готов в сопровождении сигнала ССТ;

. - ЭВМ передает устройству команду Вывод в сопровождении ОБР,на что устройство отвечает байтом состояния Про должение в сопровождении сигнала ССТ.

-ЭВМ передает устройству команду Вывод в сопровождении СЕР, на что устройство отвечает байтом состояния Продолжение в сопр.овождении сигна ла ССТ;

: - ЭВМ передает уртройству пооче- Iредно байты данных тестовой информа- |ции, на что устройство, приняв оче-i редкой байт данных, отвечает сигналом СИ-У, если тестовая информация передается в устройство по частям (с перерывами), то ЭВМ, прекратив передачу информации, снимает сигнал ОБР., на что устройство отвечает сиг-г налом Вызов ;

-ЭВМ передает устройству команду Вьздать состояние, на что устрой ство отвечает байтом состояния Готов или Ошибка данных ;

-ЭВМ в случае оншбки может произвести повторный вывод тестовой информации, начиная с передачи в устройство команды Вывод, по результатам трехкратного (если понадобиться) вывода тестовой информации

ЭВМ решает вопрос о продолжении тестового контроля устройства;

- если ошибки в данных устранены ,не бьши, ЭВМ пер.едает устройству ко- Манду Звонок, после чего предпринимается поиск и устранение появив-

шейся неисправности, а устройство переводится в состояние Не готов ;

-по окончании передачи всего массива тестовой информа1.щи ЭВМ передает устройству команду Конец массива, на что устройство отвечает байтом состояния Готов или Ошибка данных ; ЭВМ в случае ошибки может произвести повторный вьгеод всего массива тестовой информации,начиная с команды Вывод ;

-если ошибки в данных были устранены, устройство по команде Конец массива переводится в режим передачи тестовой информации в ЭВМ и передает в нее сигнал Вызов ;

-ЭВМ передает команду Вьщать объем экземпляра, на что устройство отвечает байтом состояния Продолжение, а затем передает два байта информации об объеме информации, которую он готов передать в ЭВМ;

-после передачи информации об объеме информации устройство снимает сигнал ССТ и передает в ЭВМ сигнал Вызов ;

-ЭВМ передает команду Вьщать состояние, на что устройство отвечает байтом состояния Готов ;

. - в случае сбоя ЭВМ может произвести повторньш (до трех раз) ввод информации об объеме информации;

-если ошибки в данных были устранены, то ЭВМ передает команду Ввод, на что устройство отвечает байтом состояния продолжение, а затем начинает передавать в монопольном режиме тестовую информацию;

-по завершении приема тестовой информации ЭВМ снимает сигнал ОБР, на что устройство выставляет сигнал Вызов ;

-ЭВМ передает команду Вьщать состояние, на что устройство отвечает байтом состояния Готов и ожидает появления информации от источника информации;

-при появлении, информации от источника устройство принимает ее, преобразовывает и запоминает;

-по завершении приема (заполнения памяти или прихода сигнала, соответствующего концу массива поступающей информации) устройство передает

в ЭВМ сигнал Вызов ;

, - далее происходит. процесс ввода в ЭВМ массива информации от источ- г

П1410041

ника информа1даи, которая аналогична вводу массива тестовой информации.

Устройство работает следующим образом.

При включении источника питания устройства формирователь 3, представляющий собой генератор одиночного импульса, производит вьфаботку определенной длительности, которая при-Ю (вход 51) блока 12 происходит запись

1 2

лем 92, на который поступает сигнал с выхода триггера 5 (вход 27) и тактовых импульсов с генератора 4 (вход 26). С коммутатора 9 информация поступает на блок 12, где происходит запись информации. При одновременном наличии на входах информации (вход 49), адреса (вход 50) и обращения

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения канала ввода-вывода с абонентом | 1989 |

|

SU1695312A1 |

| Устройство для сопряжения датчика информации с электронной вычислительной машиной | 1983 |

|

SU1133590A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Устройство для сопряжения ЭВМ с линиями связи | 1991 |

|

SU1784989A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1988 |

|

SU1536393A1 |

| Многоканальный адаптер | 1987 |

|

SU1495806A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для сопряжения двух магистралей | 1984 |

|

SU1241249A1 |

| Специализированный процессор | 1990 |

|

SU1705834A1 |

| Устройство для сопряжения ЭВМ с внешней памятью | 1987 |

|

SU1515166A1 |

Изобретение относится к вычислительной технике, в частности к устройствам сопряжения ЭВМ с каналами передачи данных, и может быть использовано в автоматизированных системах управления для обеспечения автоматического сбора и обработки информации. Целью изобретения является повышение скорости обмена информации. Поставленная цель достигается тем, что в устройство, содержащее формирователь импульсов начальной установки, два триггера, коммутатор входной информации, первый блок буферной памяти, первый счетчик адреса, коммутатор выходной информации и блок обмена, введены блок входных усилителей, блок дешифрации, генератор -тактовых импульсов, блок дешифрации сигнала сброса счетчиков адреса,коммутатор Адреса и обращения, второй счетчи-к адреса, второй блок буферной памяти и блок шифрации сигнала переключения блоков памяти. 1 з.п. ф-лы, 11 ил. СЛ

водит в исходное состояние узлы устройства.

По сигналу начальной установки, поступающему на.вход триггера 5, происхо.дит переключение коммутаторов 8, 15 вход триггера 5 .(вход 18), сигналы

9 и 15 таким образом, что запись поступающей информации возможна сна - чала в блок 12 памяти. Блок 13 памяти в это время включен на считывание/ Кроме того,сигнал начальной установки производит переключение триггера 6 в положение, обеспечивающее запись информации от источника информации.

Генератор 4 тактовых импульсов производит выработку импульсов синхронизации, необходимых для работы узлов устройства. Коммутатор 8 выдес которого производят переключение коммутаторов, таким образом, что запись поступающей информации возмож- .на в блок 13 памяти. С блока 12 мож

20 производиться считывание информации через коммутатор 15 и блок 16. В ре жиме тестового контроля переключени . блоков 12 (13) происходит с помощью команды Конец массива, которая по

25 ступает на вход триггера 5. В блоке 14 происходит выработка сигнала на . переключение в следующих случаях: при поступлении массива информации, превышающего объем двух блоков 12

25 ступает на вход триггера 5. В блоке 14 происходит выработка сигнала на . переключение в следующих случаях: при поступлении массива информации, превышающего объем двух блоков 12

ляет Из синхросигнала, сопровождающего

каждый байт поступающей информации,сигзо и 13 памяти; при поступлении масси- налы адреса и обращения, которые необ- ва информации в объеме бапьше ем- ходимы для записи информации в блок памяти. Из коммутатора 8 адрес поступает на счетчик 10, который в данное время включен на запись информации. Сигнал обращения с коммутатора 8 поступает непосредственно на блок 12.

кости одного буферного блока,, но .меньше двух; при поступлении массив информации в-объеме меньше одного блока памяти.

Переключение блоков 12 (13) буфер ной памяти осуществляется только при условии полного считывания информации из блока 13(12), находившегося Q в режиме считывания.

Блок 7 производит выработку сигналов сброса счетчиков 10 и 11 в следующих случаях:

а)при включении устройства по сигналу, поступающему с вьпсода формирователя 3 (вход 30);

б)по признаку начала текста, поступающему с выхода блока 1 (вход дс что означает его заполнение.

25),

в) ПО командам ЭВМ: Ввод (вход 29), т.е. перед считыванием информации из заполненного блока 12 (13); . Вьшод (вход 24), т.е. перед записью CQ тестовой информации в блок 12 (13).

Предусмотрен .также сброс счетчика 10 (11) перед записью информации в блок 12 (13), который включен в данное время на запись, и после считьша- цс НИН информации из блока 13 (12), находившегося в режиме считывания. Указанный режим осуществляется путем формирования импульсов формироватеэлемент И 96 или 97 сформирует сиг- нал, который поступает на один из формирователей 99 или 100 для формирования одиночного сигнала по фронту входного сигнала. Сигнал, полученный побле формирователей 99 , свидетельствующий о заполнении одного из блоков 12 (13) памяти, поступает на коммутатор 1Q2, .где в качестве коммутирующих сигналов используются сигналы с выходов триггера 5. С выхода коммутатора 102 сигнал переключения поступает через элемент НЕ 107 на вход группы элементов И 109 и далее

каждого байта в память.

По заполнении памяти или по признаку конца текста блок 14 вырабатывает сигнал, поступающий на счетный

с которого производят переключение коммутаторов, таким образом, что запись поступающей информации возмож- .на в блок 13 памяти. С блока 12 может

производиться считывание информации через коммутатор 15 и блок 16. В режиме тестового контроля переключение блоков 12 (13) происходит с помощью команды Конец массива, которая поступает на вход триггера 5. В блоке 14 происходит выработка сигнала на переключение в следующих случаях: при поступлении массива информации, превышающего объем двух блоков 12

и 13 памяти; при поступлении масси- ва информации в объеме бапьше ем-

о и 13 памяти; при поступлении масси- ва информации в объеме бапьше ем-

кости одного буферного блока,, но .меньше двух; при поступлении массива информации в-объеме меньше одного блока памяти.

Переключение блоков 12 (13) буферной памяти осуществляется только при условии полного считывания информации из блока 13(12), находившегося Q в режиме считывания.

В первом случае происходит анализ состояния выходов счетчиков 10 и 11 на элементах И 96 и 97. Если все раз- .ряды счетчика 10 или 11 примут значе что означает его заполнение.

элемент И 96 или 97 сформирует сиг- нал, который поступает на один из формирователей 99 или 100 для формирования одиночного сигнала по фронту входного сигнала. Сигнал, полученный побле формирователей 99 , свидетельствующий о заполнении одного из блоков 12 (13) памяти, поступает на коммутатор 1Q2, .где в качестве коммутирующих сигналов используются сигналы с выходов триггера 5. С выхода коммутатора 102 сигнал переключения поступает через элемент НЕ 107 на вход группы элементов И 109 и далее

3,

на выход блока. Сигнал с выхода ком- : мутатора 102 переключает триггер I 106, тем самым обеспечивая запрет на I прохождение сигнала Конец текста ;для того, чтобы не произошпо пере- ключьение блока 13 памяти раньше, чем закончилось считывание из блока 12, находив-шегося в режиме считывания. Во втором случае поступление сигнала Конец текста возможно раньше, чем произопшо считывание из блока 12 памяти. В этом случае для обеспечения своевременного переключения памяти сигнал Конец текста запоминается на триггере 108 и при поступлении сигнала о конце считывания с коммутатора 103 на элементы И 109 происходит выработка сигнала на переключение блоков 12 (13) памяти. При поступлении массива информации в объеме меньше одного блока 12 (13) сигнал Конец текста поступает со вто5

10

15

20

рого выхода блока 1 на вход блока 14 .непосредственно на элементы И 109, обеспечивая выработку сигнала переключения.

Блок 16 обмена работает в трех режимах:

-включения и логического подключения к ЭВМ;

-тестового контроля;

-приема информации от источника информации.

При включении устройства на блок 16 обмена поступает сигнал начальной установки, устанавливающий его элементы в исходное состояние. При нажатии кнопки Готов узел 121 выдает сигнал, поступающий на шифратор 131 байтов состояний и узел 130 для подготовки байта состояния Готов и сигнала Вызов. Сформированный

байт состояния Готов хранится в регистре 127 байтов состояния. Если на входной шине ОБР нет сигнала, то сигнал Вызов через узлы 138 и. 139 поступает на ШН-У, соответствующего адресу данного устройства, который установлен на наборном поле 252. Под- ключение устройства к ЭВМ начинается с команды Выдать состояние в сопро- вождении сигнала идентификации ОБР, По которому сигнал Вызов снимается. Расшифровка поступающих на уст- 1 ойство команд происходит с помощью |;ешифраторов 134 и 137. При совпадении адреса поступившей команды с адресом устройства схема 137 сравнения вьща25

14100Д114,

от разрешакщий сигнал, по которому дешифратор 13А расшифровывает поступившую команду. Расшифрованная команда используется для формирования байта состояния, а сигнал с вьгхода элемента И 132 поступает на триггер 124 для формирования сигнала идентификации ест. Получив байт состояния, ЭВМ снимает команду и сигнал ОБР.При снятии команды на выходе элемента 122 формируется сигнал Конец команды, который поступает на триггер 124,что ведет к снятию байта состояния с 111ИН-У. После этого ЭВМ проводит тестовую проверку устройства, производя вывод в устройство и ввод из него массива тестовой информации с помощью команд Вывод, Продолжить вывод, Конец массива. При поступлении команды Вьгоод в сопровождении ОБР устройство формирует и передает в ЭВМ байт состояния Продолжение в сопровождении ССТ. После снятия команды Вывод с ШИН-Б с ШИН-У снимается байт состояния, а на входные шины ШИН-Б поступает байт тесто- |вой информации в сопровождении сигнала идентификации СИ-Б, При этом на .выходе элемента 118 формируется сиг- нал СИ-Б1, который поступает на вы- ход 91 и далее на коммутатор 8 и используется, как адрес для записи тестовой информации в блок 12 (13), на выходе триггера 129 формируется iCHPHan, поступающий на коммутатор 135, как сигнал разрешения прохождения входной информации. Одновременно снгнал с выхода элемента 118 поступает на вход узла 117, где по фронту поступившего сигнала с помощью формирователя,207 формируется ответньй сигнал СИ-У. Приняв сигнал СИ-У ЭВМ снимает байт данных с ШИН-Б и сигнал СИ-Б. При снятии устройство снимает сигнал СИ-У. После этого ЭВМ выставляет на ШИН-Б очередной байт данных в сопровождении СИ-Б. В случае ошибки в байте дан- чых сигнал ошибки .с узла 136 поступает на шифратор 131 для формирования байта состояния Ошибка данных, приняв который, ЭВМ может повторить вьшод тестовой информации. Если при трехразовом повторе ошибка не устра30

35

40

45

50

55

няется, то ЭВМ пёредает команду Звонок, поступагаций -на узел 121 с дешифратора 134, при принятии которой устоойство формирует байт состояния

от разрешакщий сигнал, по которому дешифратор 13А расшифровывает поступившую команду. Расшифрованная команда используется для формирования байта состояния, а сигнал с вьгхода элемента И 132 поступает на триггер 124 для формирования сигнала идентификации ест. Получив байт состояния, ЭВМ снимает команду и сигнал ОБР.При снятии команды на выходе элемента 122 формируется сигнал Конец команды, который поступает на триггер 124,что ведет к снятию байта состояния с 111ИН-У. После этого ЭВМ проводит тестовую проверку устройства, производя вывод в устройство и ввод из него массива тестовой информации с помощью команд Вывод, Продолжить вывод, Конец массива. При поступлении команды Вьгоод в сопровождении ОБР устройство формирует и передает в ЭВМ байт состояния Продолжение в сопровождении ССТ. После снятия команды Вывод с ШИН-Б с ШИН-У снимается байт состояния, а на входные шины ШИН-Б поступает байт тесто- |вой информации в сопровождении сигнала идентификации СИ-Б, При этом на .выходе элемента 118 формируется сиг- нал СИ-Б1, который поступает на вы- ход 91 и далее на коммутатор 8 и используется, как адрес для записи тестовой информации в блок 12 (13), на выходе триггера 129 формируется iCHPHan, поступающий на коммутатор 135, как сигнал разрешения прохождения входной информации. Одновременно снгнал с выхода элемента 118 поступает на вход узла 117, где по фронту поступившего сигнала с помощью формирователя,207 формируется ответньй сигнал СИ-У. Приняв сигнал СИ-У ЭВМ снимает байт данных с ШИН-Б и сигнал СИ-Б. При снятии устройство снимает сигнал СИ-У. После этого ЭВМ выставляет на ШИН-Б очередной байт данных в сопровождении СИ-Б. В случае ошибки в байте дан- чых сигнал ошибки .с узла 136 поступает на шифратор 131 для формирования байта состояния Ошибка данных, приняв который, ЭВМ может повторить вьшод тестовой информации. Если при трехразовом повторе ошибка не устра5

няется, то ЭВМ пёредает команду Звонок, поступагаций -на узел 121 с дешифратора 134, при принятии которой устоойство формирует байт состояния

J.

He готов. Если весь массив тестовой информации принят без ошибок,, устройство формирует байт состояния Готов, а узел 130 формирует сигна Вызов. В ответ на поступившую команду Выдать состояние. в сопровождении сигнала ОБР устройство снимает сигнап Вызов и выставляет на ШИН-У байт состояния Готов в сопровождении сигнала ССТ. ЭВМ, приняв байт состояния, снимает команду и сигнал ОБР, а устройство снимает бай состояния и сигнал ССТ. О том, что передан весь массив информации, ЭВМ подтверждает командой Конец масси- на, на что шифратор 131 формирует байт состояния Запрос, а на выходную шину ШИН-У выставляется сигнал Вызов, т.е. устройство готово к передаче принятой тестовой информации.

Формула изобретения

10041 - 16

сброса пторого триггера упраплеиия соединен с первым BiirxonoM блока депгиф ращш, входом соединенного с первым с выходок блока входных усилителей, второй выход которого подключен к второму информационному входу коммутатора входной информации, группа адресных входов которого соединена с выходами

10 первого и второго триггеров управления, а второй выход - с информационным входом второго блока буферной памяти, адресный вход и выход которого подключены соответственно к выходу

15 второго счетчика адреса и второму информационному входу коммутатора выходной информации, третий и четвертый- информаш1онные входы которого подключены соответственно к выходам перво20 го и второго счетчиков адреса, а адресный вход - к выходу первого триггера управления и разрешающему входу коммутатора адреса и обращения, адресный вход которого соединен с выхо25

дом второго триггера управления, а

первый и второй информационные входы - соответственно с третьим выходом, блока входных усилителей и вторым выходом блока обмена, вход режима которого подключен к выходу второго триггера управления, а вход состояния - к счетному входу первого триггера управления и выходу блока дешифрации сигнала переключения блоков памяти, группа входом которого соединена с выходами первого и второго счетчиков адреса, первого триггера управления, первым и вторым выходами блока дешифрации, выходами формирователя

импульса начальной установки и генератора тактовых импульсов, счетные входы и входы сброса первого и второго счетчиков адреса соединены соответственно с первым и вторым вьгхогг,

дами блока дешифрации сигналов сброса счетчиков адреса, группа входов которого подключена к выходам первого тригг ера управления, формирователя импУльса начальной установки, генеразора тактовых импульсов, первому выходу блока дешифрации, третьему и четвертому выходам блока обмена, пятый и четвертый выходы которого соединены соответственно с управляюЩим входом коммутатора выходной информации и установочньм входом второго триггера управления, а шестой выход - с третьим входом сброса второго триггера управления и установоч.17I

ным входом первого триггера управления, входы обращения первого и второго блоков буферной памяти соединены соответственно с третьим и четвертым выходами коммутатора адреса и обращения, сйнхровход и вход начальной установки блока обмена соединены соответственно с выходами генератора тактовых импульсов и формирователя импульса начальной уста- новки.

2; Устройство по п,1, о-Т л и ч а о щ е е с я тем, что блок обмена со з;ержит узел выходных усилителей, группа выходов которого является групой выходов блока, узел входньтх усилителей, группа входов которого является группой входов блока, входной коммутатор, выход которого является тервым выходом блока, выходной ком- чутатор, узел элементов РШИ, узел задания адреса, устройства, схему сравнения адреса, шифратор байтов состояния, деимфратор команд, узел лоразрядного сложения по модулю два, :эегистр байтов состояния, узел счета збъема, узел дешифрации сигналов готовности, регистр информации, информационный вход которого является ин- оормационным входом блока, триггер сигнала идентификации состояния,узел ,|1;ешифрации сигналов управления, пер- :Ьые вход .и группа входов являются Соответственно синхронизирующим вхо- ом и входом режима блока5 два эле- liieHTa задержки, два элемента И,два Диггера управления, элемент ИЛИ и Элемент , прич ем вход разрешения фаписи регистра информации соединен фо счетным входом узла счета объема Ill первым выходом узла дешифрации сиг йаЛов управления, вторым выходом подключенного к первому входу узла выходных усилителей и первому адресно- liiy входу выходного коммутатора, вы- ЖОД И первый и второй информационные йходы которого соединены соответственно с первым входом узла элементов 1ПИ, выходами регистра информации и егистра байтов состояния, выход триг ера сигнала идентификации состоя- ййя соединен, с вторым входом узла Дешифрации сигнапов управления,вторы адресным входом выходного коммутато- ра и вторым входом узла выходных уси- Лителей, третьим входом подклгаченно- к выходу узла элемента И.ПИ, вто- Йой вход которого соединен с выхо

4118

дом узла задания адреса устройства, вторым выходом соединенного с первым входом схемы сравнения адреса, а входом начальной установки - с входом начальной установки блока, входами сброса регистра первого триггера управления, информации и узла счета объема5 первым входом сброса

триггерд сигнала идентификации состояния, первьгм входом узла дешиф- рации сигналов готовности и третьим входом узла дешифрации сигналов управления, вторая группа входов

JKOToporo соединена с группой выходов дешифратора команд, вход разрешения которого соединен с первым входом установки первого триггера управ.- ления, входами установки второго триггера и триггера сигнала идентификации состояния., вторым входом сброса подключенного к первому выходу узла сче- . та объема, второй выход и группа входов пуска которого соединена соответственно с пятым выходом блока и группой выходов дешифратора команд, первый выход узла выходных усилителей соединен с информационными входами входного коьмутатора и дешифратора

команд, вторым входом схемы сравнения адреса и через узел поразрядного сложения по модулю два с первыми входами первого элемента И и шифратора байтов состояния, вторые входы которых соединень с вторым выходом узла входных усилителей,, входом идентификации команды узла задания адреса устройства, вторым входом уста- новкк первого триггера управления, третьим входом сброса триггера сигнала идентификации состояния .и чет- вертьм входом узла дешифрации сигналов управления, пятым и шестым входами соединенного соответственно с выходами первого и второго элементов задержки, входы которых подключены соответственно к выходам элемента НЕ и второго триггера управления, входом сброса соединенного к выходу элемента ИЛИ, группа входов которого подключена к группе выходов дешифратора команд, третий выход узла входных усилителей и выход триггера управления соединены соответственно с первым и вторьгм входами второго элемента И, выходкоторого через элемент НЕ подключен к разрешающему входу входного коммутатора, группа выходов дешифратора команд соединена с тре

тьим, четвертью и шестым выходами блока, третьим входом пп-гфратора байтов состояния и вторым входом узла дешифрации сигналов готовности, третьим входом подключенного к выходу второго элемента задержки к четвертому входу сброса триггера сигнала идентификации состояния, четвертый вход шифратора байтов состояния является входом состояния блока, а группа выходов подключена к группе входов состояния узла задания адрес устройства, группе входов регистра байтов состояния и четвертому входу узла дешифрации сигналов готовности

первая и вторая группы выходов которого соедин-ены соответственно с группой входов нтафратора байтов состояния и группой входов готовности узла задания адреса устройства, выход схемы сравнения адреса соединен с третьим входом первого элемента И, третий адресный вход выходного коммутатора соединен с входом режима блока,, выход первого элемента задержки является вторым выходом блока, вход идентификации состояния узла задания адреса соединен с выходом триггера сигнала идентификации состояния.

э- iD fe

rv. rVx

Я is OD CD

iPue. 8

| Устройство для сопряжения | 1978 |

|

SU752321A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство сопряжения | 1976 |

|

SU602934A1 |

Авторы

Даты

1988-07-15—Публикация

1986-12-23—Подача