/lottl В (ь f то 2 Порту

Фиг 1

порту, выход 5 подтверждения ввода по второму порту / вывода по первому порту, первую Р-разрядную информационную шину 6, где Р - разрядность данных первого

порта, Р - МХК, К 2 п 0, 1, 2вход 7

признака обмена по первому порту, вход 8 признака конца обмена по первому порту, третий элемент И 9, первый (К-разрядный) кольцевой регистр 10, первый счетчик 11 адреса, первый элемент ИЛИ 12, первый элемент И 13, второй элемент ИЛИ 14, второй (N-разрядный) кольцевой регистр 15, четвертый элемент И 16, второй счетчик 17 адреса (первого порта), четвертый элемент

ИЛИ 18, второй элемент И 19, пятый элемент ИЛИ 20, третий (N-рязрядный) кольцевой регистр 21, группу элементов И 22, первый счетчик занятости 23, третий элемент ИЛИ 24, N блоков хранения данных 25, пятый 26, шестой 27, седьмой 28, восьмой 29 элементы И, шестой 30, седьмой 31 элементы ИЛИ, первый 32 и второй 33 триггеры, девятый 34 элемент ИЛИ, второй счетчик занятости 35, восьмой 36 элемент ИЛИ, вход 37 требования ввода по первому порту, вход 38 требования ввода по второму порту, десятый 39 и одиннадцатый 40 элементы ИЛИ, 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительной машины с магистралью обмена | 1986 |

|

SU1381519A1 |

| Устройство для сопряжения N абонентов с М ЭВМ | 1988 |

|

SU1564635A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1837305A1 |

| Устройство для ввода-вывода информации | 1988 |

|

SU1536366A1 |

| Устройство для управления обменом информацией | 1987 |

|

SU1508219A1 |

| Устройство для обмена данными между оперативной памятью и внешними устройствами | 1985 |

|

SU1295404A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для отладки программно-аппаратных блоков | 1983 |

|

SU1242965A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах обмена данными в качестве устройства сопряжения различных по скоростным характеристикам источников и приемников информации и обеспечивает последовательный доступ к ячейкам памяти при обмене между источником и приемником информации. Целью изобретения является расширение области применения устройства за счет обеспечения двунаправленного обмена информацией. Устройство ввода-вывода информации содержит выход 1 подтверждения ввода по первому порту/вывода по второму порту, вторую м-разрядную информационную шину 2, где м-разрядность данных второго порта, вход 3 признака обмена по второму порту, вход 4 признака конца обмена по второму порту, выход 5 подтверждения ввода по второму порту/вывода по первому порту, первую р-разрядную информационную шину 6, где р-разрядность данных первого порта, р = МХК, К = 2P, P = 0, 1, 2, ..., вход 7 признака обмена по первому порту, вход 8 признака конца обмена по первому порту, третий элемент И 9, первый (К-разрядный) кольцевой регистр 10, первый счетчик 11 адреса, первый элемент ИЛИ 12, первый элемент И 13, второй элемент ИЛИ 14, второй (N - разрядный) кольцевой регистр 15, четвертый элемент И 16, второй счетчик 17 адреса (первого порта), четвертый элемент ИЛИ 18, второй элемент И 19, пятый элемент ИЛИ 20, третий (N - разрядный) кольцевой регистр 21, группу элементов И 22, первый счетчик занятости 23, третий элемент ИЛИ 24, N блоков хранения данных 25, пятый 26, шестой 27, седьмой 28, восьмой 29 элементы И, шестой 30, седьмой 31 элементы ИЛИ, первый 32 и второй 33 триггеры, девятый 34 элемент ИЛИ, второй счетчик занятости 35, восьмой 36 элемент ИЛИ, вход 37 требования ввода по первому порту, вход 38 требования ввода по второму порту, десятый 39 и одиннадцатый 40 элементы ИЛИ. 2 ил.

Изобретение относится к вычислительной технике, может быть использовано в системах обмена данными в качестве устройства сопряжения различных по скоростным характеристикам источников и приемников информации и обеспечивает последовательный доступ к ячейкам памяти при обмене между источником и приемником информации.

Целью изобретения является расширение области применения устройства за счет обеспечения двунаправленного обмена информацией.

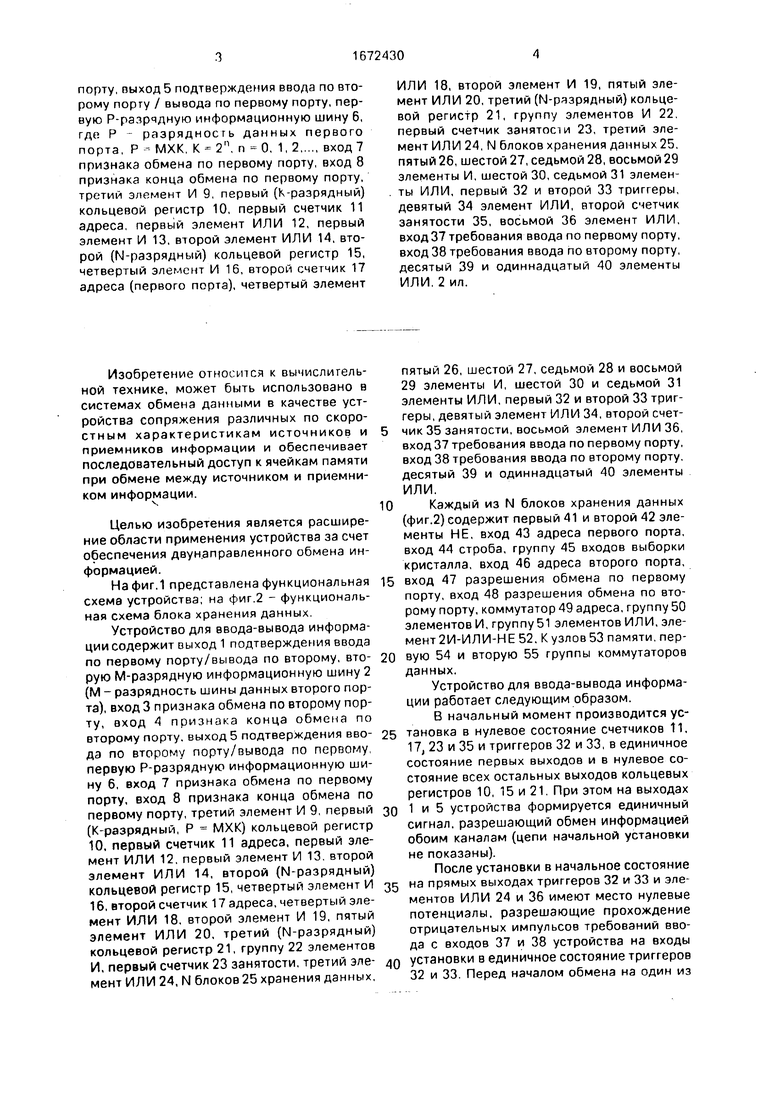

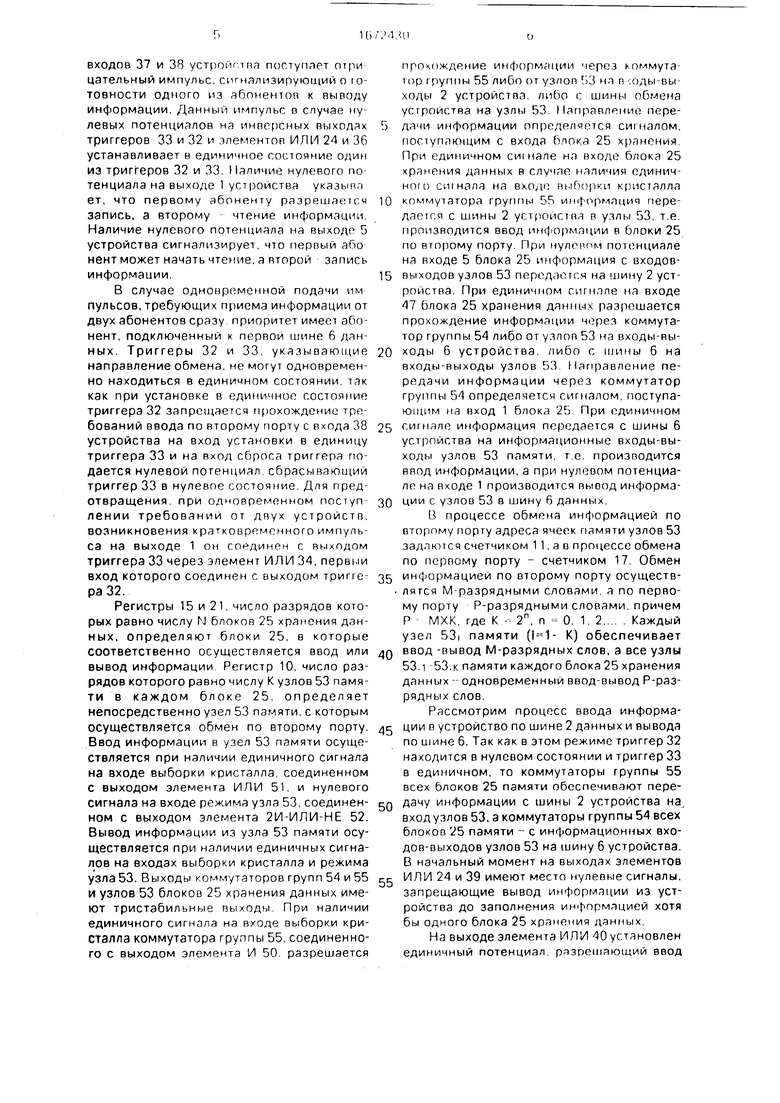

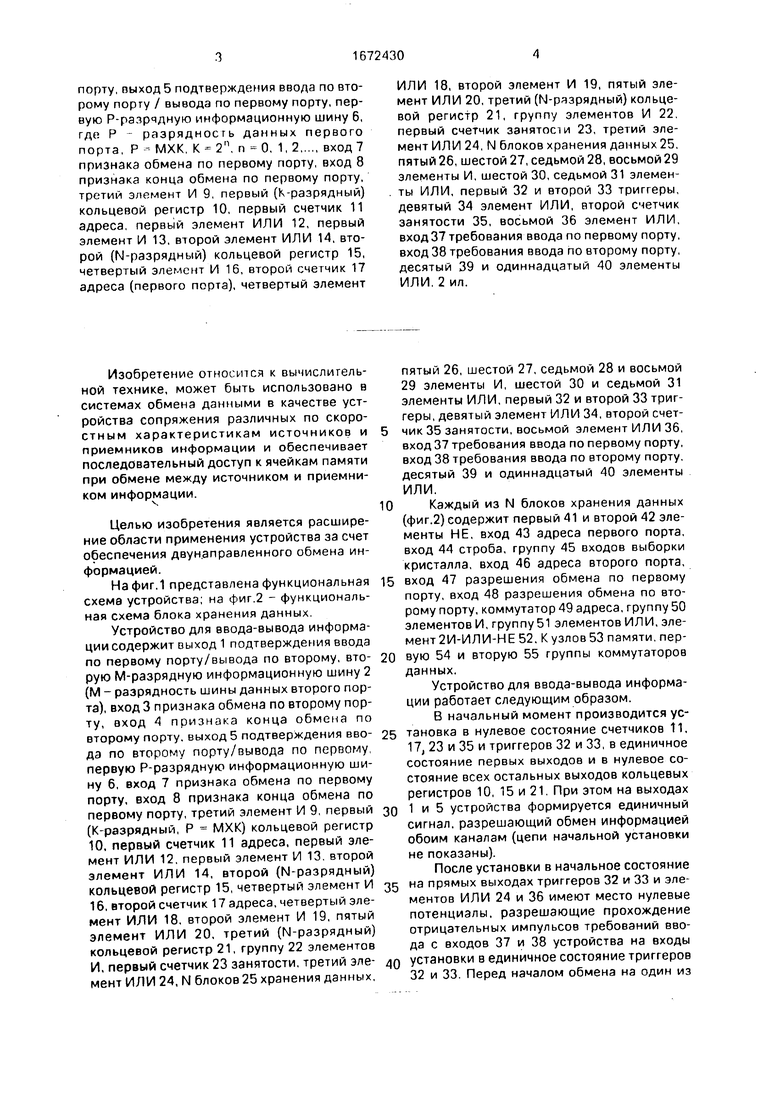

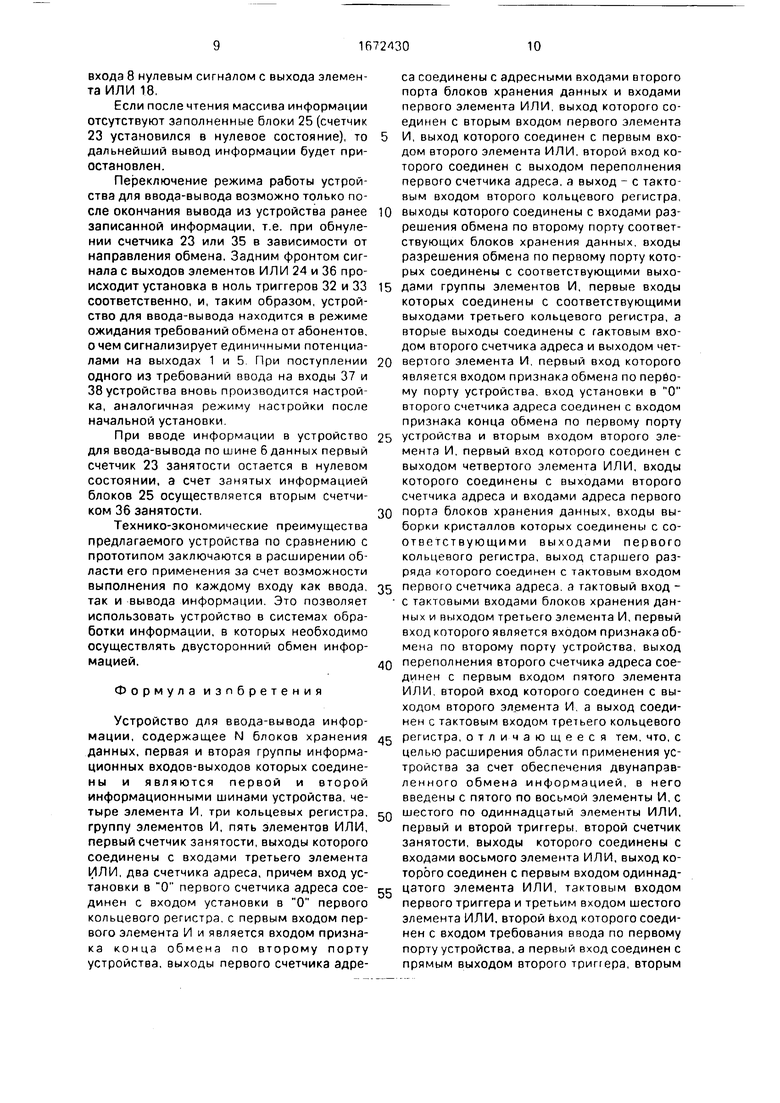

На фиг.1 представлена функциональная схема устройства; на фиг.2 - функциональная схема блока хранения данных

Устройство для ввода-вывода информации содержит выход 1 подтверждения ввода по первому порту/вывода по второму, вторую М-разрядную информационную шину 2 (М - разрядность шины данных второго порта), вход 3 признака обмена по второму порту, вход 4 признака конца обмена по второму порту, выход 5 подтверждения ввода по второму порту/вывода по первому первую Р-разрядную информационную шину 6, вход 7 признака обмена по первому порту, вход 8 признака конца обмена по первому порту, третий элемент И 9, первый (К-разрядный, Р МХК) кольцевой регистр 10, первый счетчик 11 адреса, первый элемент ИЛИ 12, первый элемент И 13, второй элемент ИЛИ 14, второй (N-разрядный) кольцевой регистр 15, четвертый элемент И 16, второй счетчик 17 адреса, четвертый элемент ИЛИ 18, второй элемент И 19, пятый элемент ИЛИ 20, третий (N-разрядный) кольцевой регистр 21, группу 22 элементов И, первый счетчик 23 занятости, третий элемент ИЛИ 24, N блоков 25 хранения данных,

пятый 26, шестой 27, седьмой 28 и восьмой 29 элементы И, шестой 30 и седьмой 31 элементы ИЛИ, первый 32 и второй 33 триггеры, девятый элемент ИЛИ 34, второй счетчик 35 занятости, восьмой элемент ИЛИ 36, вход 37 требования ввода по первому порту, вход 38 требования ввода по второму порту, десятый 39 и одиннадцатый 40 элементы ИЛИ.

Каждый из N блоков хранения данных

(фиг.2) содержит первый 41 и второй 42 элементы НЕ, вход 43 адреса первого порта, вход 44 строба, группу 45 входов выборки кристалла, вход 46 адреса второго порта,

вход 47 разрешения обмена по первому порту, вход 48 разрешения обмена по второму порту, коммутатор 49 адреса, группу 50 элементов И, группу 51 элементов ИЛИ, элемент 2И-И Л И-НЕ 52. К узлов 53 памяти, первую 54 и вторую 55 группы коммутаторов данных.

Устройство для ввода-вывода информации работает следующим образом.

В начальный момент производится установка в нулевое состояние счетчиков t1. 17, 23 и 35 и триггеров 32 и 33, в единичное состояние первых выходов и в нулевое состояние всех остальных выходов кольцевых регистров 10, 15 и 21. При этом на выходах

1 и 5 устройства формируется единичный сигнал, разрешающий обмен информацией обоим каналам (цепи начальной установки не показаны).

После установки в начальное состояние

на прямых выходах триггеров 32 и 33 и элементов ИЛИ 24 и 36 имеют место нулевые потенциалы, разрешающие прохождение отрицательных импульсов требований ввода с входов 37 и 38 устройства на входы

установки в единичное состояние триггеров 32 и 33. Перед началом обмена на один из

входов 37 и 38 устройства поступает отри цательный импульс, сигнализирующий о готовности одного из абонентов к выводу информации. Данный импульс в случае нулевых потенциалов на инверсных выходах триггеров 33 и 32 и элементов ИЛИ 24 и 36 устанавливает в единичное состояние один из триггеров 32 и 33 Наличие нулевого по тенциала на выходе 1 устройства указыва ет, что первому абоненту разрешается запись, а второму - чтение информации. Наличие нулевого потенциала на выходе 5 устройства сигнализирует, что первый або нент может начать чтение, а второй запись информации.

В случае одновременной подачи им пульсов, требующих приема информации от двух абонентов сразу приоритет имеет абонент, подключенный к первой шине 6 данных. Триггеры 32 и 33, указывающие направление обмена, не могут одновременно находиться в единичном состоянии, так как при установке в единичное состояние триггера 32 запрещается прохождение требований ввода по второму порту с входа 38 устройства на вход установки в единицу триггера 33 и на вход сброса триггера подается нулевой потенциал сбрасывающий триггер 33 в нулевое состояние Для предотвращения, при одновременном поступлении требовании от двух устройств, возникновения кратковременного импульса на выходе 1 он соединен с выходом триггера 33 через элемент ИЛИ 34, первый вход которого соединен с выходом триггера 32.

Регистры 15 и 21, число разрядов которых равно числу N блоков 25 хранения данных, определяют блоки 25, в которые соответственно осуществляется ввод или вывод информации Регистр 10. число разрядов которого равно числу К узлов 53 памяти в каждом блоке 25, определяет непосредственно узел 53 памяти, с которым осуществляется обмен по второму порту. Ввод информации в узел 53 памяти осуществляется при наличии единичного сигнала на входе выборки кристалла, соединенном с выходом элемента ИЛИ 51, и нулевого сигнала на входе режима узла 53, соединенном с выходом элемента 2И-ИЛИ-НЕ 52. Вывод информации из узла 53 памяти осуществляется при наличии единичных сигналов на входах выборки кристалла и режима узла 53. Выходы коммутаторов групп 54 и 55 и узлов 53 блоков 25 хранения данных имеют тристабильные выходы При наличии единичного сигнала на входе выборки кристалла коммутатора группы 55, соединенного с выходом элемента И 50 разрешается

прохождение информации через коммутатор группы 55 либо от узлоп 53 на в .оды-выходы 2 устройства, либо с шины обмена устройства на узлы 53 Направление передачи информации определяется сигналом, поступающим с входа бпока 25 хранения При единичном CHI нале на входе блока 25 хранения данных в случае наличия единичного сигнала на входе выборки кристалла

0 коммутатора группы 55 информация передается с шины 2 устройства в узлы 53, те производится ввод информации в блоки 25 по второму порту При нулевом потенциале на входе 5 блока 25 информация с входов5 выходов узлов 53 передается на шину 2 устройства, При единичном сигнале на входе 47 блока 25 хранения данных разрешается прохождение информации через коммутатор группы 54 либо от узлов 53 на входы-вы0 ходы 6 устройства, либо с шины 6 на входы-выходы узлов 53 Направление передачи информации через коммутатор группы 54 определяется сигналом, поступающим на вход 1 блока 25 При единичном

5 сигнале информация передается с шины 6 устройства на информационные входы-выходы узлов 53 памяти, т е производится ввод информации, а при нулевом потенциале на входе 1 производится вывод информа0 Ции с узлов 53 в шину 6 данных

В процессе обмена информацией по второму порту адреса ячеек памяти узлов 53 задаются счетчиком 11, а о процессе обмена по первому порту - счетчиком 17. Обмен

5 информацией по второму порту осуществ- . лятся М-разрядными словами а по первому порту Р-разрядными словами, причем Р МХК. где К - 2П, п - 0. 1. 2.. . Каждый узел 53i памяти (1 1- К) обеспечивает

Q ввод -вывод М-разрядных слов, а все узлы 53.1 -53.к памяти каждого блока 25 хранения данных - одновременный ввод-вывод Р-раз- рядных слов.

Рассмотрим процесс ввода информа5 дни в устройство по шине 2 данных и вывода по шине 6. Так как в этом режиме триггер 32 находится в нулевом состоянии и триггер 33 в единичном, то коммутаторы группы 55 всех блоков 25 памяти обеспечивают перед дачу информации с шины 2 устройства Haj вход узлов 53, а коммутаторы группы 54 всех блоков 25 памяти - с информационных входов-выходов узлов 53 на шину 6 устройства. В начальный момент на выходах элементов

с ИЛИ 24 и 39 имеют место нулевые сигналы, запрещающие вывод информации из устройства до заполнения информацией хотя бы одного блока 25 хранения данных

На выходе элемента ИЛИ 40 установлен единичный потенциал разрешающий ввод

информации в устройство с шины 2. Однако за счет единичных сигналов на первых выходах регистров 15 и 10 изменение адресов ячеек узлои 53 памяти, а также формирование выборок кристаллов осуществляется только в блоке 25 1 хранения данных.

Ввод информации в устройство по шине 2 осуществляется следующим образом. На информационных входах-выходах 2 устройства устанавливается вводимое информационное слово разрядностью М, а на входе 3 признака ввода - стробирующий положительный импульс, минимальная длительность которого равна циклу зэписм данных в узел 53. Во время действия сигнала на входе 3 на первом выходе группы 51 элементов ИЛИ блока 25 1 формируется единичный сигнал, так как единичные сигналы имеют место на первых выходах регистров 10 и 15. Поэтому запись первого слова осуществляется в узел 53.1 памяти блока 25 1 по нулевому адресу, задаваемому счетчиком 11. Задним фронтом сигнала на входе 3, стро- бирующего вводимые данные, осуществляется установка в единичное состояние второго разряда и в нулевое первого разряда регистра 10, поэтому во время ввода следующего слова данных единичный сигнал формируется на втором выходе группы 51 элементов ИЛИ и запись следующего слова осуществляется в узел 53 2 первого блока 25 1 также по нулевому адресу. После записи первых К слов данных во все узлы 53 первого блока 25 1 задним фронтом сигнала с К-го выхода кольцевого регистра 10 счетчик 11 увеличивает свое содержимое на еди- ницу, поэтому запись следующих К вводимых слов осуществляется последовательно в узлы 53 1-53 к блока 25 1 памяти по первому адресу, задаваемому счетчиком 11, и т.д.

После окончания ввода массива данных на входе 4 признака конца ввода формируется положительный импульс, который осуществляет установку в исходное состояние регистра 10 и счетчика 11, в единичное состояние второго разряда и в нулевое состояние первого разряда регистра 15. поэтому запись следующего массива данных производится в блок 25 2 в узел 53 1 по нулевому адресу. Кроме того, сигналом с входа 4 осуществляется увеличение на единицу содержимого счетчика 23, что приводит к формированию единичного сигнала на выходе элемента ИЛИ 24, а следовательно, к разрешению вывода информации из устройства, а именно с блока 25 1. Если длина вводимого массива больше емкости блока 25.1, то в момент переполнения счетчика 11 на выходе переполнения формируется единичный сигнал, который так.же. как и сигнал на входе 4 устройства, осуществляет сдвиг единичного сигнала в кольцевом реги- стре 15, увеличивает содержимое счетчика

23, и тем самым ввод массива данных продолжается в блок 25 2 в узел 53 1 памяти по нулевому адресу. Для исключения двойного срабатывания кольцевого регистра 15 и счетчика 23 при вводе массивов длиной,

0 равной емкости узла одного блока 25, введена блокировка входа 4 нулевым сигналом с выхода элемента ИЛ И 12, поступающим на второй вход элемента И 13.

Если все блоки 25 2-25 N заполнены, то

5 на выходе переполнения счетчика 23 формируется нулевой сигнал, который запрещает дальнейший ввод информации до тех пор, пока не освободится хотя бы один блок 25. . Вывод информации из устройства по

0 шине 6 возможен только после заполнения массивом данных хотя бы одного блока 25 и осуществляется Р-разрядными словами. На входе 7 устройства устанавливается единичный сигнал, стробирующий выводимые дан5 ные, с минимальной длительностью, равной циклу чтения из узла 53 памяти. Во время действия единичного сигнала на входе 7 устройства на выходе элемента И 16, а следовательно, и на первом выходе группы 22

0 элементов И формируется единичный сигнал, который приводит к формированию единичных сигналов на всех выходах группы 51 элементов ИЛИ блока 25,), на входах, выборки кристалла коммутаторов группы 54

5 блока 25 1 и входах задания режима всех узлов 53 1-53 к памяти блока 25 1, поэтому данные, выводимые из узлов 53 блока 25 i памяти по нулевому адресу, задаваемому счетчиком 17, через коммутатор группы 54

0 поступают на шину 6 устройства. Задним фронтом единичного сигнала с выхода элемента И 16 счетчик 17 адреса вывода увеличивает свое состояние на единицу, поэтому во время действия следующего единично5 го сигнала на входе 7 устройства вывод данных производится одновременно из узлов 53 1-53 к блока 25 i no следующему адресу, задаваемому счетчиком 17.

В момент окончания вывода массива

Q данных единичный сигнал формируется на входе 8 устройства, при этом в кольцевом регистре 21 происходит сдвиг информации, а счетчик 23 уменьшает свое содержимое на единицу. Аналогично режиму записи при

е выводе массивов длиной больше емкости блока 25 на выходе переполнения счетчика Сформируется единичный сигнал,функции которого аналогичны функциям сигнала на входе 8. Для исключения двойного срабатывания, как при записи, введена блокировка

входа 8 нулевым сигналом с выхода элемента ИЛИ 18,

Если после чтения массива информации отсутствуют заполненные блоки 25 (счетчик 23 установился в нулевое состояние), то дальнейший вывод информации будет приостановлен.

Переключение режима работы устройства для ввода-вывода возможно только после окончания вывода из устройства ранее записанной информации, т.е. при обнулении счетчика 23 или 35 в зависимости от направления обмена. Задним фронтом сигнала с выходов элементов ИЛИ 24 и 36 происходит установка в ноль триггеров 32 и 33 соответственно, и, таким образом, устройство для ввода-вывода находится в режиме ожидания требований обмена от абонентов, о чем сигнализирует единичными потенциалами на выходах 1 и 5 При поступлении одного из требований ввода на входы 37 и 38 устройства вновь производится настройка, аналогичная режиму настройки после начальной установки.

При вводе информации в устройство для ввода-вывода по шине 6 данных первый счетчик 23 занятости остается в нулевом состоянии, а счет занятых информацией блоков 25 осуществляется вторым счетчиком 36 занятости.

Технико-экономические преимущества предлагаемого устройства по сравнению с прототипом заключаются в расширении области его применения за счет возможности выполнения по каждому входу как ввода, так и вывода информации. Это позволяет использовать устройство в системах обработки информации, в которых необходимо осуществлять двусторонний обмен информацией.

Формула изобретения

Устройство для ввода-вывода информации, содержащее N блоков хранения данных, первая и вторая группы информационных входов-выходов которых соединены и являются первой и второй информационными шинами устройства, четыре элемента И. три кольцевых регистра, группу элементов И, пять элементов ИЛИ, первый счетчик занятости, выходы которого соединены с входами третьего элемента ИЛИ, два счетчика адреса, причем вход установки в О первого счетчика адреса соединен с входом установки в О первого кольцевого регистра, с первым входом первого элемента И и является входом признака конца обмена по второму порту устройства, выходы первого счетчика адреса соединены с адресными входами второго порта блоков хранения данных и входами первого элемента ИЛИ, выход которого соединен с вторым входом первого элемента

И, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом переполнения первого счетчика адреса, а выход - с тактовым входом второго кольцевого регистра,

0 выходы которого соединены с входами разрешения обмена по второму порту соответствующих блоков хранения данных, входы разрешения обмена по первому порту которых соединены с соответствующими выхо5 дами группы элементов И, первые входы которых соединены с соответствующими выходами третьего кольцевого регистра, а вторые выходы соединены с тактовым входом второго счетчика адреса и выходом чет0 вертого элемента И, первый вход которого является входом признака обмена по пербо- му порту устройства, вход установки в О второго счетчика адреса соединен с входом признака конца обмена по первому порту

5 устройства и вторым входом второго элемента И, первый вход которого соединен с выходом четвертого элемента ИЛИ, входы которого соединены с выходами второго счетчика адреса и входами адреса первого

0 порта блоков хранения данных, входы выборки кристаллов которых соединены с соответствующими выходами первого кольцевого регистра, выход старшего разряда которого соединен с тактовым входом

5 первого счетчика адреса, а тактовый вход - с тактовыми входами блоков хранения данных и выходом третьего элемента И, первый вход которого является входом признака обмена по второму порту устройства, выход

0 переполнения второго счетчика адреса соединен с первым входом пятого элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, а выход соединен с тактовым входом третьего кольцевого

5 регистра, отличающееся тем. что, с целью расширения области применения устройства за счет обеспечения двунаправленного обмена информацией, в него введены с пятого по восьмой элементы И, с

п шестого по одиннадцатый элементы ИЛИ, первый и второй триггеры, второй счетчик занятости, выходы которого соединены с входами восьмого элемента ИЛИ, выход которого соединен с первым входом одиннадс цатого элемента ИЛИ, тактовым входом первого триггера и третьим входом шестого элемента ИЛИ, второй вход которого соединен с входом требования ввода по первому порту устройства, а первый вход соединен с прямым выходом второго триггера, вторым

входом питого элемента И и первым входом шестого Элемента И, второй вход которого соединен с выходом пятого элемента ИЛИ и первым входом восьмого элемента И, второй вход которого соединен с первым входом девятого элемента ИЛИ, вторым входом седьмого элемента ИЛИ, вторым входом седьмого элемента И и прямым выходом первого триггера, обратный выход которого соединен с выходом подтверждения ввода по второму выводу по первому порту устройства, входом сброса второго триггера, вторым входом одиннадцатого элемента ИЛИ и вторыми управляющими входами блоков хранения данных, первые управляющие входы которых соединены с выходом подтверждения ввода по первому и вывода по второму порту устройства, вторым входом десятого элемента ИЛИ и выходом девятого элемента ИЛИ, второй вход которого соединен с обратным выходом второго триггера, вход установки которого соединен с выходом седьмого элемента ИЛИ, а тактовый вход соединен с выходом третьего элемента ИЛИ, первым входом десятого элемента

ИЛИ и первым входом седьмого элемента ИЛИ, третий вход которого является входом требования ввода по второму порту устройства, выход шестого элемента ИЛИ соединен с входом установки первого триггера, вход данных которого соединен с нулевой шиной питания устройства, выход одиннадцатого элемента ИЛИ соединен с вторым входом третьего элемента И, третий вход

которого соединен с выходом переполнения первого счетчика занятости, вход прибавления единицы которого соединен с выходом пятого элемента И, первый вход которого соединен с выходом второго элемента ИЛИ и первым входом седьмого элемента И, выход которого соединен с входом вычитания единицы второго счетчика занятости, вход прибавления единицы которого соединен с выходом восьмого элемента И, а

выход переполнения соединен с вторым входом четвертого элемента И, третий вход которого соединен с выходом десятого элемента ИЛИ, выход шестого элемента И соединен с входом вычитания единицы первого

счетчика занятости.

Фиг.I

| Устройство сопряжения | 1987 |

|

SU1425691A1 |

| Устройство для ввода-вывода информации | 1988 |

|

SU1536366A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-08-23—Публикация

1989-04-14—Подача