31508

Изобретение относится к автомати- ке и вычислительной технике и может быть использовано в цифроаналоговых и аналого- цифровых преобразователях информации.

Цель изобретения - повьшение быстродействия.

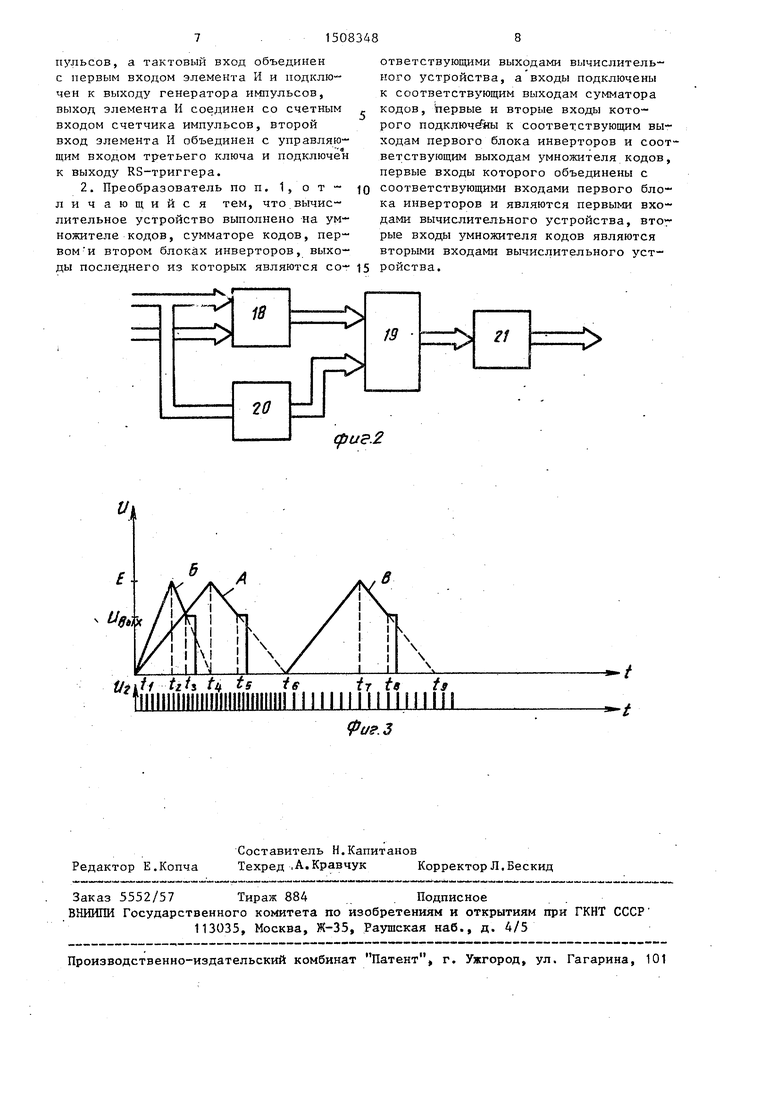

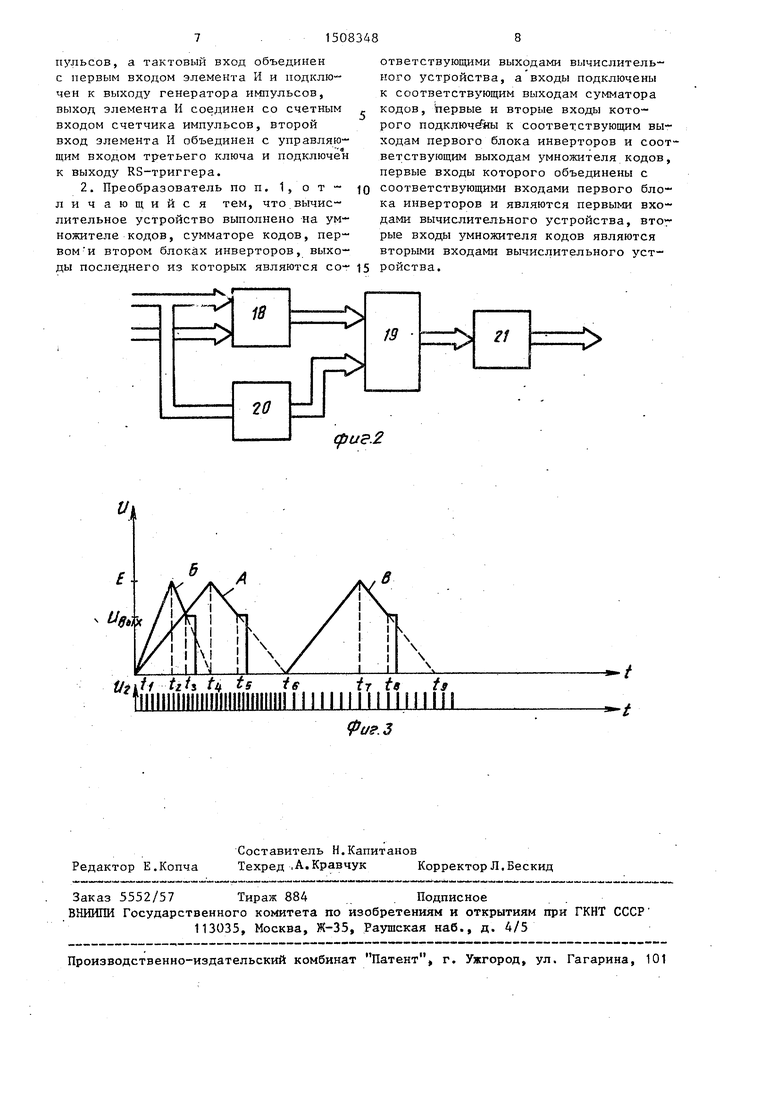

На фиг. 1 представлена функциональная схема преобразователя код - на- пряжение; на фиг. 2 - функциональная схема вычислительного устройства; на фиг. 3 - диаграмма, поясняющая принци работы преобразователя.

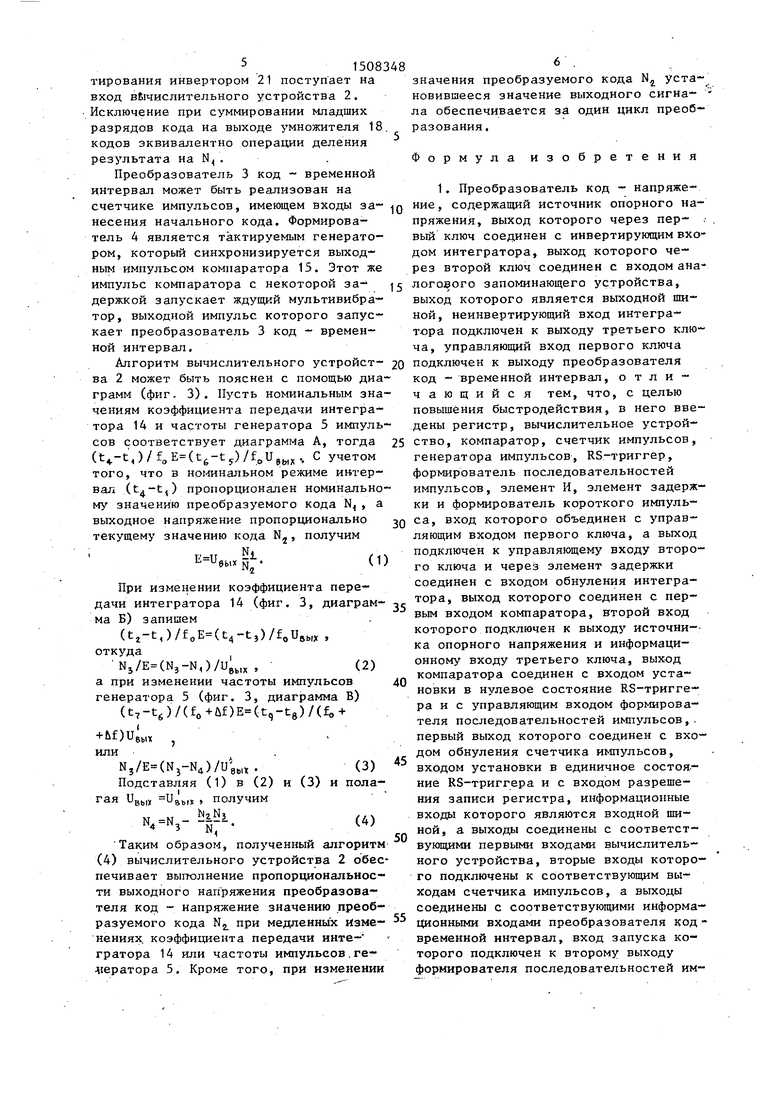

Преобразователь код - напряжение (фиг. 1) содержит регистр 1, вычисли- тельное устройство 2, преобразователь 3 код - временной интервал, формирователь 4 последовательностей импульсов, генератор 5 импульсов, RS-триг- гер 6, элемент И 7, счетчик 8 импульсов, источник 9 опорного напряжения, три ключа 10 - 12, аналоговое запоминающее устройство 13, интегратора 14, компаратор 15, формирователь 16 корот кого импульса и элемент 17 задержки. Вычислительное устройство (фиг.2) выполнено на умножителе 18 кодов, сумматоре 19 кодов и двух инверторах 20 и 21 кодов.

Преобразователь код - напряжение работает следующим образом.

В исходном состоянии интегратор 14 обнулен, преобразователь 3 код - временной интервал заблокирован, RS- триггер 6 находится в нулевом состоянии, блокируя элемент И 7.

В момент времени t, .(фиг. 3., диаграмма А) импульсом с первого выхода формирователя 4 импульсной последо- вательности преобразуемый код заносится в регистр 1, КЗ-триггер 6 устанавливается в единичное состояние, а счетчик 8 импульсов обнуляется. Сигнал с уровнем лог. 1 с выхода КЗ-триг гера открывает элемент И 7, через который импульсы генератора 5 поступают на вход синхронизации счетчика 8 и myльcoв. Сигналом с выхода RS-триг- гера 6 замыкается ключ 11, через который напряжение источника 9 опорного напряжения поступает на неинвертирующий вход интегратора 14. В результате на выходе интегратора 14 напряжение начинает возрастать. При достижении выходного напряжения интегратора 14 значение Е, равного напряжению источника 9 опорного напряжения, происходит срабатывание компаратора 15,

Q

5 0 5 0

5

О

0

5

выходным сигналом крторого RS-триг- гер 6 переводится в нулевое состояние, при этом прекращается постз пление импульсов от генератора 5 на вход счетчика 8, В момент времени Ц (момент срабатывания компаратора 15) на выходе вычислительного устройства 2 формируется код N, равный (N,-N N,/Nj) , где N, - номинальное значение преобразуемого кода; N - текущее значение преобразуемого кода; N - код на выходе счетчика 8. Момент вр емени t является концом первого такта преобразования и началом второго.

В момент времени t на втором выходе формирователя 4 формируется сигнал запуска преобразователя 3 код - временной интервал и на его выходе формируется передний фронт измерительного временного интервала, длительность которого пропорциональна значению кода N. Передним фронтом измерительного импульса замыкается ключ.10, и на инвертирующий вход интегратора 14 поступает напряжение Е с выхода источника 9 опорного напряжения. Напряжения на выходе интегратора 14 начинает убывать, вследствие чего ком- раратор 15 возвращается в исходное состояние. По окончании измерительного импульса на выходе интегратора 14 фиксируется напряжение, равное -1 kEdt . Задним фронтом измерительноi

го импульса запускается формирователь 16 короткого импульса, с помо- щью которого выходное напряжение интегратора через ключ 12 заносится в аналоговое запоминающее устройство 13. Задержанным с помощью элемента 17 задержки импульсом формирователя 16 интегратор 14 обнуляется. На этом второй такт преобразования заканчивается, на выходе преобразователя сформировано напряжение, -пропорциональное преобразуемому коду, и устройство готово к очередному циклу преобразования.

Вычислительное устройство 2 (фиг.2) предназначено для формирования кода N. Перемножение двух п разрядов кодов N и NJ осуществляется з множите- лем 18 кодов, старшие п разрядов результата перемножения суммируются с соответствующими разрядами кода Nj (инвертированного инвертором 20 кодов) с помощью сумматора 19 кодов. Результат суммирования после инвер-

15

.1508348

тирования инвертором 21 поступает на

вход вб1числительного устройства 2. Исключение при суммировании младших разрядов кода на выходе умножителя 18. кодов эквивалентно операции деления результата на N.

Преобразователь 3 код - временной интервал может быть реализован на счетчике импульсов, имеющем входы за- п несения начального кода. Формирователь 4 является тактируемым генератором, который синхронизируется выходным импульсом компаратора 15. Этот же импульс компаратора с некоторой за- держкой запускает ждущий мультивибратор , выходной импульс которого запускает преобразователь 3 код - временной интервал.

Алгоритм вычислительного устройст- 20 ва 2 может быть пояснен с помощью диаграмм (фиг. 3). Пусть номинальным значениям коэффициента передачи интегратора 14 и частоты генератора 5 импульсов соответствует диаграмма А, тогда 25 (,)/f,E(t -tp/f,U,,,,, С учетом того, что в но1-1инальном режиме интервал (,) пропорционален номинальному значению преобразуемого кода N, а выходное напряжение пропорционально о текущему значению кода Nj, получим

Ni

вых ы

(1)

При изменении коэффициента передачи интегратора 14 (фиг. 3, диаграм- ма Б) запишем

(t,-t,)/foE(t4-t,),x , откуда

Nj/E(N3-N,)/UB,,, ,(2)

а при изменении частоты импульсов генератора 5 (фиг. 3, диаграмма В)

(t7-tg)/(fo+uf)E(tq-te)/( +

+ bf)UBbu ,

или ,

Nj/E(N,-N4)/uU-(3)

Подставляя (1) в (2) и (3) и полагая UB,,), Ueb,x , получим

N,N,.(4)

Таким образом, полученный алгоритм (4) вычислительного устройства 2 обеспечивает выполнение пропорциональности выходного нагГряжения преобразователя код - напряжение значению преобразуемого кода Nj при медленньйс йзме- нениях, коэффициента передачи инте- гратора 14 или частоты импульсов.ге- lepaTopa 5. Кроме того, при изменении

15

348

.

п 2025о

45

с

40

50

значения преобразуемого кода N установившееся значение выходного сигна- ла обеспечивается за один цикл преобразования.

Формула изобретения

1. Преобразователь код - напряжение, содержащий источник опорного напряжения, выход которого через пер- вый ключ соединен с инвертирующим входом интегратора, выход которого через второй ключ соединен с входом аналогового запоминающего устройства, выход которого является выходной шиной, неинвертирующий вход интегратора подключен к выходу третьего ключа, управляющий вход первого ключа подключен к выходу преобразователя код - временной интервал, отличающийся тем, что, с целью повышения быстродействия, в него введены регистр, вычислительное устройство, компаратор, счетчик импульсов, генератора импульсов, RS-триггер, формирователь последовательностей импульсов, элемент И, элемент задержки и формирователь короткого импульса, вход которого объединен с управляющим входом первого ключа, а выход подключен к управляющему входу второго ключа и через элемент задержки соединен с входом обнуления интегратора, выход которого соединен с первым входом компаратора, второй вход которого подключен к выходу источни- ка опорного напряжения и информационному входу третьего ключа, выход компаратора соединен с входом установки в нулевое состояние RS-тригге- ра и с управляющим входом формирователя последовательностей импульсов,, первый выход которого соединен с входом обнуления счетчика импульсов, входом установки в единичное состояние RS-триггера и с входом разрешения записи регистра, информационные входы которого являются входной шиной, а выходы соединены с соответствующими первыми входами вычислительного устройства, вторые входы которого подключены к соответствующим выходам счетчика импульсов, а выходы соединены с соответствующими информационными входами преобразователя код- временной интервал, вход запуска которого подключен к второму выходу формирователя последовательностей импульсов, а тактовый вход объединен с первым входом элемента И и подключен к выходу генератора импульсов, выход элемента И соединен со счетным входом счетчика импульсов, второй вход элемента И объединен с управляющим входом третьего ключа и подключен к выходу RS-триггера.

2. Преобразователь по п. 1, о т - личающийся тем, что вычислительное устройство выполнено на умножителе кодов , сумматоре кодов, первом и втором блоках инверторов, выходы последнего из которых являются со-

ответствующими выходами вычислительного устройства, а входы подключены к соответствующим выходам сумматора кодов, Ьервые и вторые входы которого ПОДКЛЮЧЙ1Ы к соответствующим выходам первого блока инверторов и соответствующим выходам умножителя кодов, первые входы которого объединены с соответствующими входами первого блока инверторов и являются первыми входами вычислительного устройства, вто рые входы умножителя кодов являются вторыми входами вычислительного устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1986 |

|

SU1473083A1 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1984 |

|

SU1233283A1 |

| Интегрирующий аналого-цифровой преобразователь | 1982 |

|

SU1202056A1 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1988 |

|

SU1615888A1 |

| Интегрирующий аналого-цифровой преобразователь | 1986 |

|

SU1345345A1 |

| Устройство для контроля статических параметров цифроаналоговых преобразователей | 1986 |

|

SU1352647A1 |

| Преобразователь значения коэффициента модуляции амплитудно-модулированного сигнала в цифровой код | 1986 |

|

SU1370618A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1411974A1 |

| Аналого-цифровой преобразователь двухтактного интегрирования | 1988 |

|

SU1515367A2 |

| РАСХОДОМЕР ТОПЛИВА | 1990 |

|

RU2035699C1 |

Изобретение относится к автоматике и вычислительной техники и может быть использовано в цифроаналоговых и аналого-цифровых преобразователях информации. Цель изобретения - повышение быстродействия. Преобразователь код - напряжение содержит регистр 1, вычислительное устройство 2, преобразователь 3 код- временной интервал, формирователь 4 последовательностей импульсов, генератор 5 импульсов, RS-триггер 6, элемент И 7, счетчик 8 импульсов, источник 9 опорного напряжения, три ключа 10-12, аналоговое запоминающее устройство 13, интегратор 14, компаратор 15, формирователь 16 короткого импульса и элемент 17 задержки. Вычислительное устройство 2 выполнено на умножителе кодов, сумматоре кодов и двух инверторах кодов. Введение вычислительного устройства 2, счетчика 8 импульсов и других элементов с соответствующими связями позволяет повысить быстродействие преобразователя за счет сокращения времени переходного процесса установления выходного сигнала при смене входного кода до одного цикла преобразования. 1 з.п. ф-лы, 3 ил.

(риг.2

tih ti ts ieir te ff

I I I I I I I I I I I D I I t I

U .J

/

| Орнатский П.П | |||

| Автоматические приборы и измерения | |||

| Киев: Вища школа, 1986, с | |||

| Прибор для измерения угла наклона | 1921 |

|

SU253A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1989-09-15—Публикация

1988-01-18—Подача