сл

о

СО

31509922

Изобретений относится к вычислиельной технике, может быть использоано в многопроцессорных вычислительых системах

Цель изобретения - увеличение проускной способности устройства за счет совместной отработки заявок на обмен со столкновениями и без столкновений о. JO

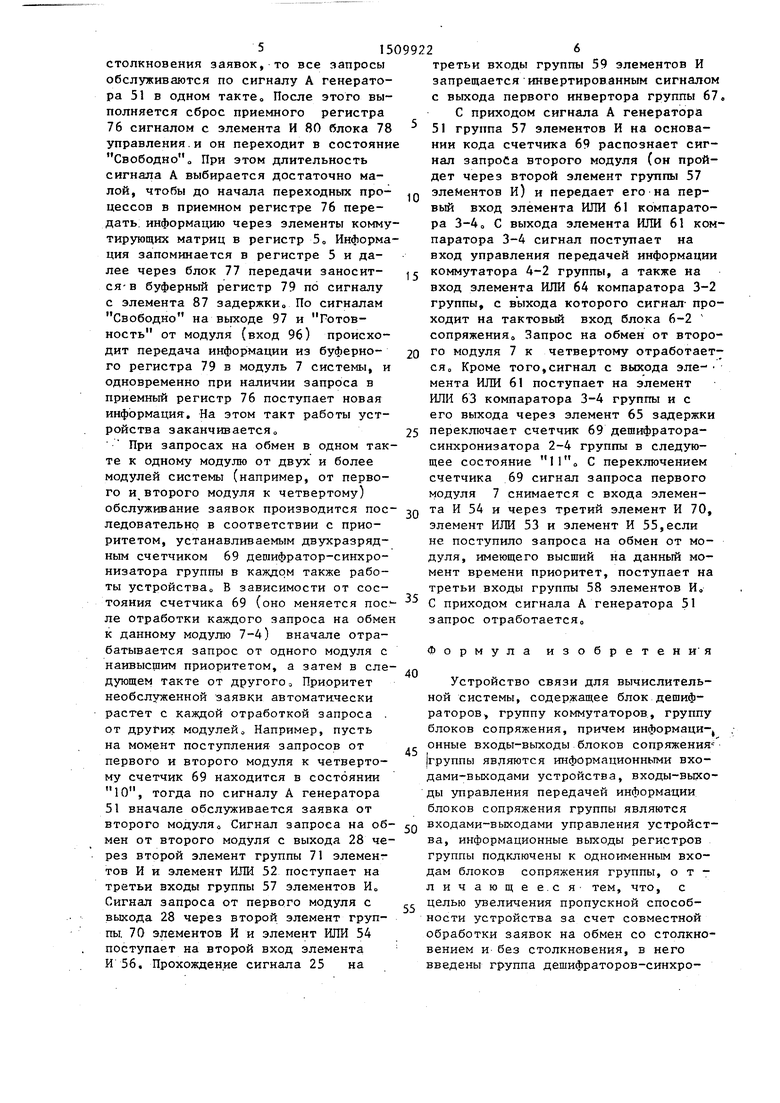

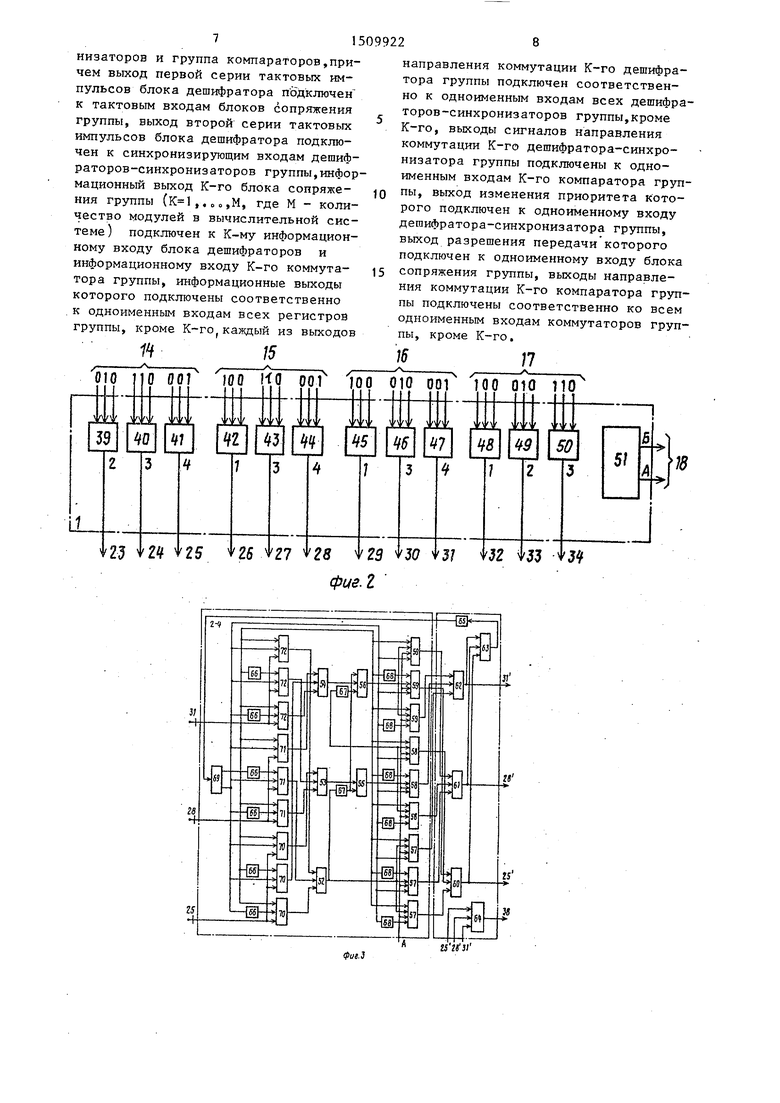

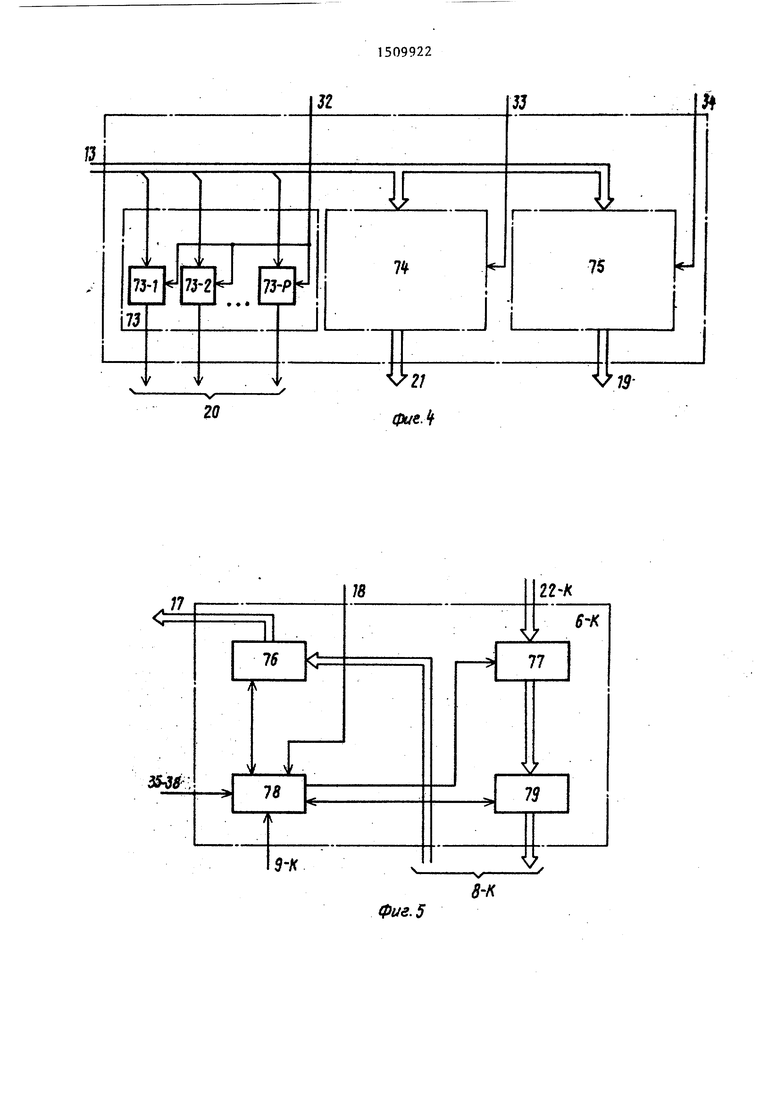

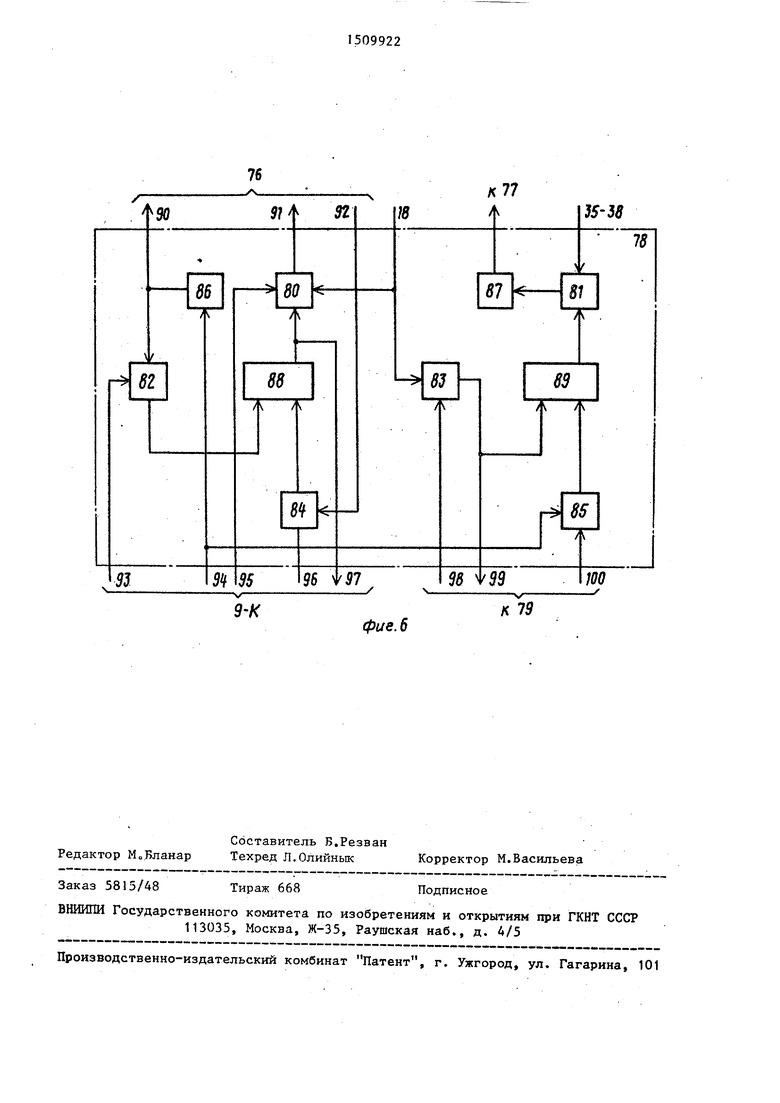

На фиго представлена функциональная схема устройства связи для вычислительной системы, состоящей из четырех модулей; на фиг. 2 - функцио-. нальная схема блока дешифратора; на is фиг о 3 - функциональная схема дешифратора-синхронизатора и компаратора; на фиг о 4 - функциональная схема коммутатора; на фиго 5 - функциональная схема блока сопряжения; на фиг 6-20 функциональная схема блока управления

Устройство (фиг„О содержит блок 1 дешифраторов, группу 2 дешифрато- ров-синхронизаторов 2- - 2-4,группу 3 компараторов 3-1 - 3-4, группу 25 4 коммутаторов 4-4 - 4-4, группу 5 регистров 5- - 5-4, гр-уппу б блоков 6г1 - 6-4 сопряжения и модули 7-1 - 7т4 вычислительной системой

Устройство.также имеет информаци- онные входы-выходы 8-1 - 8-4,управляющие входы-выходы 9-1 - 9-4, информационные входы 10-13 коммутаторов 4-1 - 4-4, информационные .входы 14-17 блока дешифраторов 1, такто- 35 вые входы 18-1 - 18-4 блоков б,1-6„4 сопряжения, информационные вьпсоды 19-21 коммутаторов, информационные входы 22-1 - 22-4 блоков сопряжения, выходы 23 - 34 направления коммута- 0 ции, выходы 23 -34 направления ком- , мутации компараторов 3-1 - 3-4,так- товые выходы 35-38 компараторав З - 3-4о

45

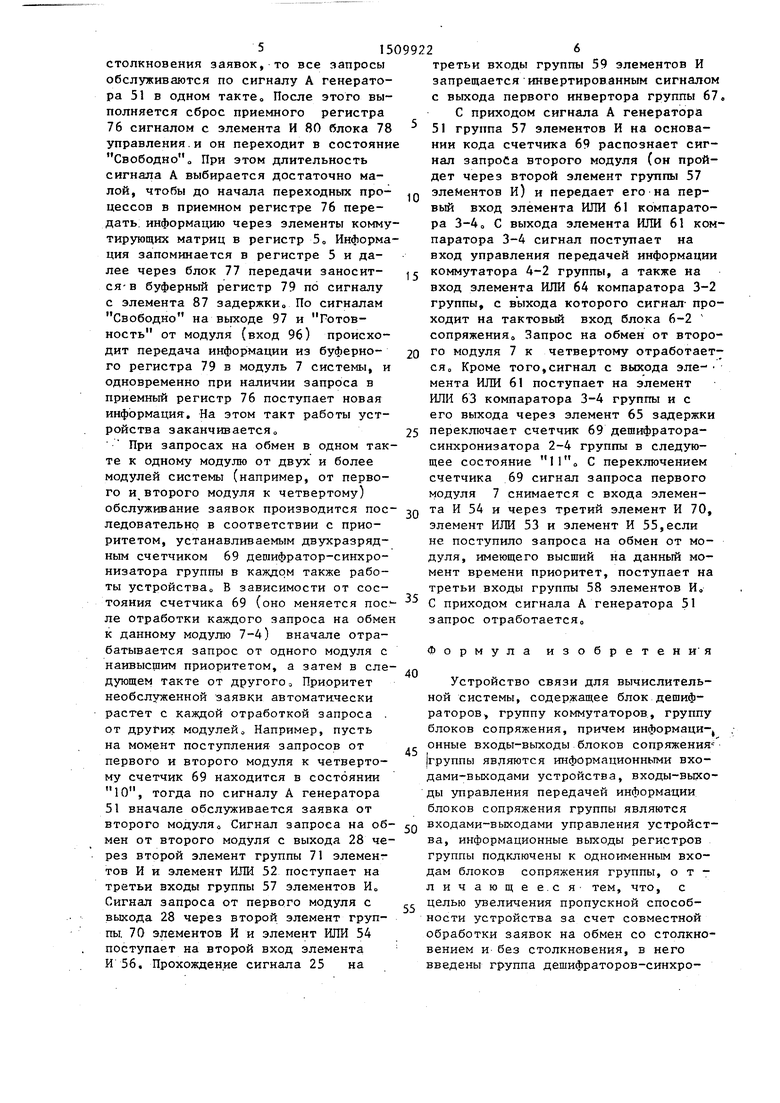

Блок 1 дешифраторов () содержит элементы И 39-50,число которых определяется выражением М(м-1), где М - количество вычислительных модулей 7, входящих в вычислительную tn систему) и генератор 51.

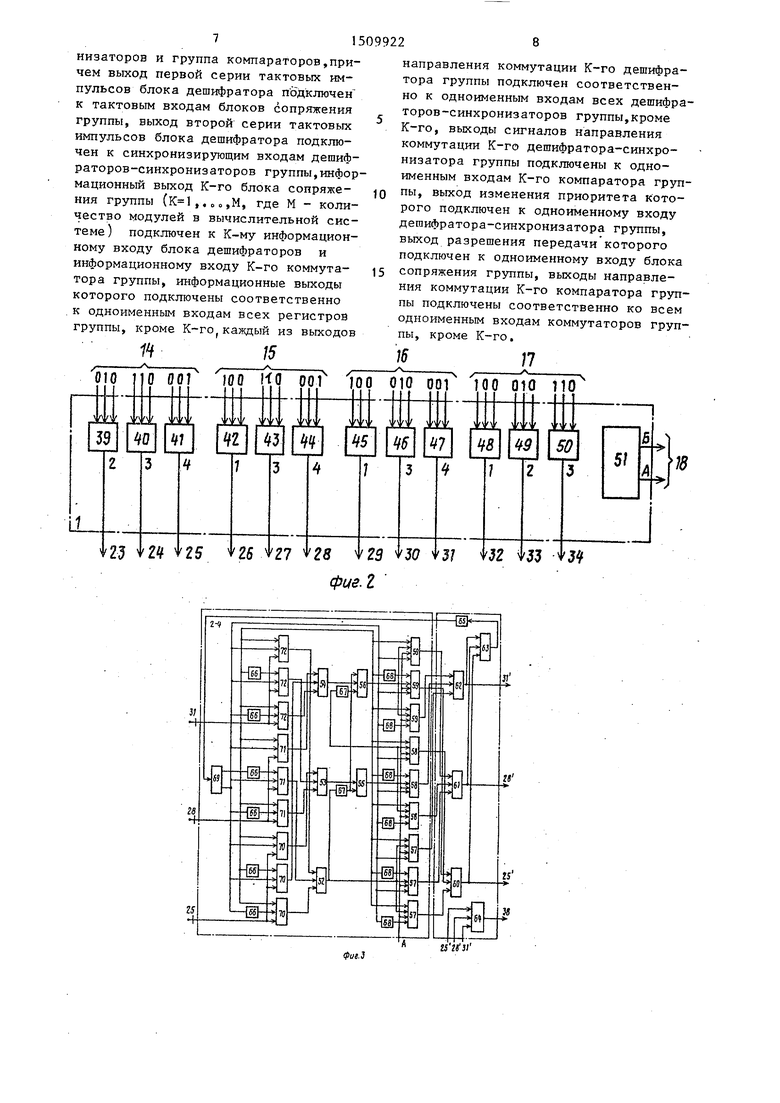

Дешифраторы-синхронизаторы 2-1 - 2-4 и компаратор 3-1 - 3-4 (фиГоЗ). содержат элементы ИЛИ 52-54,элемён- ты И 55 и 56, группы 57-59 элементов г И, элементы ИЛИ 60-64, элемент 65 задержхси, группы 66-68 инверторов, счетчик 69, группы 70-72 элемён-. тов IL

Коммутаторы 4-1 - 4-4 (фиг„4; содержат группы 73-75 из R элементов И, где R - количество информационных разрядов в приемных регистрах

Блоки 6-1 - 6-4 сопряжения (фиг,5) содержат приемный регистр 76, блок

77передачи информации, блок 78 управления и буферный регистр 79 Блок

78управления () содержит элементы И 80 - 85, элементы 86 и 87 задержки, триггеры 88 и 89. Блок 78 также имеет выход 90 занесения информации в приемный регистр 76 блока 5, выход 91 сигнала Сброс, вход 92 сигнала Свободно, вход 93 сигнала Выборка, вход 94 сигнала Обмен, вход 95 Чтение, вход 96 Готовность, выход 97 сигнала Свободно, вход 98 признака Свободно при приеме, выход 99 сигнала Сброс буферного регистра, вход 100 сигнала Запись,

В качестве модулей 7 системы могут использоваться процессоры, блоки оперативной памяти, каналы ввода-вывода и ТоПо

Устройство работает следующим образом „

В процессе, взаимодействия модули вычислительной системы, реализуя свои алгоритмы обработки данных, обмениваются информационными словами.Инфор- мационное слово может содержать как информацию, так и быть запросом на чтение информации по адресу, указанному в слове При подготовке устройства к работе все регистры, счетчики и элементы приходят в исходное состояние, блоки 6-1 - 6-4 - в состояние Свободно По пуску устройства генератор 51 в блоке 1.дешифраторов начинает вырабатывать две серии сигналов А и Б, сдвинутые относительно друг друга на величину Т, где Т - такт работы блока б-К

При поступлении запроса из модуля 7 на передачу информации устройство по состоянию блока 6-К Свободно и по сигналу Б генератора 51 производит прием информации в приемный регистр 76о При этом разряды слова, соответствующие адресу получателя, подаются непосредственно на блок. 1, который вырабатывает сигналы, устанавливающие направление передачи йнформациис

Если нет в текущем такте запросов на передачу информации от двух раз- личных модулей 7 к:одному, T.e. нет

столкновения заявок, то все запросы обслуживаются по сигналу А генератора 51 в одном такте После этого выполняется сброс приемного регистра 76 сигналом с элемента И 80 блока 78 управления.и он переходит в состояни Свободно,, При этом длительность сигнала А выбирается достаточно малой, чтобы до начала переходных про- цессов в приемном регистре 76 передать: информацию через элементы коммутирующих матриц в регистр 5о Информация запоминается в регистре 5 и далее через блок 77 передачи заносит- ся-в буферный регистр 79 по сигналу с элемента 87 задержки По сигналам Свободно на выходе 97 и Готовность от модуля (вход 96) происходит передача информации из буферно- го регистра 79 в модуль 7 системы, и одновременно при наличии запроса в приемньй регистр 76 поступает новая информация. На этом такт работы устройства заканчивается При запросах на обмен в одном такте к одному модулю от двух и более модулей системы (например, от первого и второго модуля к четвертому) обслуживание заявок производится пос ледовательно в соответствии с приоритетом, устанавливаемым двухразрядным счетчиком 69 депдифратор-синхро- низатора группы в каждом также работы устройства В зависимости от состояния счетчика 69 (оно меняется пос ле отработки каждого запроса на обме к данному модулю 7-4) вначале отрабатывается запрос от одного модуля с наивысшим приоритетом, а затем в следующем такте от другого Приоритет необслуженной заявки автоматически растет с каждой отработкой запроса . от других модулей Например, пусть на момент поступления запросов от первого и второго модуля к четвертому счетчик 69 находится в состоянии 10, тогда по сигналу А генератора 51 вначале обслуживается заявка от второго модуля Сигнал запроса на об мен от второго модуля с выхода 28 через второй элемент группы 71 элементов И и элемент ИЛИ 52 поступает на третьи входы группы 57 элементов И Сигнал запроса от первого модуля с выхода 28 через второй элемент группы. 70 элементов И и элемент ИЛИ 54 поступает на второй вход элемента И 56. Прохождение сигнала 25 на

третьи входы группы 59 элементов И запрещается инвертированным сигналом с выхода первого инвертора группы 67

С приходом сигнала А генератора 51 группа 57 элементов И на основании кода счетчика 69 распознает сигнал запроса второго модуля (он пройдет через второй элемент группы 57 элементов И) и передает его на первый вход элемента ИЛИ 61 компаратора 3-4 С выхода элемента ИЛИ 6 компаратора 3-4 сигнал поступает на вход управления передачей информации коммутатора 4-2 группы, а также на вход элемента ИЛИ 64 компаратора 3-2 группы, с выхода которого сигнал- проходит на тактовый вход блока 6-2 сопряжения Запрос на обмен от второго модуля 7 к четвертому отработается Кроме того,сигнал с выхода эле- мента ИЛИ 61 поступает на элемент ИЛИ 63 компаратора 3-4 группы и с его выхода через элемент 65 задержки переключает счетчик 69 дешифратора- синхронизатора 2-4 группы в следующее состояние 11 С переключением счетчика 69 сигнал запроса первого модуля 7 снимается с входа элемента И 54 и через третий элемент И 70, элемент ИЛИ 53 и элемент И 55,если не поступило запроса на обмен от модуля, имеющего высший на данный момент времени приоритет, поступает на третьи входы группы 58 элементов И С приходом сигнала А генератора 51 запрос отработается

Формула изобретен и я

Устройство связи для вычислительной системы, содержащее блок дешифраторов, группу коммутаторов, группу блоков сопряжения, причем информаци-, онные входы-выходы блоков сопряжения группы являются информационными входами-выходами устройства, входы-выходы управления передачей информации блоков сопряжения группы являются входами-выходами управления устройства, информационные выходы регистров группы подключены к одноименным входам блоков сопряжения группы, о т - личающее.ся тем, что, с целью увеличения пропускной способности устройства за счет совместной обработки заявок на обмен со столкновением и без столкновения, в него введены группа дешифраторов-синхро-

низаторов и группа компараторов,причем выход первой серии тактовых импульсов блока дешифратора п оДключен к тактовым входам блоков сопряжения группы, выход второй серии тактовых импульсов блока дешифратора подключен к синхронизирующим входам дешифраторов-синхронизаторов группы,информационный выход К-го блока сопряжения группы (,,оо,М, где М - количество модулей в вычислительной системе ) подключен к К-му информационному входу блока дешифраторов и информационному входу К-го коммутатора группы, информационные выходы которого подключены соответственно , к одноименным входам всех регистров группы, кроме K-rOjкаждый из выходов

5

направления коммутации К-го дешифратора группы подключен соответственно к одноименным входам всех дешифраторов-синхронизаторов группы,кроме К-го, выходы сигналов направления коммутации К-го дешифратора-синхронизатора группы подключены к одноименным входам К-го компаратора группы, выход изменения приоритета которого подключен к одноименному входу дешифратора-синхронизатора группы, выход разрешения передачи которого подключен к одноименному входу блока сопряжения группы, выходы направления коммутации К-го компаратора группы подключены соответственно ко всем одноименным входам коммутаторов группы, кроме К-го.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство связи для вычислительной системы | 1986 |

|

SU1315990A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ОПЕРАТИВНОЙ ПАМЯТЬЮ | 1992 |

|

RU2060538C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство для сопряжения двух ЭВМ | 1990 |

|

SU1798793A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных вычислительных системах. Цель изобретения - увеличение пропускной способности устройства за счет совместной обработки заявок на обмен со столкновением и без столкновения. В устройство, содержащее блок 1 дешифраторов, группу коммутаторов 4-1...4-4, группу регистров 5-1...5-4, группу блоков 6-1...6-4 сопряжения, модули 7-1...7-4 вычислительной системы, введены группа дешифраторов-синхронизаторов 2-1...2-4 и группа компараторов 3-1...3-4. Это позволяет в соответствии с "плавающим" приоритетом последовательно отрабатывать заявки на обмен со столкновениями к данному вычислительному модулю одновременно с отработкой заявок на обмен как со столкновениями, так и без них к другим вычислительным модулям. 6 ил.

Iff

15

фие.г

16

Л

фиг.З

a tf ji

20

фиеЛ

фиг. 5

9-Н

Составитель Б.Резван Редактор М„Бланар Техред Л.Олийнык Корректор М.Васильева

Заказ 5815/48

Тираж 668

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

фие.6

к 79

Подписное

| Вычислительная система последовательного действия | 1976 |

|

SU602950A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-09-23—Публикация

1988-01-11—Подача