1)3

Изобретение относится к вычислительной технике и может применяться при создании многопроцессорных вы- . числительных систем.

Цель изобретения - повышение быстродействия вычислительной системы.

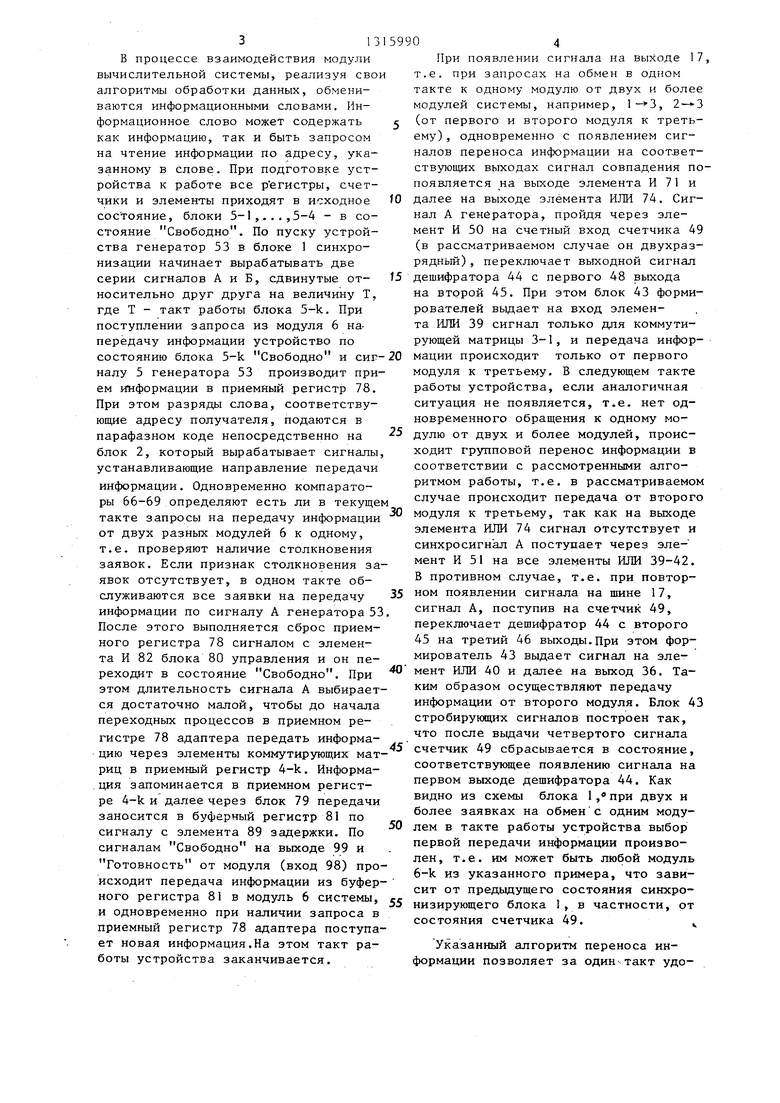

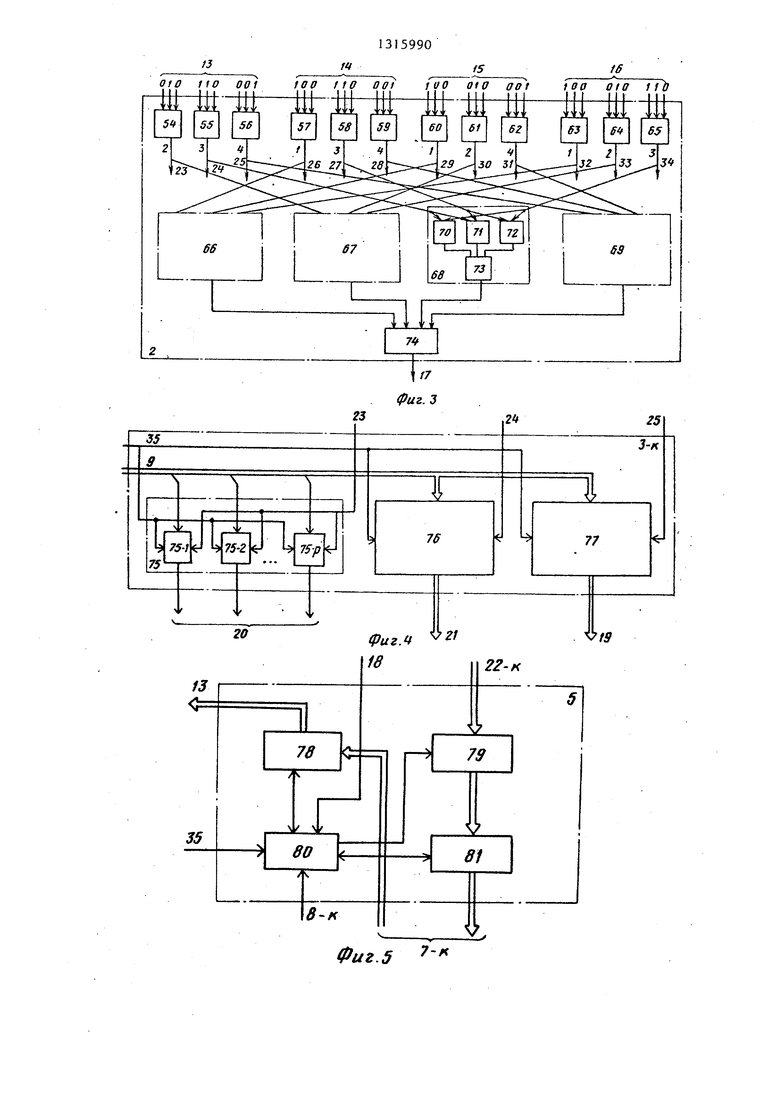

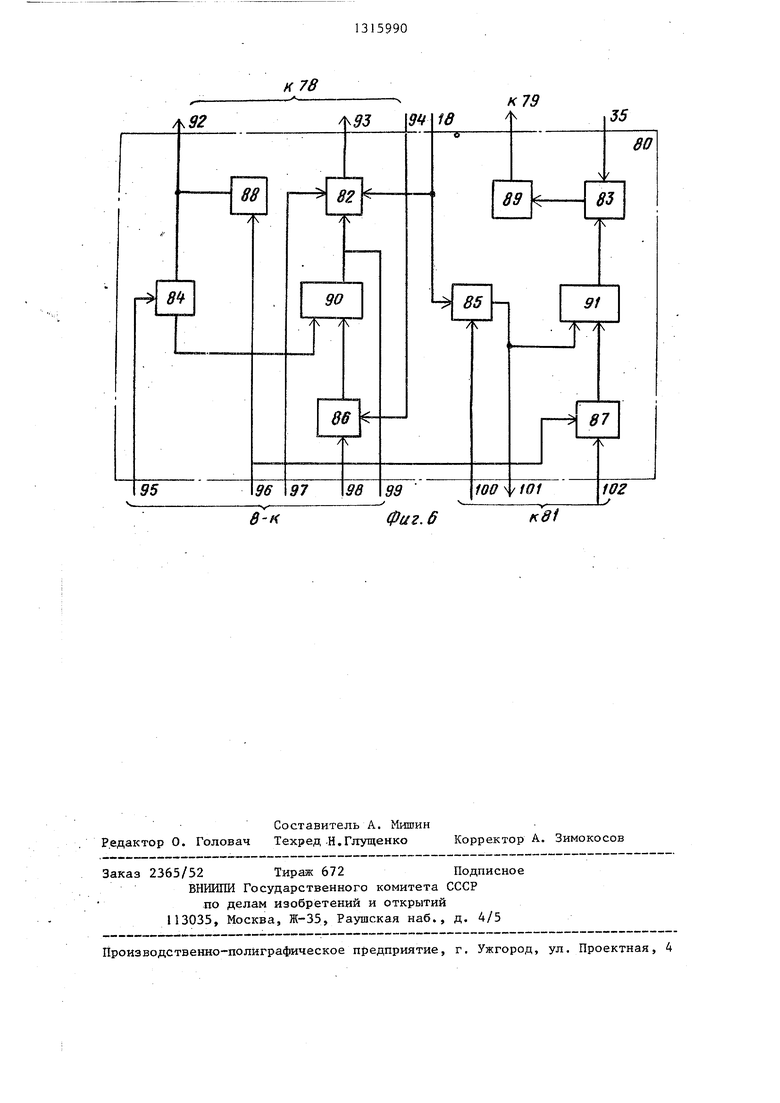

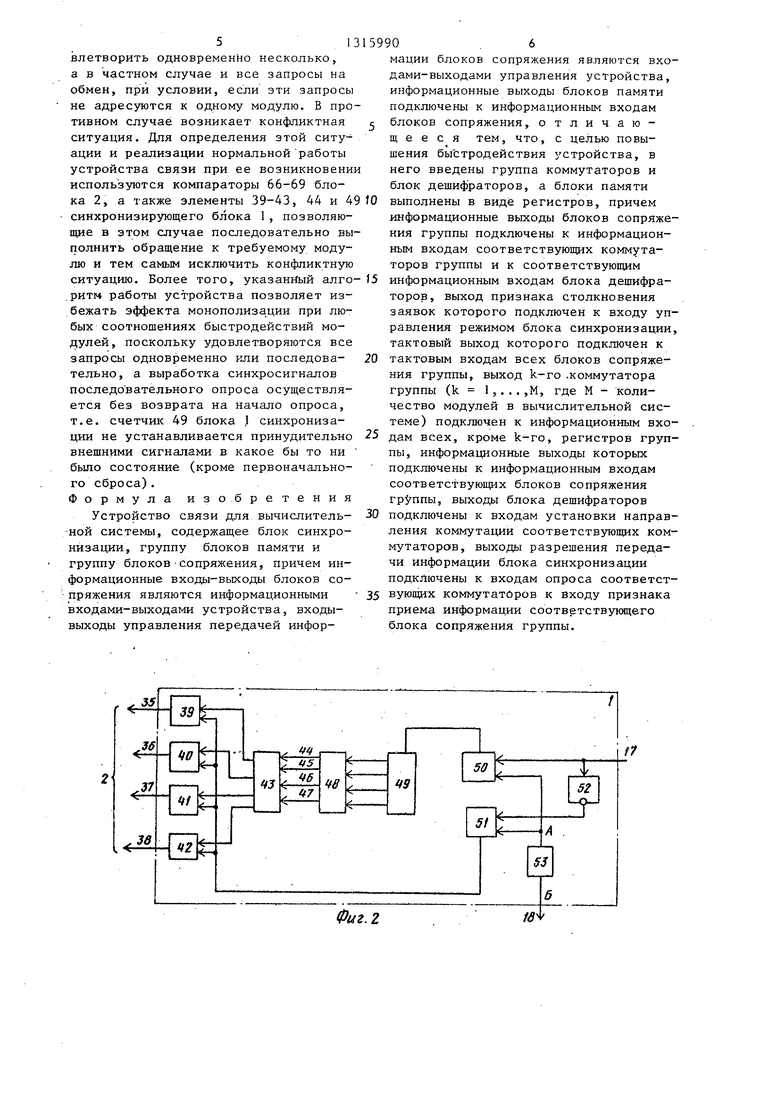

На фиг. 1 представлен пример функциональной схемы устройства связи для вычислительной системы из четырех модулей; на фиг. 2 - функциональная схема блока синхронизации; на фиг. 3 - функциональная схема блока дешифраторов; на фиг. 4 - функциональная схема коммутатора; на фиг.5 - функциональная схема блока сопряжения; на фиг. 6 - функциональная схема

блока управления блока сопряжения.

I

Устройство связи для вычислительной системы (фиг. 1) содержит блок 1 синхронизации, блок 2 дешифраторов, группу 3 коммутаторов 3-1,...,3-4, группу 4 регистров 4-1,...,4-4, группу 5 блоков 5-1,...,5-4 сопряжения и модули 6-1,...,6-4 вычислительной системы, причем информационные входы- выходы блоков 5-1,...,5-4 сопряжения являЕотся информационными входами (выходами) 7-1,...,7-4 устройства, входы-выходы управленияпередачей информации блоков 5-1,...,5-4 сопряжения являются входами (выходами) 8-1,..., 8-4 управления устройства, информационные выходы блоков 5-1,...,5-4 со.пряжения группы подключены к информационным входам 9-12 соответствующих коммутаторов 3-1,...,3-4 группы и к соответствующим информационным входам 13-16 блока 2 дешифраторов, выход 17 признака столкновения заявок

которого подключен к тактовым входам 18 всех блоков 5-1,,..,5-4 сопряжения группы, выход k-ro коммутатора группы (k 1,.,.,k-4) ПОДКЛЮ-. чен к информационным входам 19-21 всех, кроме k-го, регистров 4-1,..,, 4-4 группы, информационные выходы 22-1,. .., 22-4 которых подключены к информационным входам соответствующих блоков 5-1,...,5-4 сопряжения группы, выходы 23-25, 26-28, 29-31 и 32-34 блока 2 дешифраторов подключены к входам установки направления коммутации соответствующих коммутаторов-3-1,..., 3-4 группы. Выходы 35-38 разрешения передачи информации блока 1 синхронизации подключены к входам опроса соот ветствующих коммутаторов 3-1,...,3-4 и входу признака приема информации с

5990 . 2

соответствующего блока 5-1,...,5-4 со- сопряжения группы.

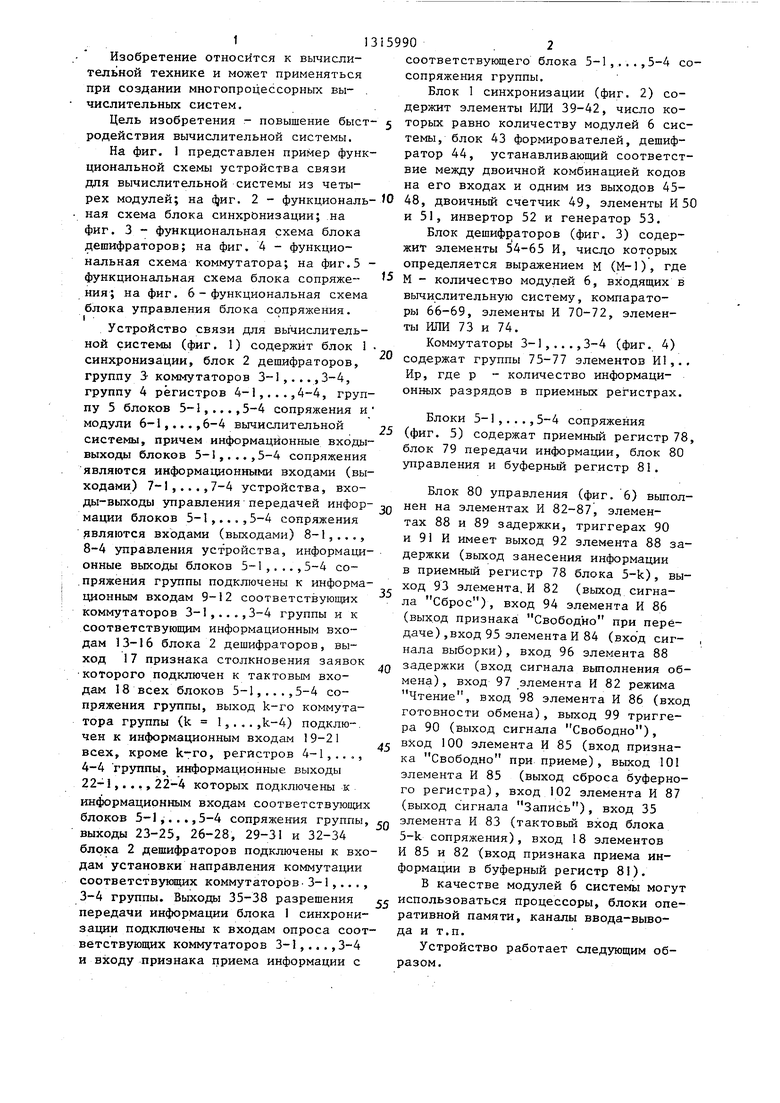

Блок 1 синхронизации (фиг. 2) содержит элементы ИЛИ 39-42, число ко5 торых равно количеству модулей 6 системы, блок 43 формирователей, дешифратор 44, устанавливаюшлй соответствие между двоичной комбинацией кодов на его входах и одним из выходов 450 48, двоичный счетчик 49, элементы И 50 и 51, инвертор 52 и генератор 53.

Блок дешифраторов (фиг. 3) содержит элементы 54-65 И, число которых определяется выражением м (М-1), где

5м- количество модулей 6, входящих в вычислительную систему, компараторы 66-69, элементы И 70-72, элемен- ИЛИ 73 и 74.

Коммутаторы 3-1,...,3-4 (фиг. 4)

20 содержат группы 75-77 элементов И1,.. И.р, где р - количество информационных разрядов в приемных регистрах.

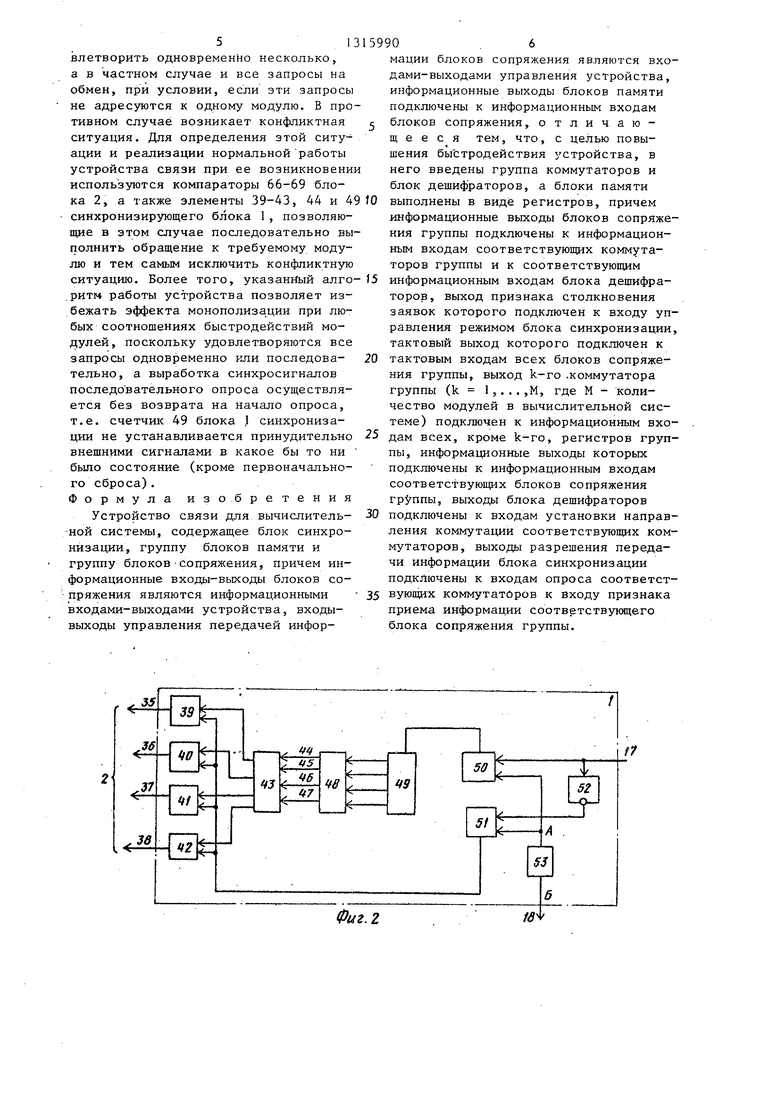

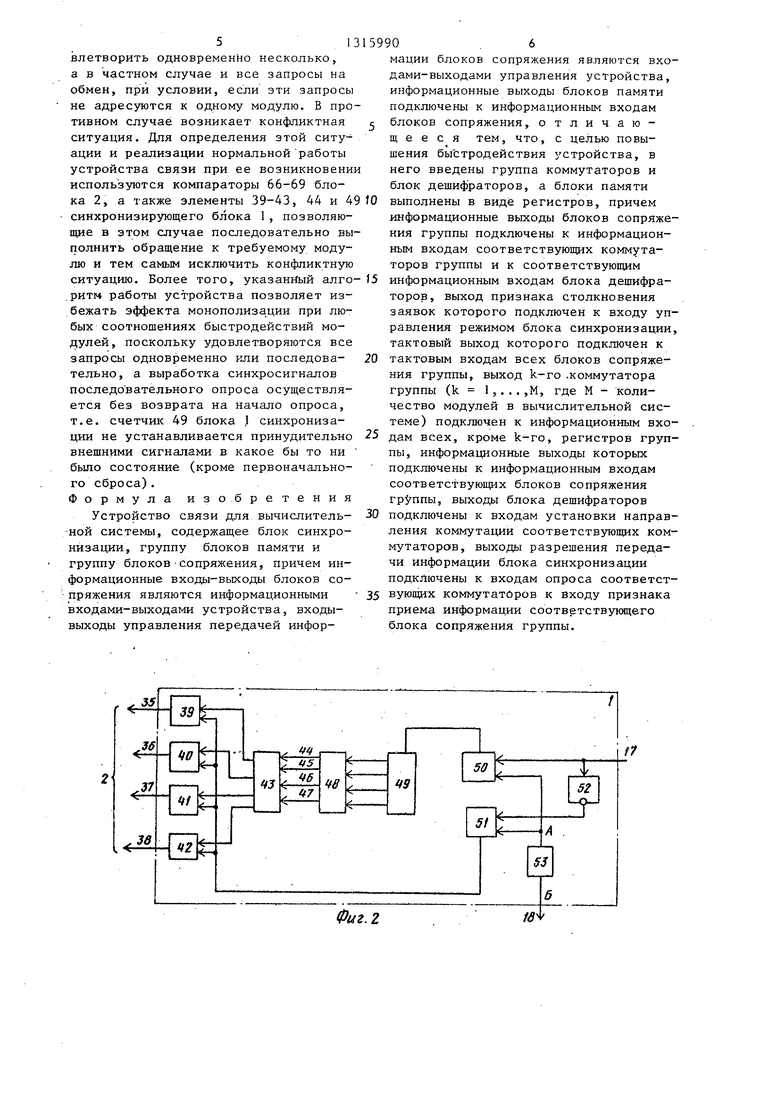

Блоки 5-1,...,5-4 сопряжения 25 (фиг. 5) содержат приемный регистр 78, блок 79 передачи информации, блок 80 управления и буферный регистр 81.

Блок 80 управления (фиг. 6) вьшол30 нен на элементах И 82-87, элементах 88 и 89 задержки, триггерах 90 и 91 И имеет выход 92 элемента 88 задержки (выход занесения информации в приемный регистр 78 блока 5-k), выход 93 элемента. И 82 (выход сигнала Сброс), вход 94 элемента И 86 (выход признака Свободно при передаче) , вход 95 элемента И 84 (вход сиг- , нала выборки), вход 96 элемента 88

Q задержки (вход сигнала выполнения обмена) , вход 97 элемента И 82 режима Чтение, вход 98 элемента И 86 (вход готовности обмена), выход 99 триггера 90 (выход сигнала Свободно),

4 вход 100 элемента И 85 (вход признака Свободно при приеме), выход 101 элемента И 85 (выход сброса буферного регистра), вход 102 элемента И 87 (выход сигнала Запись), вход 35

Q элемента И 83 (тактовый вход блока 5-k сопряжения), вход 18 элементов И 85 и 82 (вход признака приема информации в буферный регистр 81).

В качестве модулей 6 системы могут

2 использоваться процессоры, блоки оперативной памяти, каналы ввода-выво- да и т.п.

Устройство работает следующим образом.

35

313

В процессе взаимодействия модули вычислительной системы, реализуя свои алгоритмы обработки данных, обмениваются информационными словами. Информационное слово может содержать как информацию, так и быть запросом на чтение информации по адресу, указанному в слове. При подготовке устройства к работе все р егистры, счетчики и элементы приходят в исходное сос тояние, блоки 5-1,...,5-4 - в состояние Свободно. По пуску устройства генератор 53 в блоке 1 синхронизации начинает вырабатывать две серии сигналов А и Б, сдвинутые от- носительно друг друга на величину Т, где Т - такт работы блока 5-k. При поступлении запроса из модуля 6 на- передачу информации устройство по состоянию блока 5-k Свободно и сигналу 5 генератора 53 производит прием информации в приемный регистр 78. При этом разряды слова, соответствующие адресу получателя, подаются в парафазном коде непосредственно на блок 2, который вырабатывает сигналы, устанавливающие направление передачи информации. Одновременно компараторы 66-69 определяют есть ли в текущем такте запросы на передачу информации от двух разных модулей 6 к одному, т.е. проверяют наличие столкновения заявок. Если признак столкновения заявок отсутствует, в одном такте обслуживаются все заявки на передачу информации по сигналу А генератора 53 После этого выполняется сброс приемного регистра 78 сигналом с элемента И 82 блока 80 управления и он переходит в состояние Свободно. При этом длительность сигнала А выбирается достаточно малой, чтобы до начала переходных процессов в приемном регистре 78 адаптера передать информацию через элементы коммутирующих матриц в приемный регистр 4-k. Информация запоминается в приемном регистре 4-k и далее через блок 79 передачи заносится в буферный регистр 81 по сигналу с элемента 89 задержки. По сигналам Свободно на выходе 99 и Готовность от модуля (вход 98) происходит передача информации из буфер- ного регистра 81 в модуль 6 системы, и одновременно при наличии запроса в приемный регистр 78 адаптера поступает новая информация.На этом такт работы устройства заканчивается.

O 5 0 5 е

0

5

0

О4

При появлении сигнала на выходе 17, т.е. при запросах на обмен в одном такте к одному модулю от двух и более модулей системы, например, , (от первого и второго модуля к третьему) , одновременно с появлением сигналов переноса информации на соот.вет- ствующих выходах сигнал совпадения по- появляется на выходе элемента И 71 и далее на выходе элемента ИЛИ 74. Сигнал А генератора, пройдя через элемент И 50 на счетный вход счетчика 49 (в рассматриваемом случае он двухразрядный) , переключает выходной сигнал дешифратора 44 с первого 48 выхода на второй 45. При этом блок 43 формирователей вьщает на вход элемента ИЛИ 39 сигнал только для коммутирующей матрицы 3-1, и передача информации происходит только от первого модуля к третьему. В следующем такте работы устройства, если аналогичная ситуация не появляется, т.е. нет одновременного обращения к одному модулю от двух и более модулей, происходит групповой перенос информации в соответствии с рассмотренными алгоритмом работы, т.е. в рассматриваемом случае происходит передача от второго модуля к третьему, так как на выходе элемента ИЛИ 74 сигнал отсутствует и синхросигнал А поступает через эле- мент И 51 на все элементы ИЛИ 39-42. В противном случае, т.е. при повторном появлении сигнала на шине 17, сигнал А, поступив на счетчик 49, переключает дешифратор 44 с второго 45 на третий 46 выходы.При этом формирователь 43 вьщает сигнал на элемент ИЛИ 40 и далее на выход 36. Таким образом осуществляют передачу информации от второго модуля. Блок 43 стробирующих сигналов построен так, что после выдачи четвертого сигнала счетчик 49 сбрасывается в состояние, соответствукнцее появлению сигнала на первом выходе дешифратора 44. Как видно из схемы блока 1,при двух и более заявках на обмен с одним модулем в такте работы устройства выбор первой передачи информации произволен, т.е. им может быть любой модуль 6-k из указанного примера, что зависит от предыдущего состояния синхронизирующего блока I, в частности, от состояния счетчика 49.

Указанный алгоритм переноса информации позволяет за удо513

влетворить одновременно несколько, а в частном случае и все запросы на обмен, при условии, если эти запросы не адресуются к одному модулю. В противном случае возникает конфликтная ситуация. Для определения этой ситуации и реализации нормальной работы устройства связи при ее возникновении исполь:зуются компараторы 66-69 блока 2, а также элементы 39-43, 44 и 49 синхронизирующего блока 1, позволяющие в этом случае последовательно выполнить обращение к требуемому модулю и тем самым исключить конфликтную ситуацию. Более того, указанный алгоритм работы устройства позволяет избежать эффекта монополизации при любых соотношениях быстродействий модулей, поскольку удовлетворяются все запросы одновременно или последовательно, а выработка синхросигналов последовательного опроса осуществляется без возврата на начало опроса, т.е. счетчик 49 блока ) синхронизации не устанавливается принудительно внешними сигналами в какое бы то ни было состояние (кроме первоначального сброса).

Формула изобретения Устройство связи для вычислитель- ной системы, содержащее блок синхронизации, группу блоков памяти и группу блоков-сопряжения, причем информационные входь1-выходы блоков со- пряжения являются информационными входами-выходами устройства, входы- выходы управления передачей инфор0 . 6

нации блоков сопряжения являются входами-выходами управления устройства, информационные выходы блоков памяти подключены к информационным входам

блоков сопряжения, отличающееся тем, что, с цедзью повышения быстродействия устройства, в него введены группа коммутаторов и блок дешифраторов, а блоки памяти

выполнены в виде регистров, причем информационные выходы блоков сопряжения группы подключены к информационным входам соответствующих коммутаторов группы и к соответствующим

информационным входам блока дешифраторов, выход признака столкновения заявок которого подключен к входу управления режимом блока синхронизации, тактовый выход которого подключен к

тактовым входам всех блоков сопряжения группы, выход k-ro .коммутатора группы (k 15...,М, где М - количество модулей в вычислительной системе) подключен к информационным входам всех, кроме k-ro, регистров группы, информационные выходы которых подключены к информационным входам соответствующих блоков сопряжения группы, выходы блока дешифраторов

подключены к входам установки направления коммутации соответствующих коммутаторов, выходы разрешения передачи информации блока синхронизации подключены к входам опроса соответствующих коммутаторов к входу признака приема информации соответствующего блока сопряжения группы.

/J

W

01O no 001 too 11 ff oat too oio aot too ate Г77

/5

t6

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство связи для вычислительной системы | 1988 |

|

SU1509922A1 |

| Устройство связи для вычислительной системы | 1981 |

|

SU1275453A1 |

| Устройство связи для вычислительной системы | 1984 |

|

SU1164722A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство связи для вычислительной системы | 1981 |

|

SU962907A1 |

| Устройство связи для вычислительнойСиСТЕМы | 1979 |

|

SU802957A1 |

| Устройство для сопряжения модулейВычиСлиТЕльНОй СиСТЕМы C KOHTPO-лЕМ | 1978 |

|

SU807258A1 |

| Устройство связи для вычислительной системы | 1981 |

|

SU983699A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для сопряжения двух ЭВМ | 1990 |

|

SU1798793A1 |

Изобретение относится к вычислительной технике, может быть использовано в многопроцессорных вычислительных системах и позволяет повысить быстродействие вычислительной системы. В состав устройства входят блок 1 синхронизации, блок 2 дешифраторов, группа коммутаторов 3-1,..., 3-М, где М - количество модулей в вычислительной системе, группа регистров 4-1,...,4-м и группа блоков 5-1,..., 5-м сопряжения. К блокам 5-1 5-м сопряжения группы подключены модули 6-1,...,6-м вычислительной системы. На фиг. 1 приведен пример вы- числи- ельной системы, состоящей из четырех модулей (М 4). В процессе работы при помощи коммутаторов 3-1 ,. .., 3-4 группы модули 6-1,...,6-4 вычислительной системы обмениваются информационными словами, причем все заявки на обмен удовлетворяются параллельно за один такт работы устройства при условии, что они не адресуются к одному модулю. При возникновении конфликтной ситуации блок 2 дешифраторов формирует признак столкновения заявок, по которому блок 1 синхронизации организует последовательное обслуживание модулей вычислительной системы. 6 ил. S (Л САЭ СП СО

Фиг.5

фиг.Ч

7-л

96 97 98 99 100 101

f

Фиг. 6

к8

к81

| Устройство связи для вычислительной системы | 1980 |

|

SU898413A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство связи для вычислительной системы | 1977 |

|

SU734654A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-06-07—Публикация

1986-02-18—Подача