1

(21)4320709/24-21

(22)26.10.87

(46) 30.09.89. Бюл. № 36

(72) А.Б.Королев и С,А.Новожилов

(53)621.374(088.8)

(56)Авторское свидетельство СССР № 1188869, кл. Н 03 К 5/19, 1984.

Авторское свидетельство СССР № 531091, кл. G 01 R 23/00, 1975.

(54)УСТРОЙСТВО ДЛЯ ДОПУСКОВОГО КОНТРОЛЯ ЧАСТОТЫ

(57)Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и связи. Цель изобретения - повышение быстродействия при сохранении точности контроля. Для достижения цели в устройство, содержащее блок 4 синхронизации, элемент И 6, счетчик 7 импульсов, триггер 8, введены триггер 9 и преобразователь 5, который фор- . мирует разностную частоту эталонного и контролируемого сигналов. По импульсу запуска на шине 3 блок 4 устанавливает в исходное состояние счетчик 7 и триггеры 8, 9. Затем счетчик 7 подсчитывает количество импульсов эталонной частоты за период разностной частоты, определяя тем самым не выходит ли разность эталонной и контролируемой частот за пределы установленного с помощью кода на шине 12 допуска. Триггеры В и 9 фиксируют результат сравнения. 2 3.п. ф-лы, 5 ил.

i (О

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля резервированного генератора | 1987 |

|

SU1457147A1 |

| Устройство для допускового контроля частоты следования импульсов | 1982 |

|

SU1034165A1 |

| Ультразвуковой измеритель перемещений | 1989 |

|

SU1619027A1 |

| Преобразователь кода во временной интервал | 1988 |

|

SU1672567A1 |

| Устройство для контроля микросхем | 1985 |

|

SU1322289A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Устройство для локализации неисправностей | 1988 |

|

SU1674128A1 |

| Устройство измерения времени ограничения тока транзисторными коммутаторами систем зажигания | 1989 |

|

SU1758279A1 |

| Устройство для допускового контроля частоты | 1980 |

|

SU883771A1 |

| Ультразвуковой измеритель линейных перемещений | 1989 |

|

SU1645812A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и связи. Цель изобретения - повышение быстродействия при сохранении точности контроля. Для достижения цели в устройство, содержащее блок 4 синхронизации, элемент И 6, счетчик 7 импульсов, триггер 8, введены триггер 9 и преобразователь 5, который формирует разностную частоту эталонного и контролируемого сигналов. По импульсу запуска на шине 3 блок 4 устанавливает в исходное состояние счетчик 7 и триггеры 8, 9. Затем счетчик 7 подсчитывает количество импульсов эталонной частоты за период разностной частоты, определяя тем самым не выходит ли разность эталонной и контролируемой частот за пределы установленного с помощью кода на шине 12 допуска. Триггеры 8 и 9 фиксируют результат сравнения. 2 з.п. ф-лы, 5 ил.

00

сд

4

фиг.1

3-15

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и связи.

Цель изобретения - повышение быстродействия при сохранении точности контроля.

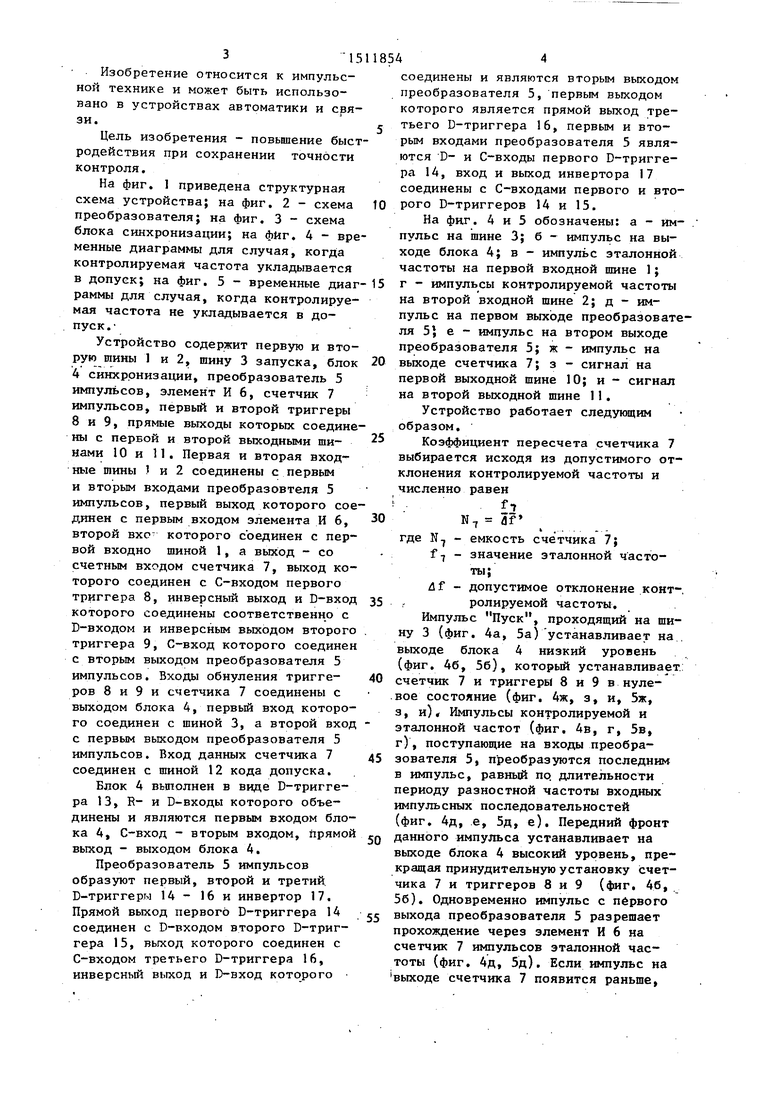

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - схема преобразователя; на фиг. 3 - схема блока синхронизации; на фиг. 4 - временные диаграммы для случая, когда контролируемая частота укладывается в допуск; на фиг. 5 - временные диаграммы для случая, когда контролируемая частота не укладывается в допуск.Устройство содержит первую и вторую шины 1 и 2, шину 3 запуска, блок 4 синхронизации, преобразователь 5 импульсов, элемент И 6, счетчик 7 импульсов, первый и второй триггеры 8 и 9, прямые выходы которьпс соединены с первой и второй выходными шинами 10 и 11. Первая и вторая входные шины и 2 соединены с первым и вторым входами преобразовтеля 5 импульсов, первый выход которого соединен с первым входом элемента И 6, второй вхс- которого соединен с первой входно шиной 1, а выход - со счетным входом счетчика 7, выход которого соединен с С-входом первого триггера 8, инверсный выход и D-вход которого соединены соответственно с D-входом и инверсным выходом второго тригг-ера 9, С-вход которого соединен с вторым выходом преобразователя 5 импульсов. Входы обнуления триггеров 8 и 9 и счетчика 7 соединены с выходом блока 4, первьш вход которого соединен с шиной 3, а второй вход с первым выходом преобразователя 5 импульсов. Вход данных счетчика 7 соединен с шиной 12 кода допуска.

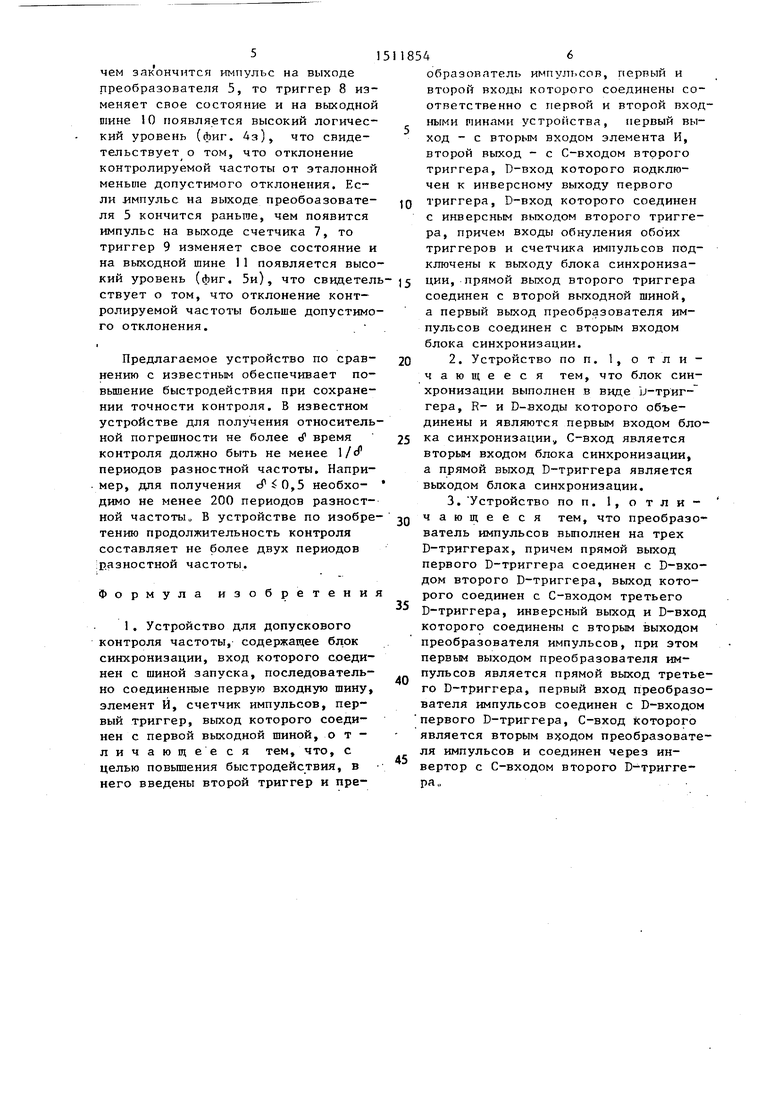

Блок 4 выполнен в виде D-тригге- ра 13, R- и D-входы которого объединены и являются первым входом блока 4, С-вход - вторым входом, прямой выход - выходом блока 4.

Преобразователь 5 импульсов образуют первый, второй и третий. D-триггеры 14 - 16 и инвертор 17. Прямой выход первого D-триггера 14 соединен с D-входом второго D-триггера 15, выход которого соединен с С-входом третьего D-триггера 16, инверсный выход и D-вход которого

4

соединены и являются вторым выходом преобразователя 5, первым выходом которого является прямой выход третьего D-триггера 16, первым и вторым входами преобразователя 5 являются D- и С-входы первого D-триггера 14, вход и выход инвертора 17 соединены с С-входами первого и второго D-триггеров 14 и 15.

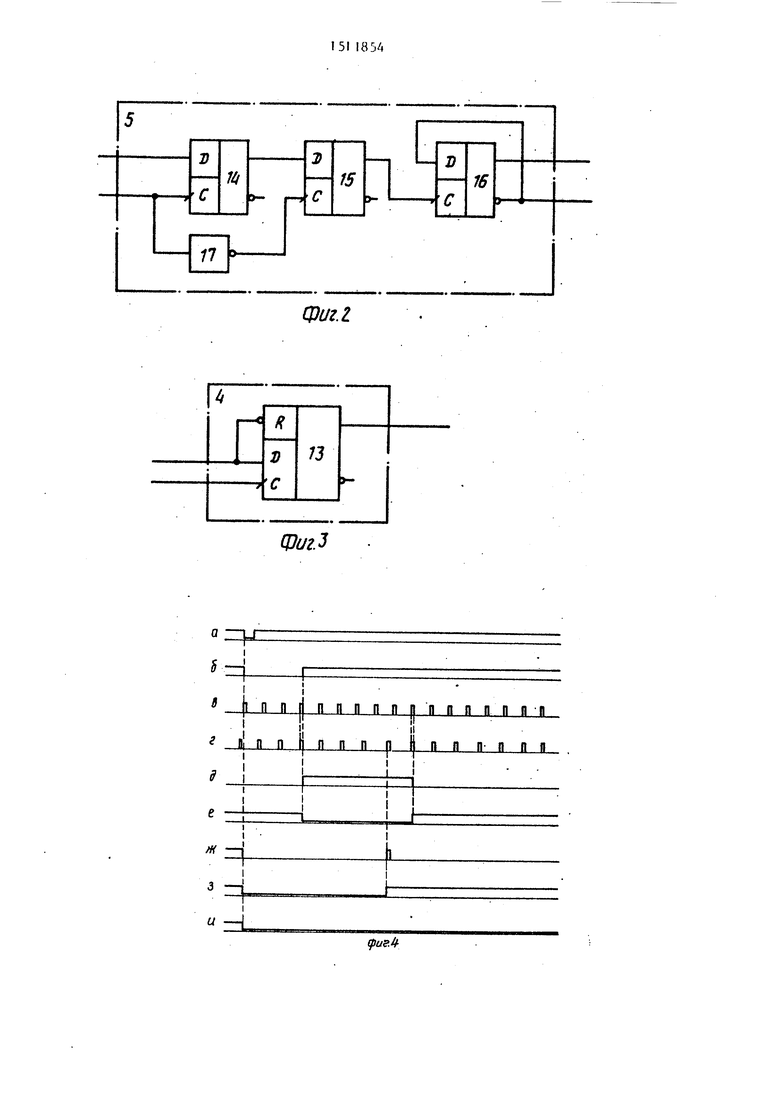

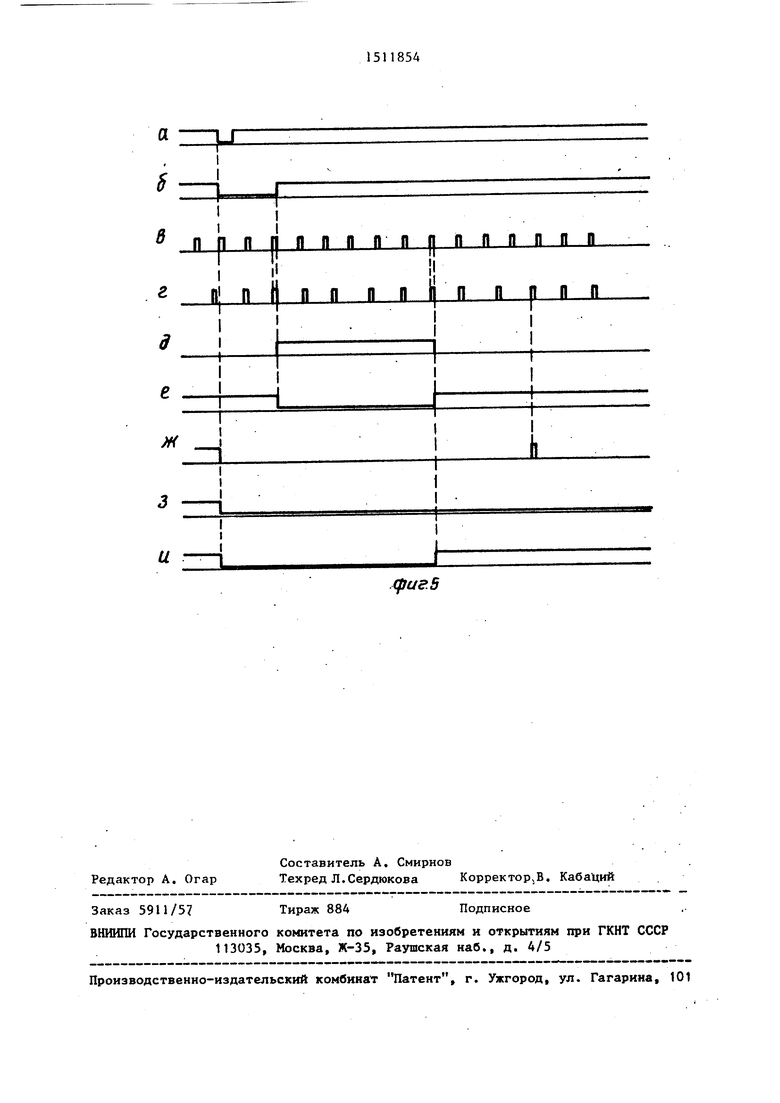

На фиг. 4 и 5 обозначены: а - импульс на шине 3; б импульс на выходе блока 4; в - импульс эталонной частоты на первой входной шине 1;

г - импульсы контролируемой частоты на второй входной шине 2; д - импульс на первом выходе преобразователя 5J е - импульс на втором выходе преобразователя 5; ж - импульс на

выходе счетчика 7; з - сигнал на первой выходной шине 10; и - сигнал на второй выходной шине 11.

Устройство работает следующим образом.

Коэффициент пересчета счетчика 7 выбирается исходя из допустимого отклонения контролируемой частоты и численно равен

; . , f

N Hf

где N - емкость счетчика 7;

f-j - значение эталонной частоты;uf - допустимое отклонение конт,- ролируемой частоты.

Импульс Пуск, проходящий на шину 3 (фиг. 4а, 5а) устанавливает на . выходе блока 4 ниэкий уровень (фиг. 4б, 5б), который устанавливает;

счетчик 7 и триггеры 8 и 9 в нуле.вое состояние (фиг. 4ж, з, и, 5ж,

3, и), Импульсы контролируемой и

эталонной частот (фиг. 4в, г, 5в,

г), поступающие на входы преобразователя 5, преобразуются последним в импульс, равный по. длительности периоду разностной частоты входных импульсных последовательностей (фиг. 4д, е, 5д, е). Передний фронт

данного импульса устанавливает на выходе блока 4 высокий уровень, прекращая принудительную установку счетчика 7 и триггеров 8 и 9 (фиг, 4б, 56). Одновременно импульс с первого

выхода преобразователя 5 разрешает прохождение через элемент И 6 на счетчик 7 иьтульсов эталонной частоты (фиг. 4д, 5д). Если импульс на выходе счетчика 7 появится раньше.

51

чем закончится импульс на выходе преобразователя 5, то триггер 8 изменяет свое состояние и на выходной шине 10 появляется высокий логический уровень (фиг. 4з), что свидетельствует о том, что отклонение контролируемой частоты от эталонной меньше допустимого отклонения. Если импульс на выходе преобоазовате- ля 5 кончится раньгае, чем появится импульс на выходе счетчика 7, то триггер 9 изменяет свое состояние и на выходной шине 11 появляется высокий уровень (фиг. 5и), что свидетельствует о том, что отклонение контролируемой частоты больше допустимого отклонения.

Предлагаемое устройство по сравнению с известным обеспечивает повышение быстродействия при сохранении точности контроля. В известном устройстве для получения относительной погрешности не более сГ время контроля должно быть не менее периодов разностной частоты. Например, для получения сР 0,5 необхо- димо не менее 200 периодов разностной частоты о В устройстве по изобретению продолжительность контроля составляет не более двух периодов :р,азностной частоты.

Формула изобретения

образойятель импульсов, первый и второй входы которого соединены соответственно с первой и второй входными шинами устройства, первый выход - с вторым входом элемента И, второй выход - с С-входом второго триггера, D-вход которого подключен к инверсному выходу первого

0 триггера, D-вход которого соединен с инверсным выходом второго триггера, причем входы обнуления обоих триггеров и счетчика импульсов подключены к выходу блока синхрониза5 ции, прямой выход второго триггера соединен с второй выходной шиной, а первый выход преобразователя импульсов соединен с вторым входом блока синхронизации.

0 2. Устройство по п. 1, отличающееся тем, что блок синхронизации выполнен в виде и-три1- гера, R- и D-входы которого объединены и являются первым входом бло-

5 ка синхронизации 1, С-вход является вторым входом блока синхронизации, а прямой выход D-триггера является выходом блока синхронизации.

J D-триггера, инверсный выход и D-вход которого соединены с вторым выходом преобразователя импульсов, при этом первым выходом преобразователя им пульсов является прямой выход третьеи

ГО D-триггера, первый вход преобразователя импульсов соединен с D-входом первого D-триггера, С-вход которого является вторым входом преобразователя импульсов и соединен через инвертор с С-входом второго D-тригге- ря„

Iff

15

Фиг2

сриг.

16

(pa г 5

Авторы

Даты

1989-09-30—Публикация

1987-10-26—Подача