со С

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР С ПРЕДУСТАНОВКОЙ ЧАСТОТЫ | 1997 |

|

RU2121749C1 |

| Устройство фазирования шкалы времени электронных часов | 1990 |

|

SU1746356A1 |

| Преобразователь угол-код | 1988 |

|

SU1596461A1 |

| Устройство фиксации переходов через нуль периодического сигнала | 1984 |

|

SU1187145A1 |

| Преобразователь код-временной интервал | 1986 |

|

SU1361721A1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

| Устройство для измерения перемещений | 1986 |

|

SU1357695A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1140248A1 |

| ЖДУЩИЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1993 |

|

RU2047939C1 |

Изобретение относится к автоматике, вычислительной технике и может быть использовано в контрольно-измерительных системах для проверки электронных модулей и блоков. Целью изобретения является повышение точности преобразования. В преобразователь, содержащий генератор импульсов, счетчик импульсов, три D-триггера и RS-триггер, введены четвертый D-триггер, два дешифратора, элемент ИЛИ-НЕ и четыре элемента ИЛИ. Это позволяет начало и конец преобразуемого временного интервала формировать передним фронтом выходных импульсов с одного и того же D-триггера. Таким образом, исключена задержка выходного сигнала относительно импульсов эталонной частоты и устранены погрешности перехода при формировании последовательных временных интервалов, что в конечном счете повышает точность преобразования. 3 ил.

Изобретение относится к автоматике. вычислительной и импульсной технике и может быто использовано в контрольно-изме- ригельных системах для проверки электронных модулей и блоков.

Цепью изобретения является повышение точности преобразования.

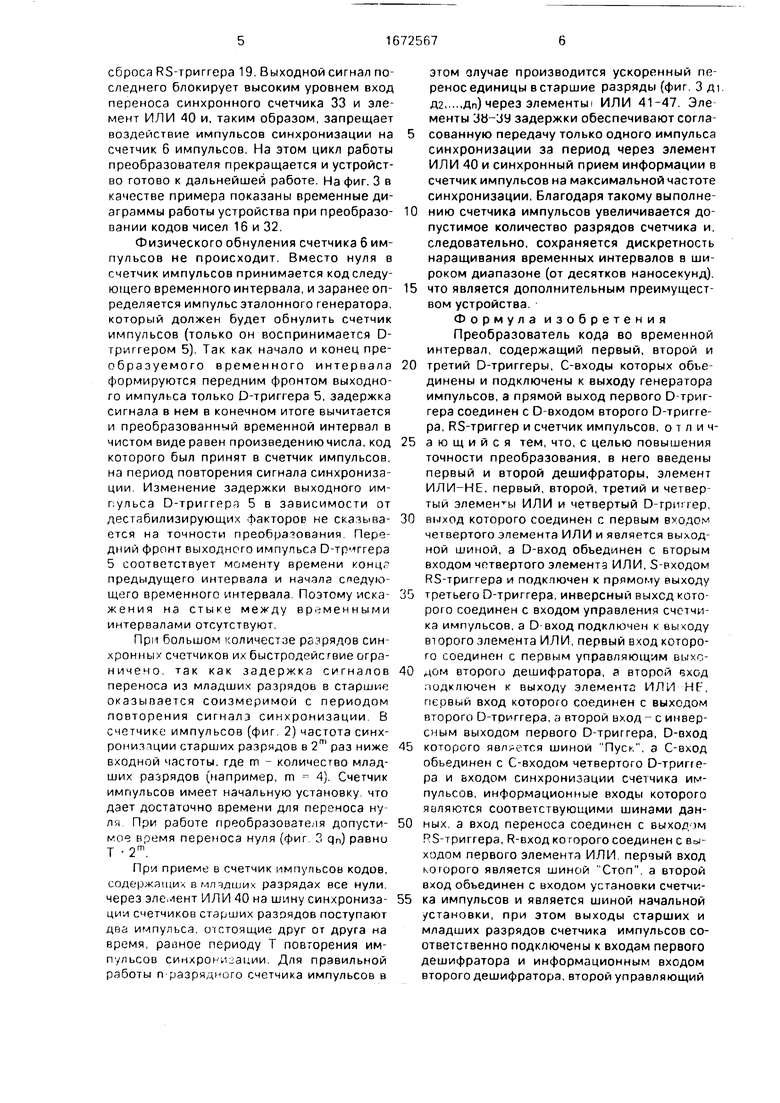

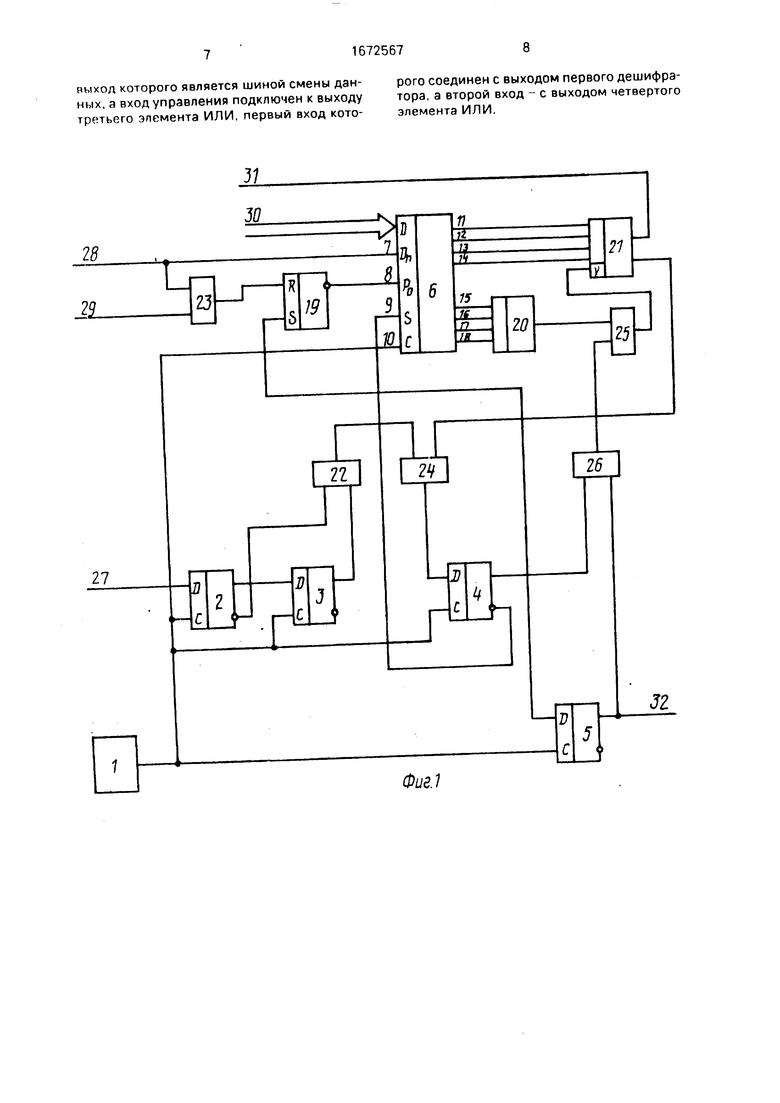

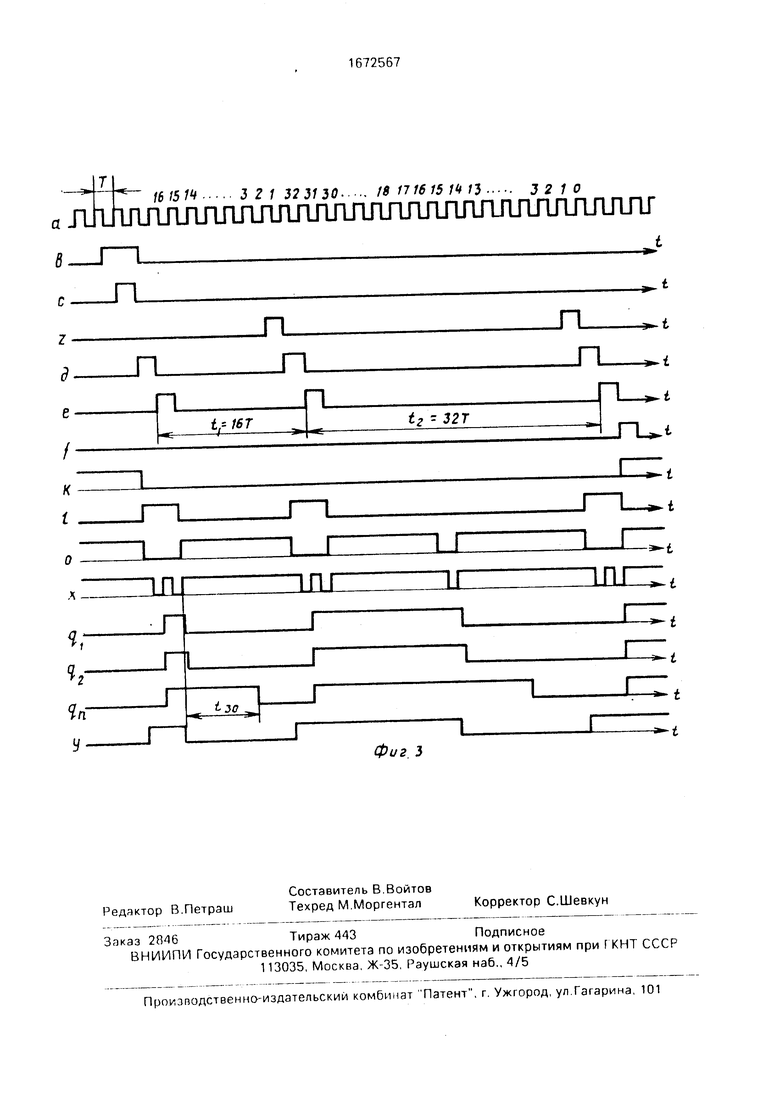

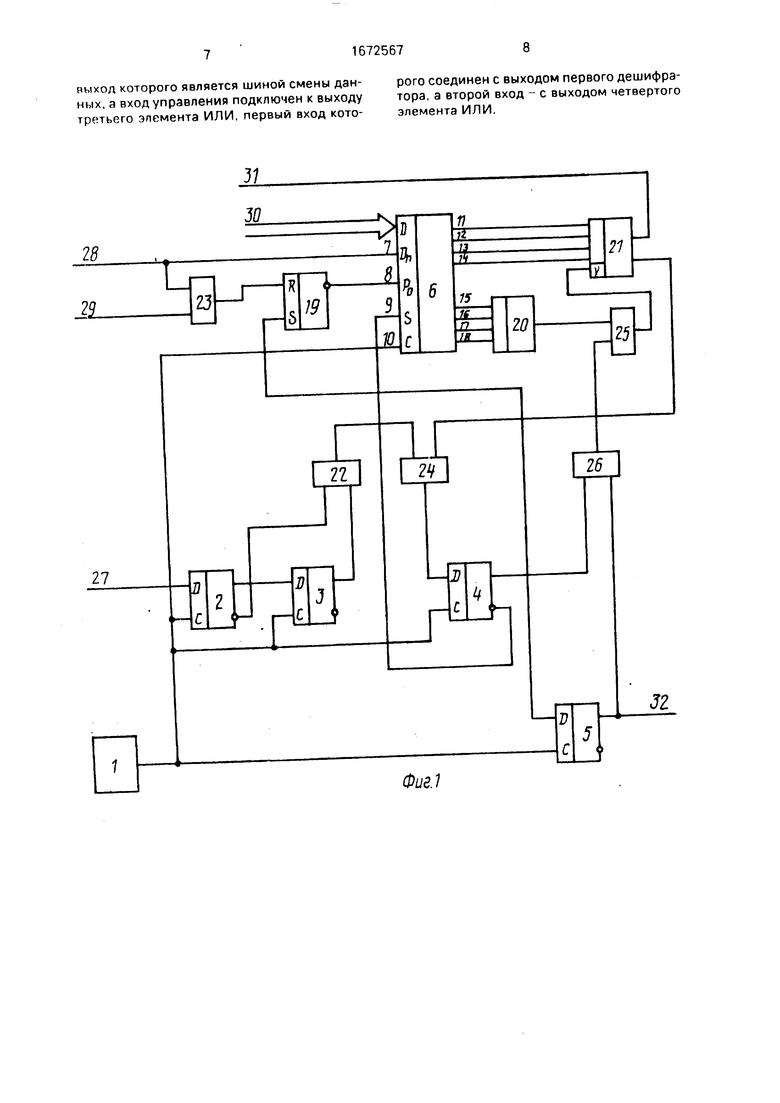

На фиг. 1 представлена структурная схема преобразователя, на фиг 2 -- структурная схема счетчика импульсов; на фиг. 3 - временные диаграммы работы преобразователя.

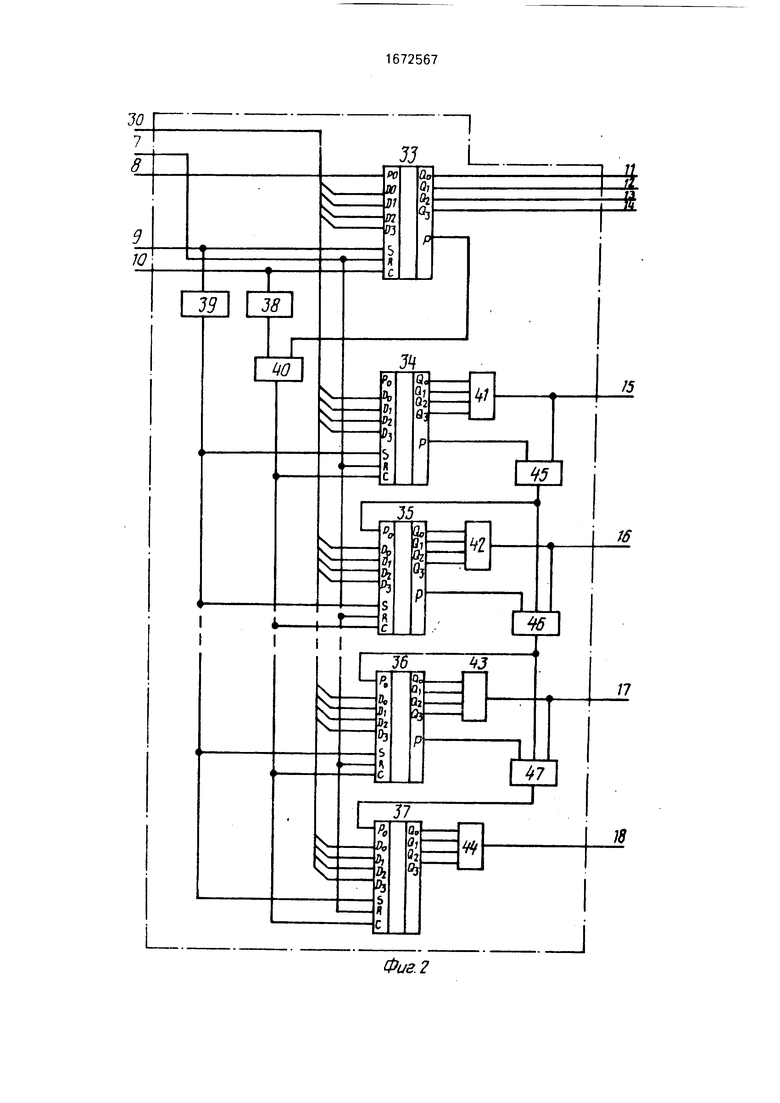

Преобразователь (фиг. 1) содержит генератор 1 импульсов, D-триггеры 2 - 5, п- разрядный двоичный счетчик 6 импульсов с входом 7 установки в О, входом 8 переноса, входом 9 управления режимом работы, входом 10 синхронизации выходами 11-14 младших разрядов и выходами 15-18 старших разрядов, RS-триггер 19. дешифратор 20 (нуля старших разрядов счетчика импульсов), дешифратор 21 (состояния младших разрядов счетчика импульсов) элемент ИЛИ-НЕ 22, элементы ИЛИ 23 - 26, шину Пуск 27, шину 28 начальной установки, шину 29 Стоп, шину 30 данных, шину З1 смены данных и выходную шину 32

Счетчик 6 содержит синхронные четырехразрядные двоичные счетчики 33-37, элементы 38 и 39 задержки, элементы ИЛИ 40-47 (элементы 40-44 выполнены в виде элементов ИЛИ МОНТАЖНОЕ)

Преобразователь работает следующим образом.

Сигналом начальной установки по шине 28 преобразователь устанавливается в кс ходное состояние. Высоким уровнем сигнала (фиг. 3 (с) с инверсного выхода RS-триггера 19 по входу 8 переноса счетчика 6 импульсов блокируется воздействие импульсов эталонной частоты на синхронный счетчик 33, высокий уровень выходного сигО

XI ю ел о VJ

нала переноса которого блокирует элемент ИЛИ 40. Устанавливается во времени сигнал переноса О на входах переноса синхронных двоичных счетчиков . По импульсу пуска (фиг. ЗЬ) на информационном входе D-григгера 2 устанавливается 1. По переднему фронту следующего за этим импульса по входу синхронизации D- триггер 2 устанавливается в состояние 1, следующим импульсом синхронизации D- триггер 3 устанавливается в состояние 1. На выходе элемента ИЛИ-НЕ 22 формируется импульс (фиг. 3 с) привязки к импульсам синхронизации, который через элемент ИЛИ 24 поступает на информационный вход D-триггера 4. Благодаря продвижению 1 сигналами синхронизации формируются импульсы на выходах D-триггеров 4 (фиг. 3 d) и 5 (фиг. 3 е). Импульсы с выходов D-триггера 4 подаются на вход 9 управления режимом работы счетчика 6 импульсов и на вход установки RS-триггера 19. При этом счетчик 6 импульсов переводится в режим параллельного приема информации с шины 30 данных.

Сигнал с инверсного выхода RS-триггера 19 низким уровнем (фиг. 3 k) поступает не вход переноса счетчика 6 импульсов. На выходе переноса синхронного счетчика 33 и на входе элемента ИЛИ 40 устанавливается низкий уровень (фиг. 3 о). Передним фронтом следующего за этим импульса синхронизации, действующим по входу 10 (фиг. 3 а) счетчика 6 импульсов и на выходе элемента ИЛИ 4.0 (фиг. 3 х), информация (например, код числа 16) с шины 30 данных параллельно вводится в счетчик 6 импульсов. Этим же по времени импульсом синхронизации, действующим по пходу синхронизации D-триггера 5, последний переключается с состояние 1 и на его выходе под действием следующего импульса синхронизации формируется импульс (фиг. 3 е) длительностью, равной периоду повторения импульсов синхронизации.

Передний фронт выходного сигнала D- триггера 5 определяет начало первого временного интервала. На выходе элемента ИЛИ 26 формируется импульс (фиг. 3 е) длительностью, равной двум периодам повторения импульсов синхронизации. Этот импульс воздействует через элемент ИЛИ 25 на вход управления дешифратора 21 состояния младших разрядов счетчика импульсов и запрещает работу дешифратора 21 на время приема информации в счетчик 6 импульсов, что исключает возможность появления сигнала смены данных или сиг нала дешифрации состояния младших разрядов при записи в них кода числа 2. После

того, как преобразуемый код будет принят в счетчик 6 импульсов и снят низкий уровень сигнала с входа 9 управления режимом работы, счетчик 6 импульсов перейдет в режим вычитания.

По мере вычитания из числа в счетчике под воздействием импульсов эталонной частоты генератора 1 вначале обнуляются старшие разряды счетчика, причем во все

младшие разряды записывается информация Г. Выходной сигнал дешифратора 20 нуля (фиг. 3 у) низким уровнем через элемент ИЛИ 25 поступает на вход управления дешифратора состояния младших разрядов,

разрешая работу последнего. Первым появляется и поступает на шину 31 сигнал смены данных, по которому на шину 30 данных подается код следующего временного интервала. Состояние младших разрядов счетчика 6 импульсов, которое при этом дешифруется, соответствует числу щ, удовлетворяющему условию

где tB - время выборки информации на шину данных;

Т - период повторения сигнала синхронизации.

На втором выходе дешифратора 21 появляется импульс (фиг. 3 z), когда в счетчике 33 число 2. Этот импульс поступает через элемент ИЛИ 24 на информационный вход D-триггера 4.

Под действием синхронизации появление импульсов на выходах D-триггеров 4 и 5 соответствует записи в счетчике 33 чисел 1 и 0. Импульс с инверсного выхода D-триггера 4 снова переводит счетчик 6 импульсов по входу 9 управления режимом работы в

режим приема информации. Очередным импульсом синхронизации, который должен обнулить счетчик 6 импульсов, код следующего временного интервала с шины 30 дан ных записывается в счетчик 6 импульсов.

Передний фронт импульса на выходе D- триггера 5 и выходной шине 32 преобразователя соответствует моменту времени конца первого временного интервала и начала следующего временного интервала.

0 Начинается преобразование кода в следующий временной интервал.

Преобразование запрограммированной последовательности временных интервалов продолжается до тех пор, пока по

5 заднему фронту выходного сигнала D-триггера 5 не будет сформирован программным устройством управления (не показано) сигнал Стоп (фиг. 3 f). который поступает по шине 29 через элемент ИЛИ 23 на вход

сброса RS-триггера 19. Выходной сигнал последнего блокирует высоким уровнем вход переноса синхронного счетчика 33 и элемент ИЛИ 40 и. таким образом, запрещает воздействие импульсов синхронизации на счетчик 6 импульсов. На этом цикл работы преобразователя прекращается и устройство готово к дальнейшей работе. На фиг. 3 в качестве примера показаны временные диаграммы работы устройства при преобразовании кодов чисел 16 и 32.

Физического обнуления счетчика б импульсов не происходит. Вместо нуля в счетчик импульсов принимается код следующего временного интервала, и заранее определяется импульс эталонного генератора, который должен будет обнулить счетчик импульсов (только он воспринимается D- триггером 5) Так как начало и конец преобразуемого временного интервала формируются передним фронтом выходного импульса только D-триггера 5, задержка сигнала в нем в конечном итоге вычитается и преобразованный временной интервал в чистом виде равен произведениючисла, код которого был принят в счетчик импульсов, на период повторения сигнала синхронизации Изменение задержки выходного импульса D-триггеря 5 в зависимости от дестабилизирующих Факторов не скатывается на точности преобразования Передний франт выходного импульса D-трчггера 5 соответствует моменту времени концг предыдущего интервала и начала следующего временного интервала Поэтому иска- жения на стыке между временными интервалами отсутствуют

При большом количестве разрядов синхронных счетчиков их быстродействие огра- ничечо так как задержка сигналов переноса из младших разрядов в старшие оказывается соизмеримой с периодом повторения сигналэ синхронизации В счетчике импульсов (фиг 2) частота синх- ронипции старших разрядов в 2Ш раз ниже входной частоты, где m - количество младших разрядов (например, m - 4) Счетчик импульсов имеет начальную установку что дает достаточно времени для переноса ну л. При работе преобразователя допустимое время переноса нуля (фиг 3 qn) равно Т -2т.

При приеме в счетчик импульсов кодов, содержащий вмлчдших разрядах все нули через элемент ИЛИ 40 на шину синхронизации счетчиков старших разрядов поступают два импульса отстоящие друг от друга на время, равное периоду Т повторения импульсов синхронизации Для правильной работы п разрядного счетчика импульсов в

этом олучае производится ускоренный перенос единицы в старшие разряды (фиг Зд1

Д2дп) через элементы ИЛИ 41-47. Эле

менты ЗЬ-ЗУ задержки обеспечивают согла- 5 сованную передачу только одного импульса синхронизации за период через элемент ИЛИ 40 и синхронный прием информации в счетчик импульсов на максимальной частоте синхронизации. Благодаря такому выполне- 0 нию счетчика импульсов увеличивается допустимое количество разрядов счетчика и, следовательно, сохраняется дискретность наращивания временных интервалов в широком диапазоне (от десятков наносекунд), 5 что является дополнительным преимуществом устройства

Формула изобретения Преобразователь кода во временной интервал, содержащий первый, второй и

0 третий D-триггеры, С-входы которых объединены и подключены к выходу генератора импульсов, а прямой выход первого D-триггера соединен с D-входом второго D-триггера, RS-триггер и счетчик импульсов, о т л и ч5 ающийся тем, что, с целью повышения точности преобразования, в него введены первый и второй дешифраторы, элемент ИЛИ-НЕ. первый, второй, третий и четвертый элементы ИЛИ и четвертый D-триггер,

0 выход которого соединен с первым входом четвертого элемента ИЛИ и является выходной шиной, а D-вход объединен с вторым входом четвертого элемента ИЛИ, S-входом RS-триггера и подключен к прямому выходу

5 третьего D-триггера, инверсный выход которого соединен с входом управления счетчика импульсов, a D вход подключен к выходу второго элемента ИЛИ, первый вход которого соединен с первым управляющим выхп0 дом второго дешифратора, а второй вход подключен к выходу элемента ИЛИ НЕ-, первый вход которого соединен с выходом второго D-тоиггера, а второй вход - с инверсным выходом первого D-триггера, D-вход

5 которого является шиной Пуск, а С-вход объединен с С-входом четвертого D-триггера и входом синхронизации счетчика импульсов, информационные входы которого являются соответствующими шинами дан0 ных а вход переноса соединен с выход м PS-триггера, R-вход ко горого соединен с вы- хэдом первого элемента ИЛИ перчый вход которого является шиной Стоп а второй вход объединен с входом установки счетчи5 ка импульсов и является шиной начальной установки, при этом выходы старших и младших разрядов счетчика импульсов соответственно подключены к входам первого дешифратора и информационным входом второго дешифратора, второй управляющий

выход которого является шиной смены данных, а вход управления подключен к выходу третьего элемента ИЛИ, первый вход которого соединен с выходом первого дешифратора, а второй вход - с выходом четвертого элемента ИЛИ.

Фиг. 2

Фиг J

| Преобразователь кода в суммарный интервал времени | 1983 |

|

SU1106012A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь код-временной интервал | 1983 |

|

SU1115225A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-08-23—Публикация

1988-01-07—Подача