/4

(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Пересчетная схема в коде Фибоначчи | 1990 |

|

SU1757098A1 |

| Пересчетная схема в коде Фибоначчи | 1991 |

|

SU1800612A1 |

| Счетчик импульсов в максимальных кодах Фибоначчи | 1990 |

|

SU1720157A1 |

| Модуль пересчетной схемы в минимальном Р-коде Фибоначчи | 1988 |

|

SU1511862A1 |

| Пересчетная схема в коде Фибоначчи | 1991 |

|

SU1780188A1 |

| Счетчик импульсов в максимальных кодах Фибоначчи | 1988 |

|

SU1531215A1 |

| Счетчик импульсов в Р-кодах Фибоначчи | 1991 |

|

SU1803974A1 |

| Пересчетное устройство в коде Фибоначчи | 1990 |

|

SU1725389A1 |

| Кольцевой счетчик | 1987 |

|

SU1437995A2 |

| Счетчик импульсов в максимальных Р-кодах Фибоначчи | 1988 |

|

SU1511861A1 |

Изобретение относится к импульсной технике и может быть использовано для пересчета импульсов в минимальном и максимальном кодах Фибоначчи при Р 1. Счетчик импульсов содержит 3 элемента памяти на D-триггерах, вход сброса (4), тактовый вход (15), 2 управляющих входа (6, 7). 2 управляющих выхода (8, 9), 2 элемента И (10, 11), выход переноса (12), каждый элемент памяти дополнительно содержит 2 элемента 4И-ИЛИ (13, 14). 3 элемента И (16, 17, 18), элемент ИЛИ (19), 4 элемента НЕ (20-23), шину выбора режима (24), элемент 5И-ИЛИ

vj

СЬ Ю О 00

Изобретение относится к импульсной технике и может быть использовано дня пересчета импульсов в минимальном и максимальном кодах Фибоначчи при Р 1,

Известна пересчетная схема в коде Фибоначчи, содержащая первый, второй и третий элементы памяти, вход сброса, тактовый вход, первый и второй элементы И, элементы ИЛИ, элемент НЕ, управляющий вход, управляющий выход и выход переноса.

Недостатком этого устройства являются узкие функциональные возможности, обусловленные возможностью пересчета импульсов только в минимальных Р 1 кодах Фибоначчи.

Наиболее близким по технической сущности к предлагаемому является счетчик импульсов в максимальных кодах Фибоначчи, содержащий первый, второй и третий элементы памяти, вход сброса, тактовый вход, первый и второй управляющие входы, первый и второй управляющие выходы, первый и второй элементы И, выход переноса, причем вход сброса счетчика соединен с входами сброса всех элементов памяти, тактовые входы которых и первый вход первого элемента И соединены с тактовой шиной счетчика, прямые выходы первого, второго и третьего элементов памяти соединены соответственно с первым, вторым и третьим входами второго элемента И, выход которого соединен со вторым входом первого элемента И, первый управляющий выход соединен с пряным выходом первого элемента памяти, а второй - с инверсным выходом второго элемента памяти. Счетчик содержит также первый, второй, третий, четвертый и пятый элементы И-НЕ.

Недостатками этого устройства также являются узкие функциональные возможности, обусловленные возможностью пересчета импульсов только в максимальных Р - 1 кодах Фибоначчи.

Цель изобретения - расширение функциональных возможностей и области применения путем обеспечения пересчета в минимальных и максимальных Р 1 кодах Фибоначчи.

Поставленная цель достигается тем, что счетчик импульсов в кодах Фибоначчи, содержащий первый, второй и третий элементы памяти, вход сброса, тактовый вход, первый и второй управляющие входы, первый и второй управляющие выходы, первый и второй элементы И, выход переноса, причем, вход сброса счетчика соединен с входами сброса всех элементен памяти, тактовые входы которых и первый вход первого элемента И соединены г, тактовой шиной счетчика, прямые выходы первого, второго и третьего элементов памяти соединены соответственно с первым, вторым и третьим входами второго элемента И, выход которого

соединен со вторым входом первого элемента И, первый управляющий выход соединен с прямым выходом первого элемента памяти, а второй - с инверсным выходом второго элемента памяти, каждый элемент

0 памяти выполнен в виде D-триггера и дополнительно содержит первый и второй элементы 4И-ИЛИ, соединенные выходами с D-входами соответственно первого и второго триггеров, элемент 5И-ИЛИ, соединенно5 го выходом с D-входов третьего триггера, третий, четвертый и пятый элементы И. элемент ИЛИ, соединенный выходом с выходом переноса счетчика, первый, второй, третий и четвертый элементы НЕ, шину вы0 бора режима, причем прямой выход первого триггера соединен с первыми входами первой и второй структуры И второго элемента 4И-ИЛИ, с первыми входами третьей и пятой структуры И элемента 5И-ИЛИ и со вто5 рым входом третьего элемента И, соединенного выходом с первым входом элемента ИЛИ, а его инверсный выход - с первыми входами первой и второй структуры И первого элемента 4И-ИЛИ, со вторыми

0 входами третьей структуры И второго элемента 4И-ИЛИ и второй структуры И элемента 5И-ИЛИ. прямой выход второго триггера соединен с первыми входами третьей структуоы И перзого элемента 4И5 ИЛИ, третьей и четвертой структуры И второго элемента 4И-ИЛИ первой структуры И элемента 5И-ИЛИ и со вторыми входами третьей структуры И элемента 5И-ИЛИ и четвертого элемента И, а его инверсный вы0 ход - со вторыми входами первой структуры И первого элемента 4И-ИЛИ и второй структуры И второго элемента 4И-ИЛИ. прямой выход третьего триг гера соединен со вторыми входами четвертой структуры И второго

5 элемента 4И-ИЛИ и пятой структуры И элемента 5И-ИЛИ, с первыми входами второй и четвертой структуры И элемента 5И-ИЛИ v, с третьим входом третьего элемента И, а его инверсный выход - со вторыми входами

0 третьей структуры И первого элемента 4И- h/Ш и первой структуры И второго элемента 4И-ИЛИ. второй и третий входы элемента ИЛИ соединены с выходами соответственно четвертого и первого элементов И, а выход

5 второго элемента И - с третьим входом пятого элемента И, первый и второй входы которого соединены соответственно с первым и вторым управляющими входами счетчика, вход первого элемента НЕ соединен с выходом пятого элемента И, с первым входом четвертой структуры И первого элемента 4И-ИЛИ и с третьим входом четвертой структуры И элемента 5И-ИЛИ, а его выход - с третьим входом четвертой структуры И второго элемента 4И-ИЛИ, вход второго элемента НЕ соединен с выходом второго элемента И, а его выход - со вторым входом четвертой структуры И элемента 5И-ИЛИ, вход третьего элемента НЕ соединен с третьим входом четвертого элемента И и с первым управляющим входом счетчика, а его выход- со вторым входом первой структуры И элемента 5И-ИЛИ и с четвертым входом третьего элемента И, третьи входы первых структур И первого и второго элементов 4И-ЙЛИ, первой и второй структуры И элемента 5И-ИЛИ, пятый вход третьего элемента И, и четвертый вход четвертого элементов И, вход четвертого элемента НЕ соединены с шиной выбора режима, а вторые входы второй и четвертой структур И первого элемента 4И-ИЛИ, третьи входы третьей структуры И первого элемента 4И- ИЛИ, второй и третьей структуры И второго элемента 4И-ИЛИ, третьей и четвертой структуры И элемента 5И-ИЛИ, четвертые входы четвертой структуры И второго элемента 4И-ИЛИ и пятой структуры И элемента 5И-ИЛИ и второго элемента И соединены с выходом четвертого элемента НЕ, а первые входы третьего и четвертого элементов И - с тактовой шиной счетчика.

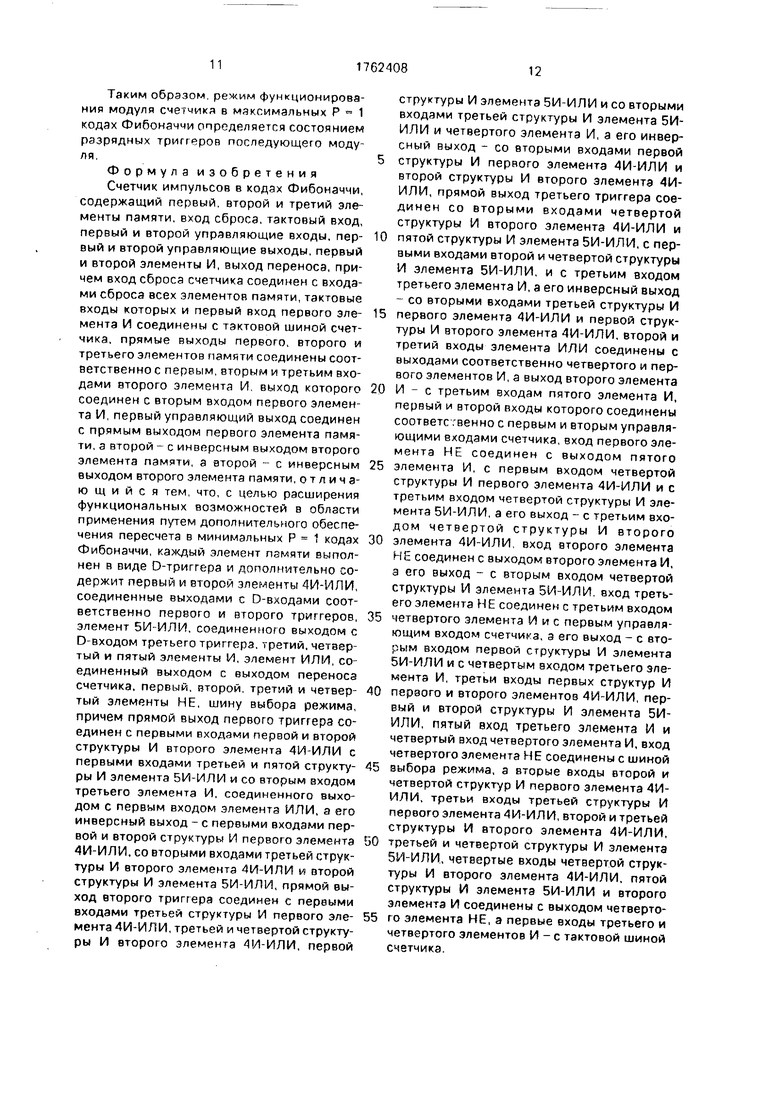

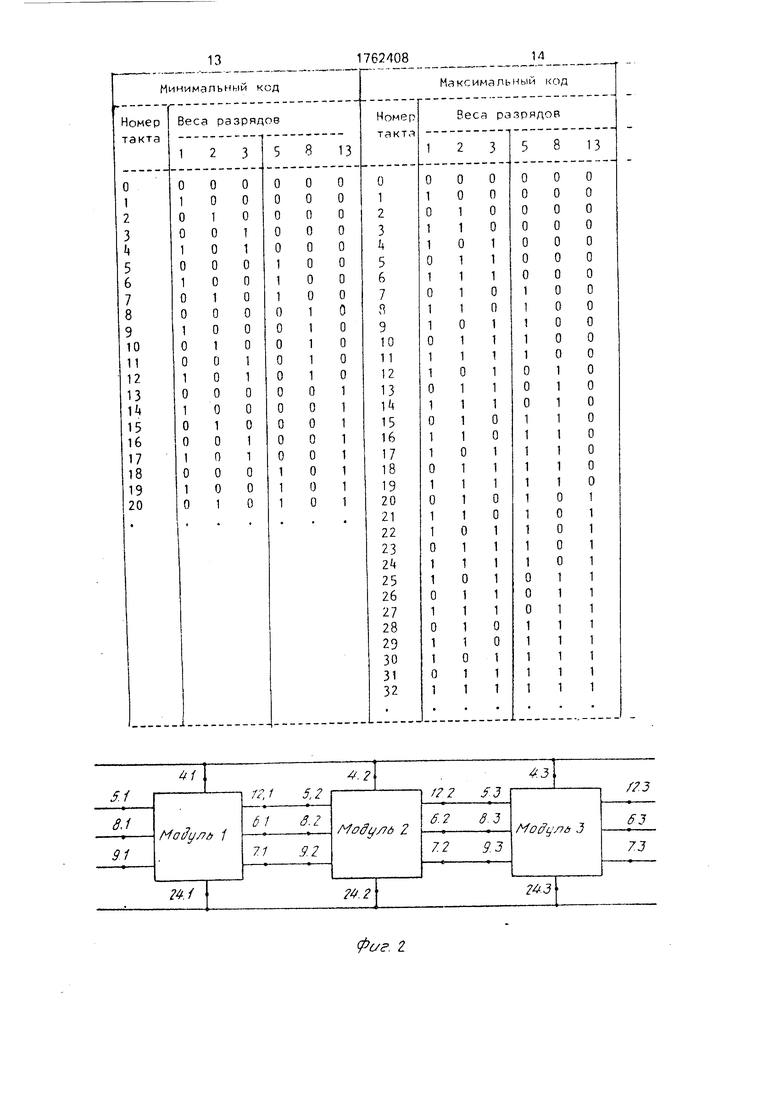

На фиг. 1 представлена функциональная схема предлагаемого счетчика импульсов; на фиг, 2 - схема подключения ряда модулей счетчика импульсов для увеличения разрядности пересчета.

Счетчик импульсов в кодах Фибоначчи содержит первый 1, второй 2 и третий 3 D-триггера, вход 4 сброса, тактовую шину 5, первый 6 и второй 7 управляющие входы, первый 8 и второй 9 управляющие выходы, первый 10 и второй 11 элементы И, выход 12 переноса, первый 13 и второй 14 элементы 4И-ИЛИ, элемент 5И-ИЛИ 15, третий 16, четвертый 17, пятый 18 элементы И, элемент ИЛИ 19, первый 20, второй 21, третий 22 и четвертый 23 элементы НЕ, шина 24 выбора режима.

Счетчик импульсов функционирует следующим образом.

Для увеличения разрядности общей схемы пересчета ряд модулей счетчика объединяется следующим образом. Первый б и второй 7 управляющие входы данного модуля соединяются соответственно с первым 8 и вторым 9 управляющими выходами последующего модуля, а выход 12 переноса - с тактовым входом 5 последующего модуля, входы 4 сброса объединяются (фиг. 2). На

первый управляющий вход 6 старшего модуля прикладывается нулевой логический потенциал, а на второй управляющий вход 7 - единичный логический потенциал. 5В исходном состоянии триггеры 1, 2 и 3

модулей счетчиков, объединенных для увеличения разрядности пересчета, находятся в нулевых состояниях.

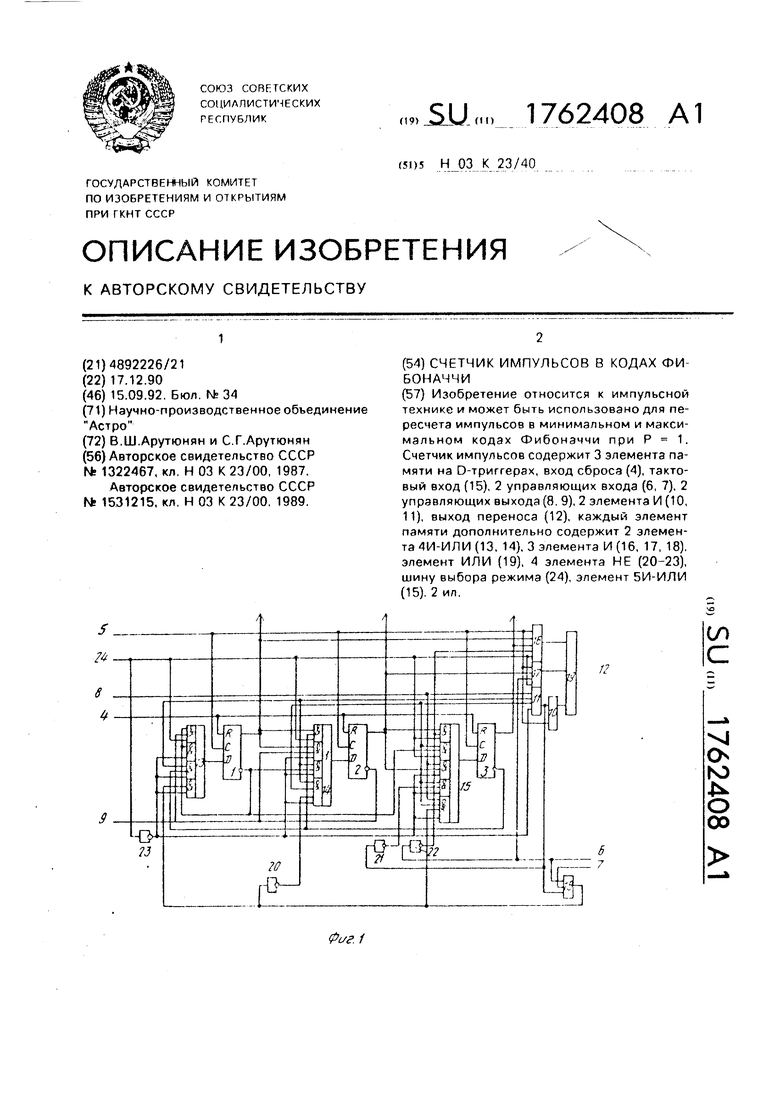

Для работы устройства в режиме пере10 счета импульсов в минимальном Р 1 коде Фибоначчи на шину 24 выбора режима прикладывается единичный логический потенциал, На выходе первого элемента 4И-ИЛИ 13 присутствует единичный логический по15 тенциал, так как на первом и втором входах его первой структуры И присутствуют единичные логические потенциалы с инверсных выходов первого 1 и второго 2 триггеров. На выходах элементов 4И-ИЛИ 14 и 5И-ИЛИ 15

0 присутствуют нулевые логические потенциалы (фиг. 1). По поступлении первого тактового импульса на выходе общей, содержащей два модуля, устанавливается код 100000 (см. таблицу кодов, описывэю5 щих работу устройства в минимальных и максимальных Р 1 кодах Фибоначчи.

Перед поступлением второго тактового импульса на выходе элемента 4И-ИЛИ 14

0 присутствует единичный логический потенциал, так как на первом и втором входах его первой структуры И присутствуют единичные логические потенциалы с прямого выхода первого триггера 1 и с инверсного выхода

5 третьего триггера 3 (фиг. 1). На выходах элементов 4И-ИЛИ 13и5И-ИЛИ 15 присутствуют нулевые логические потенциалы. Второй тактовый импульс устанавливает на выходе общей схемы код 010000 (см. таблицу).

0 Перед поступлением третьего тактового импульса на выходе элемента 5И-ИЛИ 15 присутствует единичный логический потенциал, так как на его первом и втором-входах его первой структуры присутствуют единич5 ные логические потенциалы с прямого выхода второго триггера 2 и с выхода элемента НЕ 22. На выходах элементов 4И-ИЛИ 13 и 14 присутствуют нулевые логические потенциалы. Третий тактовый импульс устанавли0 вает на выходе общей схемы код 001000 (см. таблицу).

Перед поступлением четвертого тактового импульса на выходах элементов 4И- 5 ИЛИ 13 и 5И-ИЛИ 15 присутствуют единичные логические потенциалы, тах как на первом и втором входах первой структуры И элемента 4И-ИЛИ 13 и второй структуры И элемента 5И-ИЛИ 15 присутствуют единичные логические потенциалы (фиг. 1).

По поступлении четвертого тактового импульса на выходе общей схемы устанавливается код 101000 (см. таблицу).

На втором, третьем, четвертом и пятом входах третьего элемента И 16 присутствуют единичные логические потенциалы соответственно с прямого выхода первого триггера 1, с прямого выхода третьего триггера 3, с выхода элемента НЕ 22 и с шины 24 выбора режима. На выходах элементов 4И-ИЛИ 13 и И и элемента 5И-ИЛИ 15 первого модуля и на выходах элементов 4И- ИЛИ 14 и 5И-ИЛИ 15 второго модуля присутствуют нулевые логические потенциалы, а на выходе элемента 4И-ИЛ / 13 второго модуля - единичный логический потенциал (фиг. 1Х Таким образом, пятый тактовый импульс поступает на первый вход элемента И 16 первого модуля и проходит через элемент ИЛИ 19 и выход 12 переноса первого модуля поступает на тактовый вход 5 второго модуля. На выходе общей схемы устанавливается код 000100.

В этом случае происходит изменение режима работы первого модуля, так как на первом управляющем выходе 8 второго модуля, на первом управляющем входе б, и на втором входе элемента И 17 первого модуля устанавливается единичный логический потенциал, а на втором входе первой структуры И элемента 5И-ИЛИ 15 - нулевой логический потенциал. Первоэ пересчетное устройство в шестом и седьмом тактах функционирует аналогично первому и второму тактах.

Перед поступлением чосьмого тактового импульса на втором и третьем Р.ХОДЭХ элемента И 17 первого моду/in присутствуют единичные логические потенциалы с выхода второго триггера 2 и с шины 24 выбора режима работы. На выходах элементов AIA- ИЛИ 13 и 14 и 5И-ИЛИ 15 первого модуля и на выходах элементов 41/1-И Л М 13 и 5И-ИЛИ 15 второго модуля присутствуют нулевые . логические потенциалы, а на выходе элемента 41Л-ИЛИ 14 - единичный логический потенциал. Восьмой тактовый импульс проходит через элементы Л 17, ИЛИ 19 и выход 12 переноса первого модуля поступает на тактовый вход 5 второ. о модуля, Нэ выходе общей схемы устанавливается код 000010 (см. таблицу).

В дальнейшем функционирование счетчика в режиме пересчета з минимальном Р « 1 коде Фибоначчи аналогично вышеописанному и периодически повторяется. Изменение режима работы данного модуля при пересчете в минимальных Р 1 кодах Фибоначчи обусловлено состоянием первого 1 триггера последующего модуля.

Для работы устройства в режиме пересчета импульсов в максимальных Р 1 кодах Фибоначчи на шину 24 выбора режима прикладывается нулевой логический потенциал.

В исходном состоянии триггеры 1, 2 и 3 модулей счетчиков находятся в нулевых состояниях. На выходе элемента 4И-ИЛИ 13 первого модуля присутствует единичный ло0 гический потенциал, так как на первом и втором входах его второй структуры присутствуют единичные логические потенциалы соответственно с инверсного выхода первого триггера 1 и с выхода элемента НЕ 23

5 первого модуля. На выходах элементов 4И- ИЛИ 14 и 5И-ИЛИ 15 первого модуля присутствуют нулевые логические потенциалы. По приходу первого тактового импульса счетчик, содержащий два модуля, устанав0 ливается в состояние 100000.

При поступлении второго тактового импульса ня выходе элемента 4И-ИЛИ 14 присутствует единичный логический потенциал, так как на первом, втором и третьем входах

5 его второй структуры И присутствуют единичные логические потенциалы соответственно с прямого выхода первого триггера 1, с инверсного выхода второго триггера 2 и с выхода элемента НЕ 23. На выходах элемен0 тов 4И-ИЛИ 13 и 5И-ИЛИ 15 присутствуют нулевые логические потенциалы. Второй тактовый импульс устанавливает на выходе устройства код 010000.

Перед поступлением третьего тактового

5 импульса на выходах элементов 4И-1/1ЛИ 13 и 4И-ИЛИ 14 присутствуют единичные логические потенциалы, так как на первом и ето- озм входах структура И элемента 4И-ИЛИ 13 присутствуют единичные логические по0 тенциалы с инверсного выхода первого триггера 1 и с выхода элемента НЕ 23, а на первом, втором и третьем входах третьей структуры И элемента 4И-ИЛИ 14 -соответственно с прямого выхода второго триггера

5 2, с инверсного выхода первого триггера 1 и с выхода элемента НЕ 23. На выходе элемента 5И-ИЛИ 15 присутствует нулевой логический потенциал. Третий тактовый импульс устанавливает на выходе общей

0 схемы код 110000.

Перед поступлением четвертого тактового импульса на выходах элементов 4И- ИЛИ 13 и 5И-ИЛИ 15 присутствуют единичные логические потенциалы, так как

5 на первом, втором и третьем входах третьей структуры И элемента 4И-ИЛИ 13 присутствуют единичные логические потенциалы соответственно с прямого выхода второго триггера 2, с инверсного выхода третьего триггера 3 и с выхода элемента НЕ 23, а на

первом, втором и третьем входах третьей структуры И элемента 5И-ИЛИ первого модуля - соответственно с прямых выходов первого 1 и второго 1 триггеров и с выхода элемента НЕ 23. Четвертый тактовый импульс устанавливает на выходе общей схемы код 101000.

Перед поступлением пятого тактового импульса на выходах элементов 4И-ИЛИ 14 и 5И-ИЛИ 15 присутствуют единичные логические потенциалы, так как на первом, втором, третьем и четвертом входах четвертой структуры И элемента 4И-ИЛИ 14 присутствуют единичные логические потенциалы соответственно с прямых выходов второго 2 и третьего 3 триггеров, с выходов элементов НЕ 20 и 23, а на первом, второй и третьем входах четвертой структуры И элемента 5И- ИЛИ - с прямого выхода третьего триггера и с выходов элементов НЕ 21 и 23. Пятый тактовый импульс устанавливает на выходе общей схемы код 011000.

Перед поступлением шестого тактового импульса на выходах элементов 4И-ИЛИ 13 и 14, элемента 5И-ИЛИ 15 первого модуля присутствуют потенциалы логической единицы, так как на первом и втором входах второй структуры И элемента 4И-ИЛИ 13 присутствуют единичные логические потенциалы с прямого выхода второго триггера 2 и с инверсного выхода третьего триггера 3. на первом, втором и третьем входах - соответственно с прямого выхода второго триггера 2, с инверсного выхода первого триггера 1 и с выхода элемента НЕ 23, э на первом, втором и третьем входах четвертой структуры И элемента 5И-ИЛИ - соответственно с прямого выхода третьего триггера 3 и с выходом элементов НЕ 21 и 23. Шестой тактовый импульс устанавливает на выходе общей схемы код 111000.

На первом, второй, третьем и четвертом входах элемента И 11 присутствуют единичные логические потенциалы соответственно с прямых выходов первого 1, второго 2 и третьего 3 триггеров и с выхода элемента НЕ 23. Единичный логический потенциал с выхода элемента И 11 поступает нз второй вход элемента И 10. разрешая прохождение седьмого тактового импульса через элемент ИЛИ 19 на выход переноса 12 первого модуля и на тактовый вход 5 второго модуля и на третий вход элемента И 17 и на вход элемента НЕ 21 первого модуля. На выходе элемента 4И-ИЛИ 14 первого модуля присутствует единичный логический потенциал, так как на первом, втором третьем и четвертом входах его четвертой структуры И присутствуют единичные логические потенциалы соответственно с прямых выходов

второго 2 и третьего 3 триггеров и с выходов элементов НЕ 20 и 23 Нз выходе элемента 4И-ИЛИ 13 второго модуля присутствует единичный логический импульс, так как нз 5 первом и втором входах его второй структуры присутствуют единичные логические потенциалы с инверсного выхода первого триггера 1 и с выхода элемента НЕ 23. На выходах элементов 4И-ИЛИ 13и5И-ИЛИ 15 10 первого модуля и элементов 4И-ИЛИ 14 и 5И-ИЛИ 15 второго модуля присутствуют нулевые логические потенциалы. По приходу седьмого тактового импульса на выходе общей схемы устанавливается код 010100.

15В этом случае происходит изменение

пежима работы первого модуля, так как на пераом управляющем выходе 8 второго модуля устанавливается единичный логический потенциал, который поступает на

0 второй управляющий вход 6 первого модуля.

Первый модуль счетчика с восьмого по одиннадцатый такт функционирует аналогично его работе в тактах с третьего по ше5 стой.

Перед поступлением двенадцатого тактового импульса на выходах элементов 4И- ИЛИ 13 к 5И-ИЛИ 15 первого модуля присутствуют потенциалы логической еди0 ницы, так как на первом и втором входах четвертой структуры И элемента 4И-ИЛИ 13 присутствуют единичные логические потенциалы соответственно с выходов элементов И 17 и НЕ 23, а на первом, второй и третьем

5 входах пятой структуры И элемента 5И-ИЛИ 15 - с прямых выходов первого 1 и третьего 3 триггеров и с выхода элемента И 17. На выходе элемента 4И-ИЛИ 14 второго модуля присутствует единичный логический потен0 циал, так как на первом, втором и третьем входах его второй структуры И присутствуют единичные логические потенциалы соответственно с прямого выхода первого триггера 1, с инверсного выхода второго

5 триггера 2 и с выхода элемента НЕ 23. На выходах элементов 4И-ИЛИ 14 первого модуля, 4И-ИЛИ 13 и5И-ИЛИ 15 второго модуля присутствуют нулевые логические потенциалы. Двенадцатый тактовый им0 пульс устанавливает на выходе общей схемы код 101010,

В тринадцатом и четырнадцатом тактах работы первого модуля аналогична его функционированию в пятом и шестом тактах.

5По приходу пятнадцатого тактового импульса на выходе общей схемы устанавливается код 010110 так как на выходах элементов 4И-ИЛИ 14 первого модуля, элементов 4И-ИЛИ 13 и 14 второго модуля присутствуют единичные потенциалы

Таким образом, режим функционирования модуля счетчика в максимальных Р ет 1 кодах Фибоначчи определяется состоянием разрядных триггеров последующего модуля.

Формула изобретения Счетчик импульсов в кодах Фибоначчи, содержащий первый, второй и третий элементы памяти, вход сброса, тактовый вход, первый и второй управляющие входы, первый и второй управляющие выходы, первый и второй элементы И, выход переноса, причем вход сброса счетчика соединен с входами сброса всех элементов памяти, тактовые входы которых и первый вход первого элемента И соединены с тактовой шиной счетчика, прямые выходы первого, второго и третьего элементов памяти соединены соответственно с первым, вторым и третьим входами второго элемента И. выход которого соединен с вторым входом первого элемента И, первый управляющий выход соединен с прямым выходом первого элемента памяти, а второй - с инверсным выходом второго элемента памяти, а аторой - с инверсным выходом второго элемента памяти, отличающийся тем, что, с целью расширения функциональных возможностей в области применения путем дополнительного обеспечения пересчета в минимальных Р 1 кодах Фибоначчи, каждый элемент памяти выполнен в виде D-триггера и дополнительно содержит первый и второй элементы 4И-ИЛИ, соединенные выходами с D-входами соответственно первого и второго триггеров, элемент 5И-ИЛИ, соединенного выходом с D-входом третьего триггера, третий, четвертый и пятый элементы И, элемент ИЛИ, соединенный выходом с выходом переноса счетчика, первый, второй, третий и четвертый элементы НЕ, шину выбора режима, причем прямой выход первого триггера соединен с первыми входами первой и второй структуры И второго элемента 4И-ИЛИ с первыми входами третьей и пятой структуры И элемента 5И-ИЛИ и со вторым входом третьего элемента И, соединенного выходом с первым входом элемента ИЛИ, а его инверсный выход - с первыми входами первой и второй структуры И первого элемента 4И-ИЛИ, со вторыми входами третьей структуры И второго элемента 4И-ИЛИ и второй структуры И элемента 5И-ИЛИ, прямой выход второго триггера соединен с первыми входами третьей структуры И первого элемента 4И-ИЛИ, третьей и четвертой структуры И второго элемента 4И-ИЛИ, первой

структуры И элемента 5И-ИЛИ и со вторыми входами третьей структуры И элемента 5И- ИЛИ и четвертого элемента И, а его инверсный выход - со вторыми входами первой

структуры И первого элемента 4И-ИЛИ и второй структуры И второго элемента 4И- ИЛИ, прямой выход третьего триггера соединен со вторыми входами четвертой структуры И второго элемента 4И-ИЛИ и

0 пятой структуры И элемента 5И-ИЛИ, с первыми входами второй и четвертой структуры И элемента 5И-ИЛИ, и с третьим входом третьего элемента И, а его инверсный выход - со вторыми входами третьей структуры И

5 первого элемента 4И-ИЛИ и первой структуры И второго элемента 4И-ИЛИ, второй и третий входы элемента ИЛИ соединены с выходами соответственно четвертого и первого элементов И, а выход второго элемента

0 И - с третьим входам пятого элемента И, первый и второй входы которого соединены соответственно с первым и вторым управляющими входами счетчика, вход первого элемента НЕ соединен с выходом пятого

5 элемента И, с первым входом четвертой структуры И первого элемента 4И-ИЛИ и с третьим входом четвертой структуры И элемента 5И-ИЛИ, а его выход - с третьим входом четвертой структуры И второго

0 элемента 4И-ИЛИ, вход второго элемента НЕ соединен с выходом второго элемента И, э его выход - с вторым входом четвертой структуры И элемента 5И-ИЛИ. вход третьего элемента НЕ соединен с третьим входом

5 четвертого элемента И и с первым управляющим входом счетчика, з его выход - с вторым входом первой структуры И элемента 5И-ИЛИ и с четвертым входом третьего элемента И, третьи входы первых структур И

0 первого и второго элементов 4И-ИЛИ, первый и второй структуры И элемента 5И- ИЛИ, пятый вход третьего элемента И и четвертый вход четвертого элемента И, вход четвертого элемента НЕ соединены с шиной

5 выбора режима, а вторые входы второй и четвертой структур И первого элемента 4И- ИЛИ, третьи входы третьей структуры И первого элемента 4И-ИЛИ, второй и третьей структуры И второго элемента 4И-ИЛИ,

0 третьей и четвертой структуры И элемента 5И-ИЛИ, четвертые входы четвертой структуры И второго элемента 4И-ИЛИ, пятой структуры И элемента 5И-ИЛИ и второго элемента И соединены с выходом четверто5 го элемента НЕ, а первые входы третьего и четвертого элементов И - с тактовой шиной счетчика.

| Пересчетная схема в коде Фибоначчи | 1985 |

|

SU1322467A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Счетчик импульсов в максимальных кодах Фибоначчи | 1988 |

|

SU1531215A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-09-15—Публикация

1990-12-17—Подача