XI

схэ

о

00 00

/Изобретение относится к импульсной технике и может быть использовано для пересчета импульсов в минимальном коде Фибоначчи.

Известна переснетная схема в коде Фибоначчи, содержащая в каждом разряде счетный триггер, элементы И и элемент ИЛИ 1.

Недостатком этого устройства является невозможность модульной организации пересчета.

Наиболее близким техническим решением к предлагаемому является модуль пересчетной схемы в коде Фибоначчи, содержащая вход сброса, счетный вход первый, второй и третий триггеры, входы сброса которых соединены с входом сброса пересчетной схемы, первый и второй элементы И, первые входы которых и синхровходы всех триггеров соединены со счетным входом пересчетной схемы, элемент ИЛИ, первый и второй входы которого соединены с вь ходами соответственно первого и второго элементов И, выход переноса, соединенный с выходом элемента ИЛИ. управляющий вход, управляющий выход, элемент НЕ, соединенный выходом со вторым входом второго элемента И, а входом - с управляющим входом пересчетной схемы, прямой и инверсный выходы первого триггера соединены соответственно с первыми J- и К-входами второго триггера, инверсный выход которого соединен с J- и К-входами первого триггера, прямой и инверсный выходы второго триггера соединены соответственно с первыми J- и К-входами третьего триггера, инверсный выход которого соединен со вторыми J- и К-входами второго триггера, прямой выход первого триггера соединен с вторым входом первого элемента И и с вторым К-входом третьего триггера, а его инверсный выход - с управляющим выходом пересчетной схемы, прямой выход второго триггера соединен с третьим входом второго элеглента И, а прямой выход третьего триггера - с третьЕ-.м входом первого элемента И 2,

Недостатком этого устройства является узкая область применения, обусловленная невозможностью пересчета с разрядностью, кратному пяти,

Цель изобретения - расширение области применения за счет обеспечения пересчета с разрядностью, кратному пяти.

Поставленная цель достигается тем, что пересчетная схема в коде Фибоначчи, содержащая вход сброса, счетный вход, первый, второй и третий триггеры, входы сброса которых соединены с входом сброса пересчетной схемы, первый и второй элементы И, первые входы которых и синхровходы всех триггеров соединены со счетным входом пересчетной схемы, элемент ИЛ И, первый и второй входы которого соединены с выходами соответственно первого м втсро0 го элементов И, выход переноса, соединенн ы и с выходом элемента И Л И, управляющий вход, управляюидий выход, элемент НЕ, соединенный выходом со вторым входом второго элемента И, а входом 5 с управляющим входом пересчетиой схемы, прямой и инверсный выходы первого триггера соединены соответственно с первыми J-M К-входами второго триггера, инверсный выход которого соединен с J- и К-входами

0 первого триггера, прямой и инверсный выходы второго триггера соединены соответственно с первыми J- и К-входами третьего триггера, инверсный выход которого соединен со вторыми J- и К-входами второго триггера, прямой выход первого триггера соединен с вторым входом первого элемента И и с вторым К-входом третьего триггера, а его инверсный выход - с управляющим выходом пересчетной схемы, прямой вь5ход

0 второго триггера соединен с третьим входом второго элемента И, о прямой выход третьего триггера -с третьим входом первого элемента И, дополнительно содержит четвертый и пятый JK-триггеры, причем первые J- и К-входы четвертого триггера соедин е и ы соответственно с прямым и инверсным выходами третьего триггера, а его прямой и инверсный выходы соответственно с первыми J- и К-входами пятого триггера, инверсный выход которого соединен со вторыми J-и К-входами четвертого триггера, прямой выход четвертого триггера соединен с четвертым входом второго элемента И, а его инверсный выход - с вторым J и третьим К-входом третьего триггера, прямой выход пятоготриггера соединен с четвертым входом первого эле,мента И, а его второй J-вxQд - с прямым выходом второго триггера и с третьим К-входом четвертого триггера,- второй К-вход пятого триггера соединен с прямым выходом первого триггера и с третьим J-входом четвертого триггера, а его третий К-вход - с прямым выходом третьего триггера, третий

5 J- и К-входы пятого триггера соединены с управляющим входом пересчетной схег-1ы, а входы сброса и синхровходы- четвертого и пятого триггеров соединены соответственно с входом сброса и счетным входом пересчетной схемы.

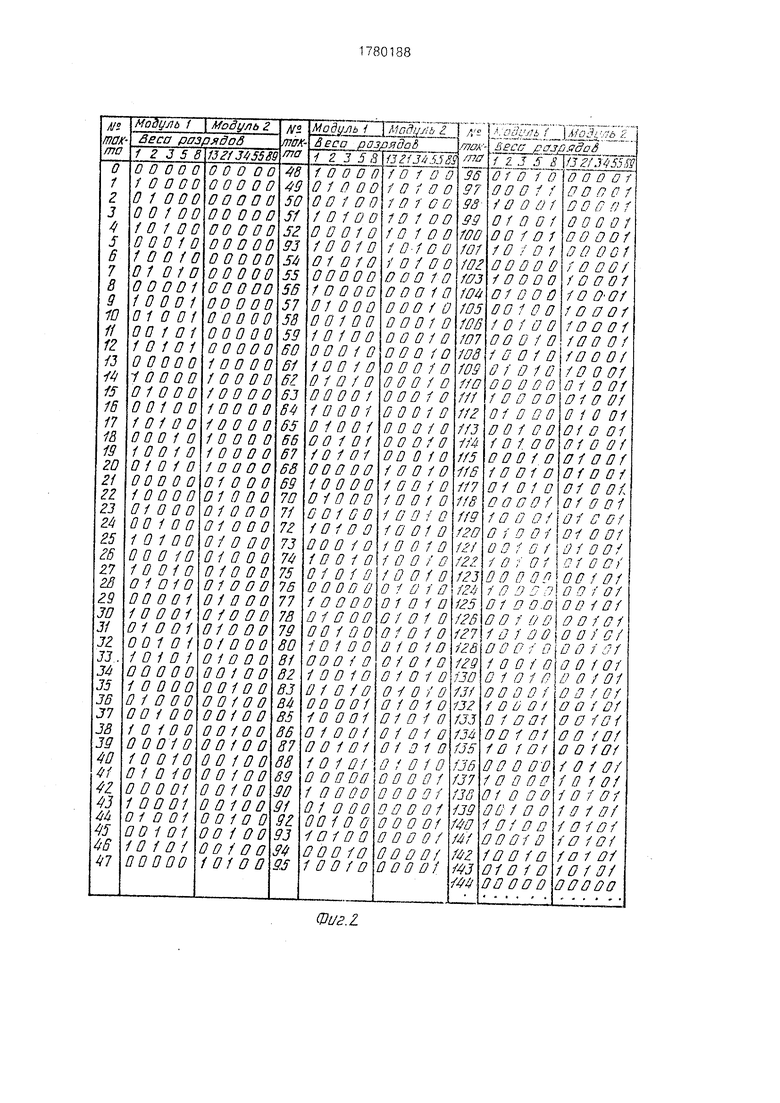

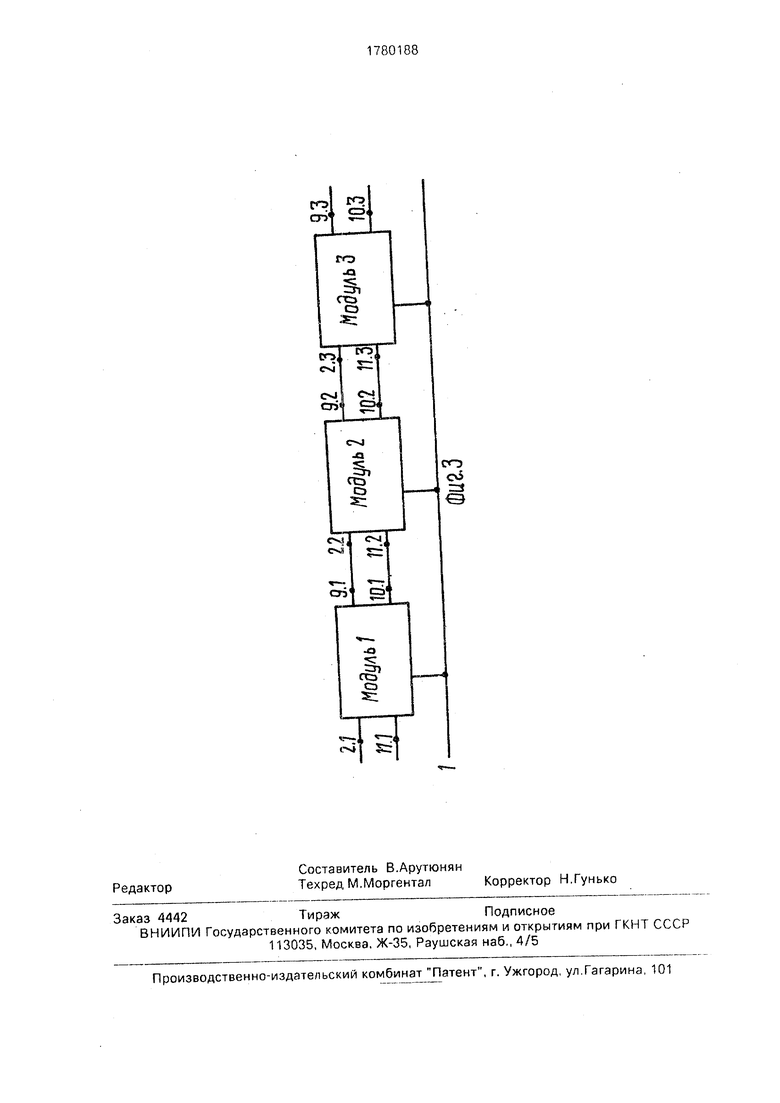

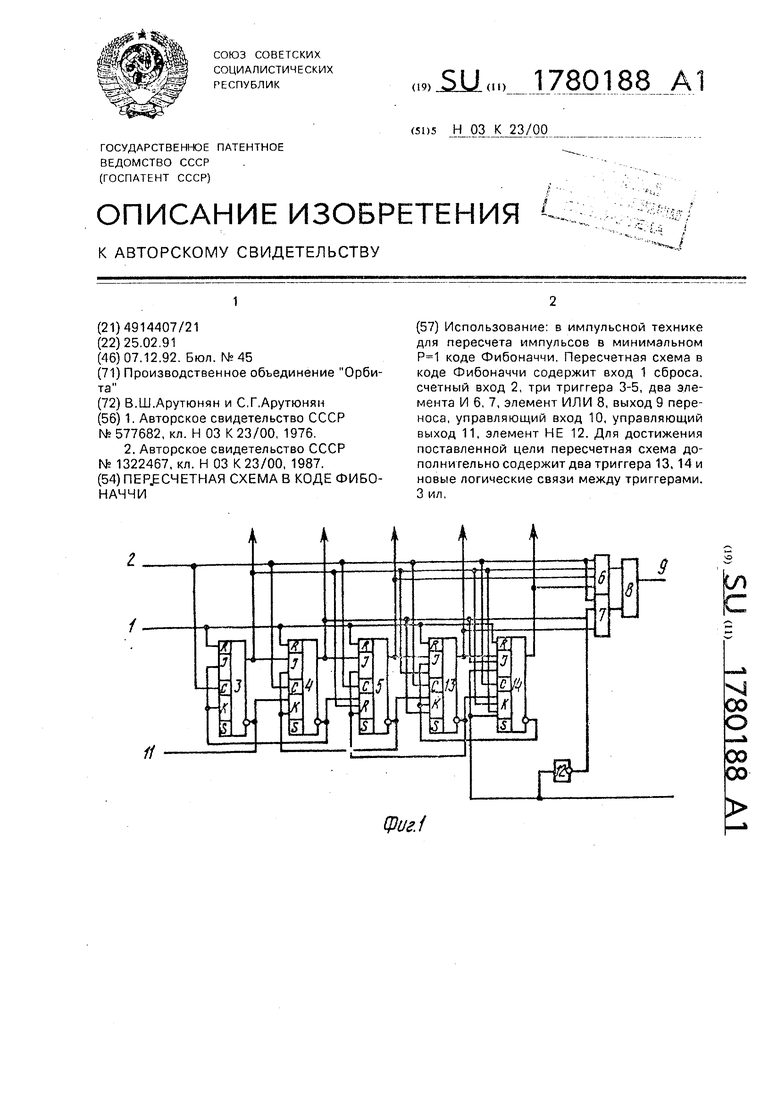

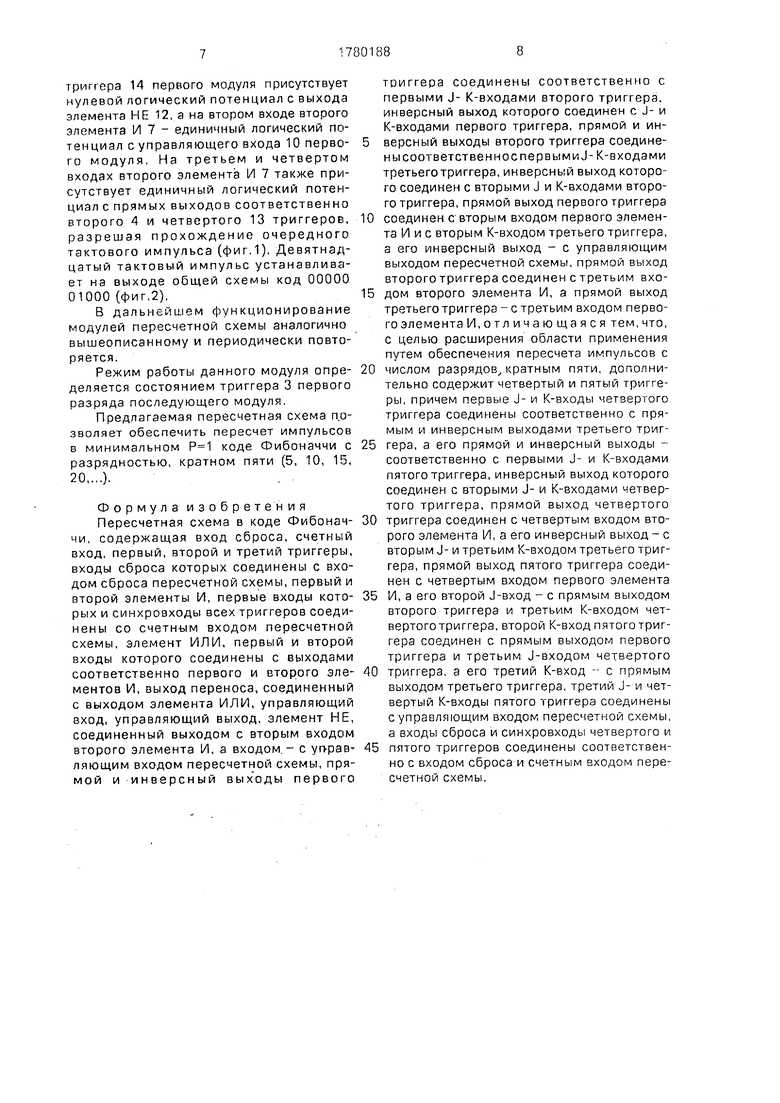

На фиг,1 представлена функциональная схема пересчетный схемы: на фиг.2 - таблица кодов, описывающих работу устройства; на фиг.З - схема подключения нескольких модулей для наращивания разрядности пересчета.

Пересчетная схема в коде Фибоначчи содержит вход 1 сброса, счетный вход 2, первый 3, второй 4, и третий 5 триггеры, первый 6 и второй 7 элементы И, элемент ИЛИ 8, выход переноса 9. управляющий вход 10, управляющий выход 11, элемент НЕ 12, четвертый 13 и пятый 14 триггеры (фиг.1).

Пересчетная схема в минимальных кодах Фибоначчи функционирует следующим образом.

Для наращивания разрядности общей схемы ряд модулей пересчетной схемы (фиг.1) объединяются следующим образом. Выход переноса 9 данного модуля подключается к счетному входу 2 последующего модуля, управляющий вход 10 данного модуля - к управляющему выходу 11 последующего модуля входы 1 сброса всех модулей объединяются, а на управляющий вход 10 старшего модуля прикладывается единичный логический потенциал.

В исходном состоянии триггеры модулей находятся в нулевых состояниях (фиг.1 и 2). Первый триггер 3 первого модуля находится в режиме переключения, так как на его J- и К-входах присутствует единичный логический потенциал с инверсного выхода второго триггера 4, который находится в режиме записи нуля, так как на его первом J-входе присутствует потенциал логического нуля, а на первом и втором К-входах - единичные логические потенциалы соответственно с инверсных выходов третьего 5 и первого 3 триггеров. Четвертый 13 и пятый 14 триггеры находятся в режиме хранения, так как на их первых J- и К-входах присутствуют нулевые логические потенциалы. По приходу первого тактового импульса на выходе пересчетной схемы, содержащей, например, два модуля, устанавливается код 10000 00000 (фиг.2), что соответствует десятичному числу 1.

Перед поступлением второго тактового импульса первый триггер 3 первого модуля находится в режиме переключения, второй триггер 4 - в режиме записи единицы, так как на его J-входах присутствуют потенциалы логической единицы соответственно с

прямого выхо,да первого тр1:ггера 3 и с инверсного выхода третьего тригге)а 5, а на втором его К-входе - нулевой логический потенциал с инверсного выхода первого

триггера 3. Третий триггер 5 находится в режиме записи нуля, а четвертый 13 и пятый 14 триггеры - в режиме хранения. Второй, тактовый импульс устанавливает на выходе общей схемы код 01 00000000 (фиг.2), что

0 соответствует десятичному числу 2.

Последующие тактовые импульсы приводят к формированию в первом модуле пересчетной схемы определенных кодо§, соответствующих десятичным

5 числам ряда натуральных чисел (3,4,5,.,,). Однако каждому из этих десятичных чисел соответствуют определенные кодовые комбинации, так как разряды пятиразрядного первого модуля имеют веса, соответствующие первым пяти числам минимальных кодов Фибоначчи (1, 2, 3, 5, 8). По поступлении десятого тактового импульса на выходе общей схемы устанавливает5 ся код 10101 00000 (фиг,2),

Разряды пятиразрядного второго модуля пересчетной схемы имеют веса, соответствующие следующим пяти числам Фибоначчи (13, 21, 34, 55, 89). Перед поступлением одиннадцатого тактового импульса на втором, третьем и четвертом входах первого элемента И 6 присутствуют единичные логические потенциалы с прямых выходогз соответственно первого 3, третьего 5 и пятого. 14 триггеров. Первый триггер 3 первого модуля находится в режиме переключения, второй триггер 4 - в режиме хранения, третий триггер 5 - в режиме

0 записи нуля, четвертый триггер 13 - в режиме хранения, а пятый триггер 14 в режиме записи нуля. Одиннадцатый тактовый импульс проходит через элементы И 6, ИЛИ 8 и выход 9 переноса

5 первого модуля поступает на счетный вход 2 второго модуля (фиг.1). На выходе общей схемы устанавливается код 00000 10000 (фиг,2).

На управляющем выходе 11 второго

0 модуля устанавливается нулевой логический потенциал, который поступает на управляющий вход 10 первого модуля.

В дальнейшем, до поступления девятнадцатого тактового импульса, первый модуль функционирует аналогично с первого по восьмому тактам.

Перед поступлением девятнадцатого тактового импульса на третьем J-входе и на четвертом К-входе пятого

триггера 14 первого модуля присутствует нулевой логический потенциал с выхода элемента НЕ 12, а на втором входе второго элемента И 7 - единичный логический потенциал с управляющего входа 10 первого модуля, На третьем и четвертом входах второго элемента И 7 также присутствует единичный логический потенциале прямых выходов соответственно второго 4 и четвертого 13 триггеров, разрешая прохождение очередного тактового импульса (фиг,1). Девятнадцатый тактовый импульс устанавливает на выходе общей схемы код 00000 01000 (фиг,2),

В дальнейшем функционирование модулей пересчетной схемы аналогично вышеописанному и периодически повторяется.

Режим работы данного модуля определяется состоянием триггера 3 первого разряда последующего модуля.

Предлагаемая пересчетная схема п.озволяет обеспечить пересчет импульсов в минимальном коде Фибоначчи с разрядностью, кратном пяти (5, 10, 15, 20,.,.).

Формула изобретения Пересчетная схема в коде Фибоначчи, содержащая вход сброса, счетный вход, первый, второй и третий триггеры, входы сброса которых соединены с входом сброса пересчетной схемы, первый и второй элементы И, первые входы которых и синхрозходы всех триггеров соединены со счетнъ1м входом пересчетной схемы, элемент ИЛИ, первый и второй входы которого соединены с выходами соответственно первого и второго элементов И, выход переноса, соединенный с выходом элемента ИЛИ, управляющий вход, управляющий выход, элемент НЕ, соединенный выходом с вторым входом второго элемента И, а входом.- с уп.рав ляющим входом пересчетной схемы, прямой и инверсный выходы первого

триггера соединены соответственно с первыми J- К-входами второго триггера, инверсный выход которого соединен с ,J- и К-входами первого триггера, прямой и инверсный выходы второго триггера соединены соответствен но с первым и J-К-входами третьеготриггера, инверсный выход которого соединен с вторыми ,J и К-входами второго триггера, прямой выход первого триггера

соединен с вторым входом первого элемента И и с вторым К-входом третьего триггера, а его инверсный выход - с управляющим выходом пересчетной схемы, прямой выход второго триггера соединен с третьим входом второго элемента И, а прямой выход третьего триггера-с третьим входом первого эле мента И,отличающаяся тем, что, с целью расширения области применения путем обеспечения пересчета импульсов с

числом разрядов кратным пяти, дополнительно содержит четвертый и пятый триггеры, причем первые J- и К-входы четвертого триггера соединены соответственно с прямым и инверсным выходами третьего триггера, а его прямой и инверсный выходы соответственно с первыми J- и К-входами пятого триггера, инверсный выход которого соединен с вторыми J- и К-входами четвертого триггера, прямой выход четвертого

триггера соединен с четвертым входом второго элемента И, а его инверсный выход - с вторым J- и третьим К-входом третьего триггера, прямой выход пятого триггера соединен с четвертым входом первого элемента

И, а его второй J-вход - с прямым выходом второго триггера и третьим К-входом четвертоготриггера, второй К-вход пятого триггера соединен с прямым выходом первого триггера и третьим J-входом четвертого

триггера, а его третий К-вход - с прямым выходом третьего триггера, третий J- и четвертый К-входы пятого триггера соединены с управляющим входом пересчетной схемы, а входы сброса и синхровходы четвертого и

пятого триггеров соединены соответственно с входом сброса и счетным входом пересчетной схемы.

Фиг. 2.

(j

| название | год | авторы | номер документа |

|---|---|---|---|

| Модуль пересчетной схемы в минимальном Р-коде Фибоначчи | 1988 |

|

SU1511862A1 |

| Пересчетная схема в коде Фибоначчи | 1991 |

|

SU1800612A1 |

| Пересчетная схема в коде Фибоначчи | 1990 |

|

SU1757098A1 |

| Счетчик импульсов в максимальных кодах Фибоначчи | 1988 |

|

SU1531215A1 |

| Счетчик импульсов в кодах Фибоначчи | 1990 |

|

SU1762408A1 |

| Пересчетное устройство в коде Фибоначчи | 1990 |

|

SU1725389A1 |

| Счетчик импульсов в максимальных кодах Фибоначчи | 1990 |

|

SU1720157A1 |

| Пересчетное устройство в коде Фибоначчи | 1989 |

|

SU1651375A1 |

| Пересчетная схема в коде Фибоначчи | 1985 |

|

SU1322467A1 |

| Счетчик импульсов в максимальных Р-кодах Фибоначчи | 1988 |

|

SU1511861A1 |

Использование: в импульсной технике для пересчета импульсов в минимальном Р=1 коде Фибоначчи. Пересчетная схема в коде Фибоначчи содержит вход 1 сброса, счетный вход 2, три триггера 3-5, два элемента И 6, 7, элемент ИЛИ 8, выход 9 переноса, управляющий вход 10, управляющий выход 11, элемент НЕ 12. Для достижения поставленной цели пересчетная схема дополнительно содержит два триггера 13,14 и новые логические связи между триггерами. 3 ил.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Двоичный счетчик с последовательным переносом | 1976 |

|

SU577682A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Пересчетная схема в коде Фибоначчи | 1985 |

|

SU1322467A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-12-07—Публикация

1991-02-25—Подача