8

10

И

СЛ

00

СЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1982 |

|

SU1065857A1 |

| Устройство для локализации неисправностей | 1980 |

|

SU903888A1 |

| Сигнатурный анализатор | 1980 |

|

SU903898A1 |

| Сигнатурный анализатор | 1984 |

|

SU1223231A1 |

| Устройство для контроля цифровых узлов | 1982 |

|

SU1059576A1 |

| Устройство для контроля цифровых объектов | 1986 |

|

SU1319037A2 |

| Сигнатурный анализатор | 1983 |

|

SU1223230A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Устройство для контроля цифровыхОб'ЕКТОВ | 1979 |

|

SU851410A1 |

| Устройство для диагностирования аппаратуры обработки данных | 1985 |

|

SU1390610A1 |

Изобретение относится к вычислительной технике и может использоваться для контроля и диагностирования дискретных объектов. Цель изобретения - расширение функциональных возможностей сигнатурного анализа. Анализатор содержит формирователь сигнатур, представляющий собой регистр сдвига 2 с сумматором 1 по модулю два в цепи обратной связи, блок 3 индикации, первый триггер 4, два элемента И 5 и 6, два элемента 7 и 8 задержки, блок 9 сравнения, второй триггер 10, индикатор 11. Анализатор позволяет получать сигнатуры, характеризующие состояние объекта контроля от момента старта до первого сбоя. 1 ил.

Т 2

гу/

инфорп.

CUHXft,

старпп с/поп

12

i1513A50

Изобретение относится к вычисли- тельной технике и может быть использовано для кодирования технического состояния цифровых систем, их конт- г роля и поиска в них неисправных эле - ментов.

Цель изобретения - расширение функциональных возможностей за счет получения укороченной сигнатуры, ю характеризующей состояние объекта от момента Старт до первого сбоя.

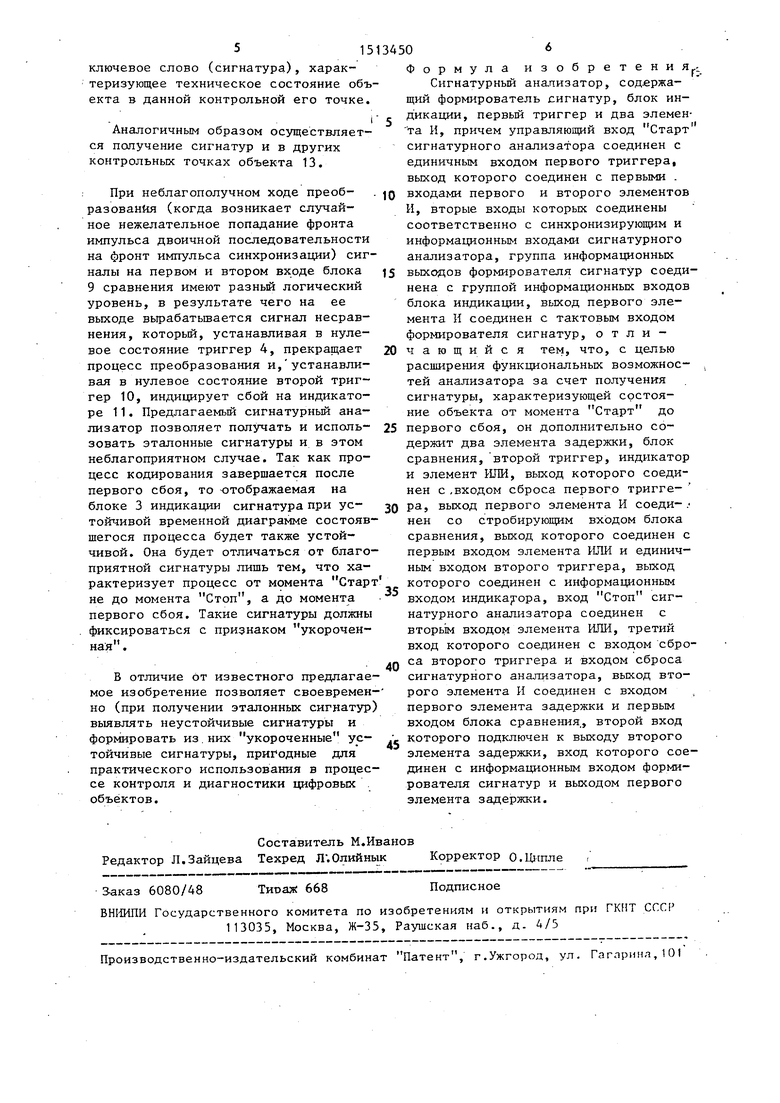

На чертеже представлена схема сигнатурного анализ-атора.

Сигнатурньй анализатор содержит 15 Формирователь сигнатур, состоящий из сумматора 1 по модулю два, регистра 2 сдвига, блок 3- индикации, первый триггер 4, элементы И 5 и 6, элементы задержки 7 и 8, блок 9 срав- 20 нения, второй триггер 10, индикатор 11 и элемент ИЛИ 12, входы Информация, Синхронизация, Старт Стоп, Сброс.

Цифровой объект 13 не входит в 25 состав анализатора и приводится лишь для пояснения его работы.

Блок 3 индикации предназначен для отображения двоичного кода, получаемого на регистре 2 сдвига. В соот- 30 ветствии с назначением блок 3 индикации содержит дешифратор, на вход которого поступает двоичньй код, и семисегментные индикаторы, связанные по входу с выходом дешифратора. Сигнатурньй анализатор работает следующим образом.

Предполагается, что цифровой объект 13 солеожит внутри себя встроен- ньй стимулятор, обеспечивающий де- 40 терминированное возбуждение объекта 13 в режиме его контроля, по команде Пуск объект 13 имеет также установку в нуль.

Перед началом работы входы Ин- д формация, Синхронизация, Старт Стоп и Сброс подключаются к соответствующим выходам объекта 13.

По сигналу Сброс.(установка в начальное состояние объекта 13) в исходное состояние также устанавливается и устройство. При этом в состояние логического нуля устанавливаются первьй триггер 4 (через элемент ШШ 12) и триггер 10. Нулевой логический уровень выхода первого триггера 4 закрьшает элементы И 5 и 6, а второго триггера 10 - индикатор 11, который не светится. Затем

50

55

5 0

5

0 0

0

5

по команде Пуск осуществляется запуск стимуляции объекта 13 и выработка сигнала Старт, которьй жестко связан с процессом запуска стимуляции. По сигналу Старт первьй триггер 4 устанавливается в состояние логической единицы и открывает элементы И 5 и 6.

В результате стимуляции цифрового объекта 13 контрольными воздействиями в его контрольных точках вырабатываются реакции на эти воздействия - двоичнью последовательности, которые собственно и являются информацией, отражающей техническое состояние (исправное или неисправное) цифрового объекта 13.

С помощью автоматического или ручного щупа вход Информация соединяется с контрольной точкой объекта 13. При этом двоичная последовательность через открытьй элемент И 6 поступает на вход первого элемента 7 задержки и на первьй вход блока 9 сравнения и далее с выхода первого элемента 7 задержки на информацион- ньй вход сумматора 1 и вход второго элемента 8 задержки, с выхода которого - на второй вход блока 9 сравнения. С помощью синхроимпульсов, поступающих на вход синхронизации регистра 2 сдвига, через вход Синхронизация и через открытьй элемент И 5 осуществляется преобразование длинных, двоичных последовательностей в компактные ключевые слова. Это осуществляется путем сдвигов на каждом такте синхронизации суммы по модулю два соответствующих битов двоичной последовательности и значения бита цепи обратной связи, поступающего с выхода регистра 2 сдвига на вход обратной связи сумматора 1. При благополучном ходе преобразования (когда не возникает случайного нежелательного попадания фронта импульса двоичной последовательности на фронт импульса синхронизации и, следовательно, на первом и-втором входах блока 9 сравнения присутствуют в момент тактирования сигналы одного и того же логического уровня) процесс преобразования завершается по сигналу Стоп, KOTopbtti через элемент ШП1 12 устанавливает первьй триггер 4 в состояние логического нуля. При этом закрываются элементы И 5 и 6, а в блоке 3 индикации высвечивается

51513450

ключевое слово (сигнатура), характеризующее техническое состояние объекта в данной контрольной его точке.

Ф

щи

Аналогичным образом осуществляется получение сигнатур и в других контрольных точках объекта 13.

: При неблагополучном ходе преобразования (когда возникает случайное нежелательное попадание фронта импульса двоичной последовательности на фронт импульса синхронизации) сигналы на первом и втором входе блока 9 сравнения имеют разньй логический уровень, в результате чего на ее выходе вырабатьшается сигнал несравнения, который, устанавливая в нулевое состояние триггер 4, прекращает процесс преобразования и, устанавливая в нулевое состояние второй триггер 10, индицирует сбой на индикаторе 11. Предлагаемый сигнатурньй анализатор позволяет получать и использовать эталонные сигнатуры и в этом неблагоприятном случае. Так как процесс кодирования завершается после первого сбоя, то отображаемая на блоке 3 индикации сигнатура при устойчивой временной диаграмме состоявшегося процесса будет также устойчивой. Она будет отличаться от благоприятной сигнатуры лишь тем, что характеризует процесс от момента Старт не до момента Стоп, а до момента первого сбоя. Такие сигнатуры должны фиксироваться с признаком укороченная .

В отличие от известного предлагаемое изобретение позволяет своевременно (при получении эталонных сигнатур) выявлять неустойчивые сигнатуры и формировать из.них укороченные устойчивые сигнатуры, пригодные для практического использования в процессе контроля и диагностики цифровых . объектов.

Составитель М.Иванов Редактор Л.Зайцева Техред Л .Олийнык Корректор О.Ципле

3-аказ 6080/48

Тиоаж 668

BHIiИЛИ Государственного комитета по изобретениям и открытиям при ГКИТ СССР 113035, Москва, Ж-35, Раушская наб., д. А/5

Формула изобретения.:

Сигнатурньй анапизатор, содержащий формирователь сигнатур, блок инд икации, первьш триггер и два элемен- та И, причем управляющий вход Старт сигнатурного анализатора соединен с единичным входом первого триггера, выход которого соединен с первыми .

входами первого и второго элементов И, вторые входы которых соединены соответственно с синхронизирующим и информационным входами сигнатурного анализатора, группа информационных

выходов формирователя сигнатур соединена с группой информационных входов блока индикации, выход первого элемента И соединен с тактовым входом формирователя сигнатур, о т л и -

чающийся тем, что, с целью расширения функциональных возможностей анализатора за счет получения сигнатуры, характеризующей состояние объекта от момента Старт до

первого сбоя, он дополнительно содержит два элемента задержки, блок сравнения, второй триггер, индикатор и элемент ЬШИ, выход которого соединен с .входом сброса первого тригге-

Р выход первого элемента И соеди-. нен со стробирующим входом блока сравнения, выход которого соединен с первым входом элемента РШИ и единичным входом второго триггера, выход которого соединен с информационным входом индика;гора, вход Стоп сигнатурного анализатора соединен с BTOpbiM входом элемента ИЛИ, третий вход которого соединен с входом сброса второго триггера и входом сброса сигнатурного анализатора, выход второго элемента И соединен с входом первого элемента задержки и первым входом блока сравнения., второй вход которого подключен к выходу второго

элемента задержки, вход которого соединен с информационньм входом формирователя сигнатур и выходом первого элемента задержки.

Подписное

| Электроника, 1977, № 5, с | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Устройство для контроля цифровыхОб'ЕКТОВ | 1979 |

|

SU851410A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-10-07—Публикация

1987-08-17—Подача