I

Изобретение относится к вычислительной технике и может быть использовано для контроля и локализации неиспра:вностей в цифровых схемах.

Известно устройство для обнаружения и локализации неисправностей в микропроцессорных системах при помощи шестнадцатиричных ключевых кодов (сигнатур), содержащее генератор стимулирующих воздействий (тестов), выходы которого соединены с входами проверяемой схемы, логический анализатор реакций, содержащий регистр сдвига с обратными связями, формируюощй сигнатуры, блок управления, индикатор. Ногический сигнатурный анализатор снабжен входыми клеммами Старт, Стоп, Синхронизация, Данные. Устройство позволяет определять значения ключевых кодов реакций схемы в любой выбранной точке с целью сравнеВИЯ их с эталонными значениями СП,Однако устройство не позволяет локализовать неисправности в цифровых схемах, содержащих цепи обратной связи без разрыва этих цепей при помощи аппаратных переключателей или разъемов.

Известно также устройство, содержащее сигнатурный генератор, дисплей, элемент И, триггер управлеtoния, причем информационный вход устройства соединен с информационным входом сигнатурного генератора, выход которого соединен с входом дисплея, синхровход сигнатурного

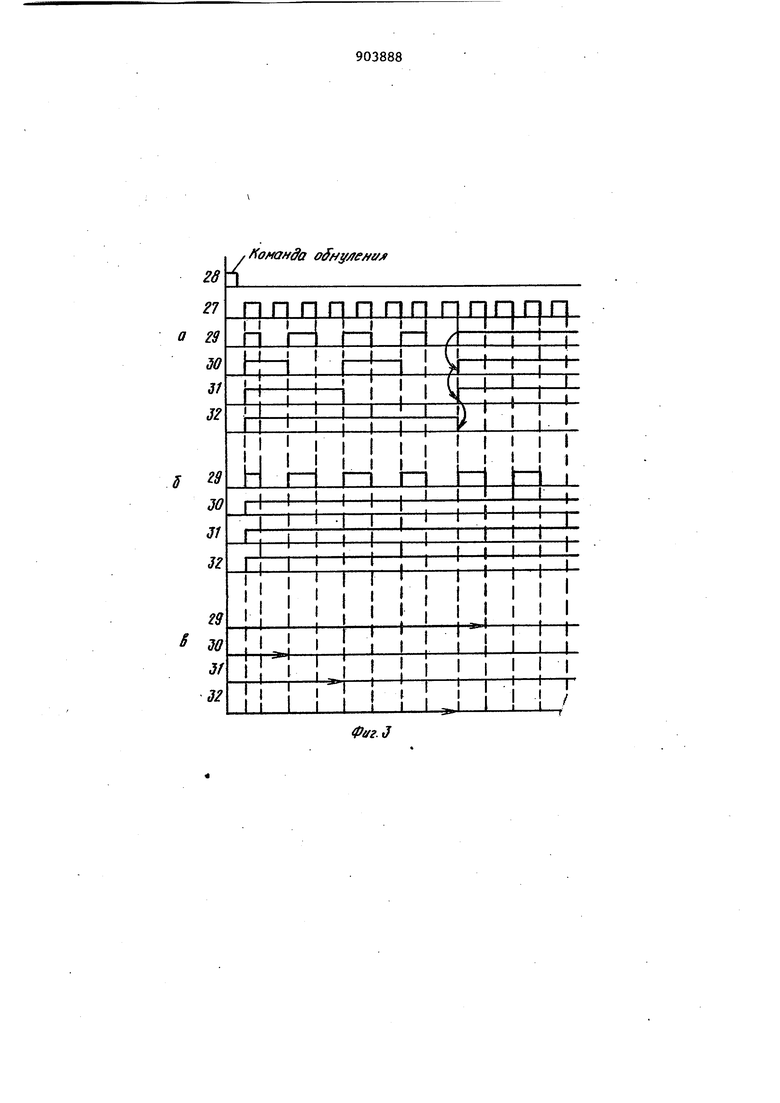

ts генератора соединен с выходом элемента И, первый вход которого является синхровходом устройства, второй вход элемента И соединен с выходом триггера управления, пер30вый установочный вход которого является первым управляющим входом устройства, второй управляющий вход которого соединен с вторым установочным входом триггера управления 2 . Недостатком этого устройства яв- ляется отсутствие блока задания чис ла синхроимпульсов, подаваемых на его синхровход, следовательно, труд ность локализации неисправностей в логических узлах, содержащих цепи с обратными связями. Цель изобретения - повьшение достоверности контроля, т.е. обеспечение возможности локализации неисправностей до уровня элементов в цифровых схемах, как без обратных связей, так и с обратными связями без разрыва этих связей при помощи переключателей, разъемов или путем закрывания соответствующих вентилей по программе без значительных аппаратурных затрат., Поставленная цель достигается тем, что в устройство для локализации неисправностей, содержащее генератор синхроимпульсов, генератор тестов, коммутатор, триггер управления, элемент И, логический анализатор реакций, причем логический а1гализатор реакций содержит два эле мента задержки, одновибратор, элемент НЕ, переключатель, регистр сдвига, регистр памяти, дешифратор, узел индикации, входы которого соединены соответственно с выходами де шифратора, входы которого соединены соответственно с выходами регистра памяти, информационные входы,входы которого соединены с выходами регистра сдвига, установочный вход кото рого соединен с входом одновибратора и является установочным входом логического анализатора реакций, ин формационный вход которого соединен с информационным входом регистра сдвига, синхровход которого соедине с выходом переключателя, первый вхо которого соединен с выходом элемен :,та НЕ, вход которого соединен с вто рым входом переключателя и является синхровходом логического анализатор реакций, управляющий вход которого соединен с входом первого элемента задержки, выход которого соединен с синхровходом регистра памяти и с входом второго элемента задержки, выход которого соединен с входом одновибратора, информационный вход логического анализатора реакций сое динен с выходом коммутатора, вход которого соединен с контактом проверяемого узла, группа входов которого соединена соответственно с группой выходов генератора тестов, установочный вход которого соединен с установочным выходом логического анализатора реакций, с первым установочным входом триггера управления, прямой выход которого соединен с управляющим входом логического анализатора реакций, синуровход которого соединен с выходом элемента И, первый вход которого соединен с инверсным выходом триггера, синхровход генератора тестов соединен с синхровходом проверяемого узла, с выходом генератора синхроимпульсов, введен блок управления глубиной анализа, синхровход которого соединен с выходом генератора синхроимпульсов, выход блока управления глубиной анализа соединен с вторым установочным входом триггера управления. Кроме того, блок управления глубиной анализа содержит пеоеключатель глубины анализа, узел памяти, узел сравнения кодов, счетчик, синхровход которого является входом блока, выход которого соединен с выходом узла сравнения кодов, с управляющим входом счетчика, группа выходов которого соединена соответственно с первой группой входов узла сравнения кодов, вторая группа входов которого соединена соответственно с группой выходов узла памяти, вход которого соединен с выходом переключателя глубины анализа. Введение в устройство указанного блока позволяет устанавливать нужную глубину анализа для фиксации момента (такта цикла проверки) возникновения ошибки или сбоя в работе цифровой схемы и предотвращения прохождения этой ошибки по цепям обратной связи. На фиг, I изображена функциональная схема устройстваi на фиг, 2 часть проверяемой схемы для пояснения работы устройства; на фиг, Заэпюры напряжений в соответствующих точках схемы, изображенной на фиг,2 при исправной ее работе} на фиг, 36эпюры напряжений в соответствующих точках схемы при неисправной работе триггера Т2 на фиг, Зв - глубина анализа, при которой эпюры напряжений и соответственно сигнатурь в выбранных точках неисправностей

схемы совпадают с эпюрами напряжений и сигнатурами в соответствующих точках исправной схемы; на фиг. 4 пример реализации регистра с обратными связями логического анализатора.

Устройство для локализации неисправностей (фиг. О содержит генератор тестов, проверяемую схему 2, коммутатор 3, логиче.ский анализатор 4 реакций, включающий в себя регистр 5 сдвига с обратными связями, регистр 6 памяти, дешифратор 7 сигнатуры, узел 8 индикации, узел 9 выбора активного фронта импульсов синхронизации, содержавший элемент НЕ IО и переключатель 11, кроме того, логический анализатор С9держит элемент 12 задержки, второй элемент 13задержки, одновибратор 14, информационный вход 15 логического анализатора 4 реакций, управляюидий вход 16 логического анализатора 4 реакций, синхровход 17 логического анализатора 4 реак-ций, выход 18 логического анализатора 4 реакций.

Кроме тогоJустройство (фиг. l) содержит генератор 19 синхроимпульсов, блок 20 управления глубиной анализа, триггер 21 управления, .элемент И 22, переключатель 23 установки глубины анализа, узел 24 памяти, узел 25 сравнения кодов, счетчик 26.

Устройств1О работает следующим образом о

Перед началом проверки оператор с помощью переключателя 23 установк глубины анализа вводит в узел 24 памяти двоичное число, соответствующее числу тактов в цикле проверки. Разрядность данного двоичного числа опЬ еделяется максимальным числом тактов в полном цикле проверки.

Переключателем 11 схемы 9 выбора активного фронта импульсов синхрнизации выбирают активный фронт импульсов синхронизации, по которому производится запись и обработка Двоичной информации, поступающей с выхода коммутатора 3 в регис гр 5 с обратными связями. С помощью коммутатора 3 оператор подключает одну из контролируемых точек проверяемой схемы 2 к информационному входу 15 логического анализатора 4.

В начале цикла проверки все элементы памяти устройства устанавли-.

ваются в исходное состояние. При этом триггер 21 управления находит. ся в таком состоянии, при котором

на инверсном выходе устанавливается уровень логической 1, а на прямом выходе уровень логического О, и через открытый элемент И импульсы синхронизации с выхода генератора 19 импульсов синхронизации поступают

O на синхровход 17 логического акализатора 4. Одновременно ийпульсы синхронизации с выхода генератора 19 поступают на синхровход генератора 1 тестов, синхровход проверяемой схе-

5 мы 2 и синхровход счетчика 26. С выходов генератора 1 тестов на информационные входы проверяемой схемы 2 поступают периодические стимулирующие воздействия, необходимые для

0 форсированного переключения логических состояний проверяемой схемы 2. Двоичная информационная последовательность импульсов в выбранной контролируемой точке проверяемой схемы 2 (реакция контролируемой точки) через коммутатор 3 поступает на вход регистра 5 сдвига с обратными Связями и под действием импульсов синхронизации с вькода узла 9 выбора

активного фронта импульса синхронизации обрабатьша-ется по известному закону в данном регистре 5.

Процесс обработки реакции контролируемой схемы продолжается до тех пор, пока установленный в блоке 24 памяти двоичный код при помощи переключателя 23 устройства глубины анализа не совпадет с двоичным кодом на выходах счетчика 26. В этот момент на выходе схемы 25 сравнения кодов формируется импульс, который проходит на управляющий вход счетчика 26, устанавливая его в исходное положение. Одновременно импульс с выхода схемы 25 сравнения кодов проходит на второй установочный вход триггера управления и переводит его в состояние, при котором элемент И 22 закрьшается, а на прямом выходе триггера 2I управления .формируется перепад напряжения, поступаюищй на вход первого элемента 12 задержки, с выхода которого перепад напряжения поступает на управляющий вход регистра 6 памяти. При этом остаток двоичной последовательности, находяцщйся в регистре 5 сдвига с обратными связями переписывается в регистр 6 памяти. С 7У выходов регистра 6 памяти остаток двоичной последовательности поступает на входы дешифратора 7, где преобразуется в ключевой код реакции контролируемой точки (сигнатуру точки). С выходов дешифратора 7 сиг натура контролируемой точки поступает на входы индикатора 8. Таким образом, результат анализа двоичной последовательности выводится на цифровой индикатор 8 в виде числа:, однозначно определяющего сигнатуру выбранной точки при данной глу бине анализа С выхода первого элемента 12 задержки перепад напряжения поступает также на вход второго элементу 13 задержки, а с выхода второго эле мента 13 задержки на вход одновибратора 14, служащего для формирования сигнала сброса в начале цикла проверки и после окончания очередного цикла проверки. При этом все элементы памяти устройства приводят ся в исходное состояние, за исключением регистра памяти, в котором записан остаток информационной двои ной последовательности. В этот момент логический анализатор 4 (сигнатурный) готов к приему новых данных, а на индикаторе 8 индицируется сигнатура предыдущей контролируемой точки проверяемой схемы 2. Правильные сигнатуры контролируемых точек определяются просто, например путем контроля точек схемы заведомо работоспособной (эталонной) Результаты такого контроля могут быть зафиксированы на бумаге. При несовпадении сигнатуры прове ряемой точки узла с эталонной оператор производит контроль точек, ра положенных ближе к входам, двигаясь по узлу с|1рава налево. При этом он должен обнаружить элемент узла, у -которого на входе сигнатуры соответствуют эталонным, а на выходе не Этот элемент является неисправным. В случае проверки узлов, содержа щих цепи обратной связи, устройство позволяет так .подобрать глубину анализа (момент окончания анализа) что ошибка, возникшая в узле, не ус йевает пройти по цепям обратной связи и исказить сигнатуры всех кон троЛируемьрс точек, связанных с-этими цепями. Рассмотрим пример. На фиг. 2 изображена часть цифровой схемы, содержащая цепь обратной, связи, которая состоит из триггеров Т1-Т4-27-30 и элемента И-НЕ 31. Предположим, что в приведенной схеме триггер 12 не управляется, а ert инверсный выход постоянно находится в состоянии логической 1. Сравнивая эпюры напряжений в соответствующих точках исправной и неисправной схемы, на фиг. 3 можно заметить, что различие в эпюрах допускается скорее всего на выходе неисправного триггера. Таким образом, если плавно увеличить глубину анализа, проверяя сигнатуры элементов, назначенных обратной связью, можно обнаружить элемент, на выходе которого раньше других сигнатура не будет соответствовать эталонной. Этот элемент и будет неисправным элементом, который является источником ошибки. Необходимо отметить, что между видом двоичной последовательности, поступающей на вход регистра 5 сдвига с обратными связями, и сигнатурой, которая формируется в индикаторе, существует однозначеное соответствие. Если в указанной последовательности изменится хотя.бы один бит информации, изменится и ее сигнатура, поэтому в примере глубина анализа, при которой сигнатуры в соответствующих точках схемы соответствуют эталонным, определяется по соответствию эпюр напряжений в этих точках для исправного и неисправного элемента. Таким образом, предлагаемое устройство локализует неисправности в проверяемых цифровых узлах, содержащих цепи обратной связи, до уровня элементов, позволяя уменьшить общее время поиска неисправностей в схемах без значительных аппаратурных затрат. Формула изобретения 1. Устр9йство для локализации неисправностей, содержащее генератор синхроимпульсов, генератор тестов, коммутатор, триггер управления, элемент И, логический анализатор реакций, причем логический анализатор реакций содержит два элемента задержки, одновибратор, элемент НЕ, переключатель, регистр сдвига, ре9 . гистр памяти, дешифратор, узел индикации, входы которого соединены соответственно с выходами дешифратора, входы которого соединены соответственно с выходами регистра памяти, информа1щонные входы которого соединены с выходами регистра сдвига, установочный вход которого соединен с входом одновибратора и является установочным входом логического анализатора реакций, информационный вход которого соединен с информационным входом регистра сдвига, синхровход которого соединен с выходом переключателя, первый вход которого соединен с выходо элемента НК, вход которого соединен с вторым входом переключателя и являе.тся синхровходом логического ана лизатора реакций, управляющий вход которого соединен с входом первого элемента задержки, выход которого соединен с синхровходом регистра .памяти, и с входом второго элемента задержки, выход которого соединен с входом одновибратора, информацион ный вход логического анализатора ре акций соединен с выходом коммутатора, вход которого соединен с контактом проверяемого узла, группа входов которого соединена соответственно с группой выходов генератор тестов, установочный вход которого соединен с установочным выходом логического анализатора реакций, с пе вым установочным входом триггера управления, прямой выход которого соединен с управляющим входом логического анализатора реакций, синх ровход которого соединен с выходом элемента И, первый вход которого соединен с инверсньш выходом триггера, синхровход генератора тестов соединен с синхровходом проверяемого узла, с выходом генератора синхроимпульсов, отличающееся тем, что, с целью повышения достоверности контроля, в него введен блок управления глубиной анализа, синхровход которого соединен с выходом генератора синхроимпульсов, выход блока управления глубиной анализа соединен с вторым установочным входом триггера управления. 2. Устройство по п. 1, отличающееся тем, что блок управления глубиной анализа содержит переключатель глубины анализа, узел памяти, узел сравнения кодов, счетчик, синхровход которого является входом блока, выход которого соединен с выходом узла сравнения кодов, с управляющим входом счетчика, группа выходов которого соединена соответственно с первой группой йходов узла сравнения кодов, вторая группа входов которого соединена соответственно с группой выходов узла памяти, вход которого соединен с выходом переключателя глубины анализа. Источники информации, принятые во внимание при экспертизе 1. Электроника, 1977, № 5, с. 24. 2.Патент США 3976861, кл. G 06 F 11/00, опублик. 1976 (прототип).

фуг./

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Устройство для контроля и диагностики цифровых блоков | 1986 |

|

SU1388871A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Сигнатурный анализатор | 1986 |

|

SU1388869A1 |

| Многовходовый сигнатурный анализатор | 1986 |

|

SU1383362A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

77

&.

61rj

dxoff dSot/vffot/

UH(f)OffMff Vt/

w

нг

Авторы

Даты

1982-02-07—Публикация

1980-02-15—Подача