Изобретение .относится к вычислительной технике и может использоваться для контроля дискретных объектов.

Целью изобретения является повышение надежности сигнатурного анали- затора за счет обеспечения контроля за правильностью процесса формирования сигнатур анализируемых последовательностей .

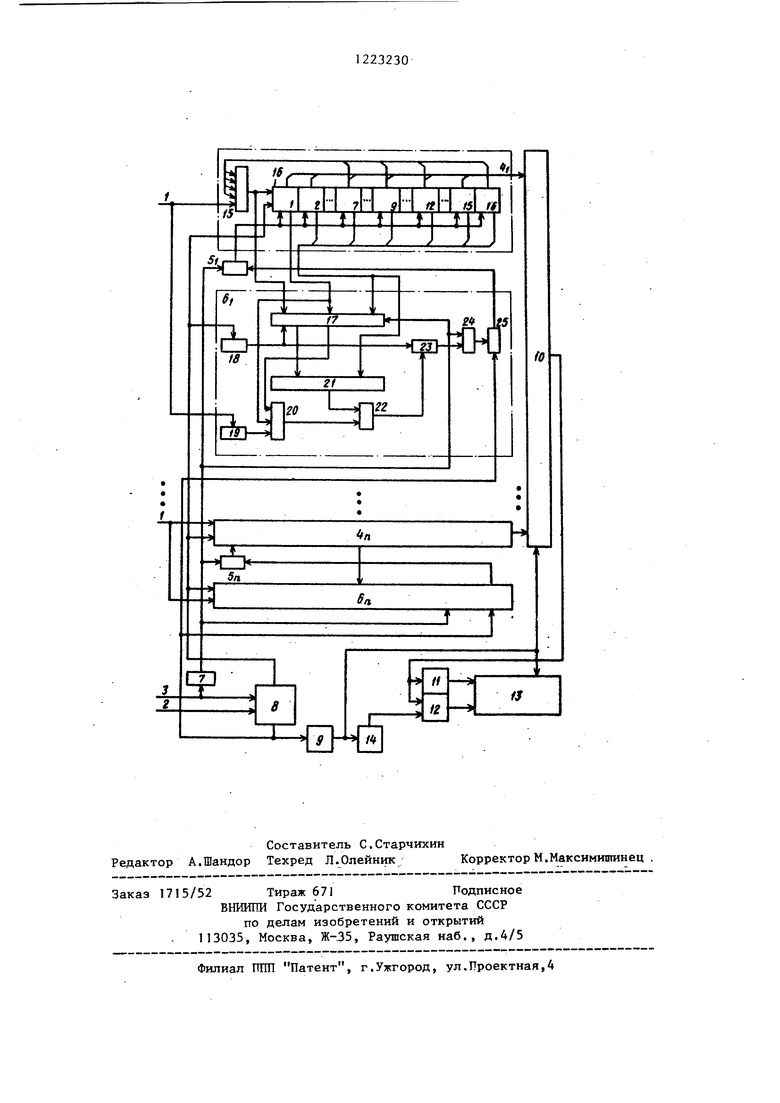

На чертеже представлена структур- ная схема сигнатурного анализатора.

Схема содержит инфор ационные входы 1, синхровход 2, управляющий , вход 3, N формирователей 4 сигнатур по числу информационных входов, N первых элементов ИЛИ 5, N блоков 6 контроля, блок 7 установки нуля, блок 8 формирования интервала обработки входных последовательностей, блок 9 синхронизации, коммутатор 10 знаковый генератор 11, блок 12 сравнения , блок I3 индикации, блок 14 памяти.

Каждый формирователь 4 сигнатур содержит сумматор 15 по модулю два и регистр 16 сдвига, разрядность ко- -торого определяется степенью образую . щег о полинома.

Каждый блок 6 контроля содержит регистр 17 разрядностью (М+1),где М - разрядность регистра 16 сдвига, два элемента J8 и 19 задержки, сумматор 20. по модулю два, узел 21 сравне- ;ния, элемент ИЛИ 22, второй элемент

30

Блок 8 определяет интер ботки двоичных последовател снимаемых с различных точек мой схемы. Сигнал, приходящ 3 анализатора, определяет о ний. С приходом этого сигна вырабатьшает импульс, устан щий в исходное состояние р е сдвига, регистры 17 и тригг выходе блока 8 появляется п тельность синхроимпульсов, щих на синхровходы регистро ле завершения процесса форм сигнатур на выходе блока 8 ся сигнал, поступающий на с вующие входы блоков 6 контр

И 23, триггер 24, первый элемент И 25,5 вход блока 9 синхронизации.

причем синхровход и информационный вход блока 6 соединены соответственно с входами первого 18 и второго 19 элементов задержки, установочный вход блока 6 соединен с нулевым вхо- дом триггера 24 и входом установки в ноль регистра 17, стробирующий вход блока 6 соединен с первым входом первого элемента И 25, первый вход группы информационных входов блока 6 сое- динен с первым информационным входом регистра 17, второй вход группы информационных входов блока 6 соединен с вторым информационным входом регистра 1 7 и первым входом сумматора 20 по модулю 2, (М-1) входов группы информационных входов блока 6 соединены с (М-1) информационными входами старших разрядов регистра 17 и перПолученные сигнатуры через комму татор 10 поступают на генератор 11 знаков и входы блока 12 сравнения. На другие входы блока J 2 сравнения поступают кодовые эталоны из блока 14 памяти. Синхронная работа блока 14 памяти, коммутатора 10 и блока 13 индикации обеспечивается блоком 9 синхронизации, который начинает работу после окончания каждого времен ного интервала обработки входных последовательностей, вьфабатьшает синхронизирующие импульсы и переклю чает коммутатор таким образом, чтобы он мог вьадавать на своих выходах коды всех регистров 16 сдвига после довательно. Синхронно с этим формируются адреса ячеек блока 14 памяти в которых хранятся соответствующие

вой группой входов узла 21 сравнения, 55 кодовые эталоны. В блоке 12 сравневыход первого элемента И 25 является выходом ошибки блока 6 контроля.

ния происходит сравнение кодов, поступающих одновременно из блока 4 па мяти и коммутатора 10, при обнаруже

5 0

5

Анализатор работает следующим образом.

Логические выражения сигналов на в ыходах сумматора 20 по модулю два и узла 21 сравнения соответственно имеют следующий вид:

q, ©а,.® q ©. . .@ q,, ; (О (Я ® Ч.а) V ( Яз) V...VX

(Я., ©Ч«). (2)

п где q- и qj - содержимое j-x разрядов

регистров 16 и 17 соответственно;

а - сигнал на выходе элемента 19

If

задержки.

Соотношение задержек, вносимых элементами 18 и 19, удовлетворяет соотношению i,

0

Т/2, где Т - период следования синхроимпульсов.

Блок 8 определяет интервал обработки двоичных последовательностей, снимаемых с различных точек исследуемой схемы. Сигнал, приходящий на вход 3 анализатора, определяет окно измерений. С приходом этого сигнала блок 7 вырабатьшает импульс, устанавливающий в исходное состояние р егистры 16 сдвига, регистры 17 и триггеры 24. На выходе блока 8 появляется последовательность синхроимпульсов, поступающих на синхровходы регистров 16. После завершения процесса формирования сигнатур на выходе блока 8 появляет- ся сигнал, поступающий на соответствующие входы блоков 6 контроля и

Полученные сигнатуры через коммутатор 10 поступают на генератор 11 знаков и входы блока 12 сравнения. На другие входы блока J 2 сравнения поступают кодовые эталоны из блока 14 памяти. Синхронная работа блока 14 памяти, коммутатора 10 и блока 13 индикации обеспечивается блоком 9 синхронизации, который начинает работу после окончания каждого временного интервала обработки входных последовательностей, вьфабатьшает синхронизирующие импульсы и переключает коммутатор таким образом, чтобы он мог вьадавать на своих выходах коды всех регистров 16 сдвига последовательно. Синхронно с этим формируются адреса ячеек блока 14 памяти, в которых хранятся соответствующие

кодовые эталоны. В блоке 12 сравнения происходит сравнение кодов, поступающих одновременно из блока 4 памяти и коммутатора 10, при обнаружеНИИ несоответствия управление передается блоку 13 с целью индикации ошибки. В знаковом генераторе 11 происходит преобразование полученных сигнатур в вид, удобный для восприятия.

Процесс формирования сигнатуры для частного случая образующего полинома cf/x/ l+x + описывается следующими уравнениями:

q,(t+1)a(t)@q(t))®

@q,3j (t) @q,6 (t)j(3)

) q;., (t), i ТЛё, (4)

где q;(t) и qj(t+l) - значения i-ro разряда регистра 16 сдвига соответственно до и после прихода синхроимпульса 5

a(t) - значение анализируемого разряда входной последовательности.

Если для всех i (, М-1) выполняется условие q q; , где

pa 17,

м+

q . - содержимое i-ro разряда регистна выходе узла 21 сравнения в силу выражения (2) присутствует потенциал логического нуля, если хотя бы для одного i равенство не выполняется, на выходе узла 21 присутствует потенциал логической единицы

Таким образом, если не вьшолняет- ся условие (3), сигнал логической единицы с выхода сумматора 20 по модулю два, пройдя через элемент 22 на вход элемента 23, в момент появления импульса на выходе элемента 18 задерки вызовет появление на выходе элемента 23 сигнала ошибки. Если не выполняется условие (4), то появление сигнала ошибки будет вызвано сигналом логической единицы с выхода узла 21. Сигнал ошибки устанавливает в единичное состояние триггер 24. №отульс с выхода блока 8, определяющий момент окончания окна измерений, появляясь на входе Элемента 25, на другом входе которого присутствует потенциал логической единицы с выхода триггера 24, вызывает пойвление на выходе блока 6 контроля сигнала ошибки, который,пройдя через соот- ветствзгющий элемент ИЛИ 5, сбрасьша- ет в ноль все разряды регистра 16 сдвига (или заносит в регистр 16 сдв .га какой-либо другой, вполне опреде- пенный код).

Таким образом, если в каком-лнбо из блоков 4 в процессе формирования

сигнатур анализируемых последовательностей произошел сбой, перед началом работы блока 9 синхронизации в регистре 16 сдвига соответствующего форми- 5 рователя )сигнатур устанавливается код, позволяющий при индикации выявить данное нежелательное событие.

Формула изобретения

0 Сигнатурный анализатор, содержащий N формирователей сигнатур по числу информационных входов анализатора, блок формирования итнтервала обработки входных последовательностей,

5 коммутатор, блок синхронизации, блок установки нуля, блок памяти, знаковый генератор, блок сравнения, блок индикации, причем первый и второй информационные входы блока индикации

0 соединены соответственно с выходами знакового генератора и блока сравнения , управляющий вход блока индикации соединен с управляющим входом коммутатора, входом блока памяти и выходом

5 блока синхронизации, вход запуска которого соединен с первым выходом блока формирования интервала обработки входных последовательностей, второй выход которого подключен к синх- ровходам формирователей сигнатур, информационные входы которых являются информационными входами анализатора, первые группы выходов формирователей сигнатур соединены с соответствующими группами информационных входов коммутатора, группа выходов которого связана с группой входов знакового .генератора и первой группой информационных входов блока сравнения, вторая, группа информационных входов которого соединена с группой выходов блока памяти, синхровход анализатора соединен с синхровходом блока формирования интервала обработки входных последовательностей, вход запуска

5 анализатора соединен с входом запуска блока формирования интервала обработки входных последовательностей и входом запуска блока установки нуля,. каждый формирователь сигнатур содер0 ясит регистр сдвига и сумматор по модулю два,.первый вход которого является информационным входом формирователя сигнатур, rpyima входов сумматора по модулю два соединена с груп5 пой выходов регистра сдвига, определяемых видом образующего многочлена, выход сумматора по модулю два соединен с информационным входом регнст0

5

0

pa сдвига, синхровход и вход установки в ноль регистра сдвига являются соответственно синхровходом и входом установки в ноль формировател сигнатур, группа разрядных выходов регистра сдвига является первой группой выходов формирователя сигнатур, выход сумматора по модулю два является первым выходом второй группы выходов формирователя сигнатур, выход первого разряда регистра сдвига является вторым выходом второй группы выходов формирователя сигнатур, выходы (М-1) старших разрядов регист pa сдвига, где М - разрядность регистра сдвига, являются (М-1) выходами второй группы выходов формирователя сигнатур, отличайщий- с я тем, что, с целью повьшения надежности за счет обеспечения контроля за правильностью процесса формирования сигнатур анализируемых последовательностей, он содержит N блоков контроля и группу элементов ИЛИ, выходы которых соединены с входами установки в ноль соответствующих формирователей сигнатур, вторые группы выходов которых соединены с группами информационных входов соот- ветствующих блоков контроля, установочные входы которых соединены с первыми входами элементов ИЛИ группы и выходом блока установки нуля, выходы ошибки блоков контроля соединены с вторыми входами соответствующих элементов ИЛИ группы, синхровходы блоков контроля соединены с синхровхо- дами формирователей сигнатур, информационные входы блоков контроля под- ключены к информационным входам соответствующих формирователей сигнатур, стробирующие входы блоков контроля соединены с входом запуска блока синхронизации, каждый из блоков конт

роля содержит два элемента задержки,

j 0 s 0 5 о

5

два элемента И, элемент ИЛИ, cyMi-ia- тор по модулю два, узел сравнения, регистр и триггер, причем синхровход и информационный вход блока контроля соединены соответственно с входами первого и второго элементов задержки, установочный вход блока контроля соединен с нулевым входом триггера и входом установки в ноль регистра, стробирующий вход блока контроля соединен с первым входом первого элемента И, первый вход группы информационных входов блока контроля соединен с первым информационным входом регистра, второй вход группы информационных входов блока контроля соединен с вторым информационным входом регистра и первым входом сумматора по модулю два, выход первого элемента задержки соединен с синхровходом регистра и первым входом второго элемента И, (М-1) входов группы информационных входов блока контроля соединены с соответствующими (М-1) информационными входами старших разрядов регистра и входами первой группы входов узла сравнения, группа выходов регистра, определяемых видом образующего многочлена соответствукадего формирователя сигнатур, соединена с группой входов сумматора по модулю два, (М-1). выходов старших разрядов регистра соеди- нены с соответствукядими входами второй группы входов узла сравнения, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом сумматора по модулю два, второй вход которого соединен с выходом второго элемента задержки, выход элемента ИЛИ соединен с вторым входом второго элемента И, выход которого соединен с единичным в-ходом триггера, выход которого соединен с вторым входом первого элемента И, выход которого является вьпсодом сшибки блока контроля.

16

r1

fl

tl-l 7П |-| Itl-l й| /

j Ум

fl

l-l

Ш

Л1

iif

±1.

5/.

4п

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

| Сигнатурный анализатор (его варианты) | 1984 |

|

SU1252784A1 |

| РЕЗЕРВИРОВАННАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2039372C1 |

| Сигнатурный анализатор | 1984 |

|

SU1179341A1 |

| Сигнатурный анализатор | 1987 |

|

SU1444776A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ | 1991 |

|

RU2065202C1 |

| Сигнатурный анализатор | 1983 |

|

SU1140123A1 |

| Многовходовый сигнатурный анализатор | 1986 |

|

SU1383362A1 |

| Сигнатурный анализатор | 1986 |

|

SU1361555A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля дискретных объектов. Целью изобретения является повьшение надежности сигнатурного анализатора за счет обеспечения контроля за правильностью процесса формирования сигнатур анализируемых последовательностей. Для дос тижения цели в сигнатурный анализатор, содержащий N формирователей сигнатур, блок установки нуля, блок формирования интервала обработки входных последовательностей, блок синхронизации, коммутатор, знаковый генератор, блок сравнения, блок памяти и блок индикации, дополнительно введены N блоков контроля и группа элементов ИЛИ. I ил. (Л СО ю со

| Авторское свидетельство СССР № 913385, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Логический анализатор | 1980 |

|

SU890396A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-04-07—Публикация

1983-05-20—Подача