Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении цифровых узлов повышенной надежности.

Цель изобретения - повышение быстродействия контроля дешифратора.

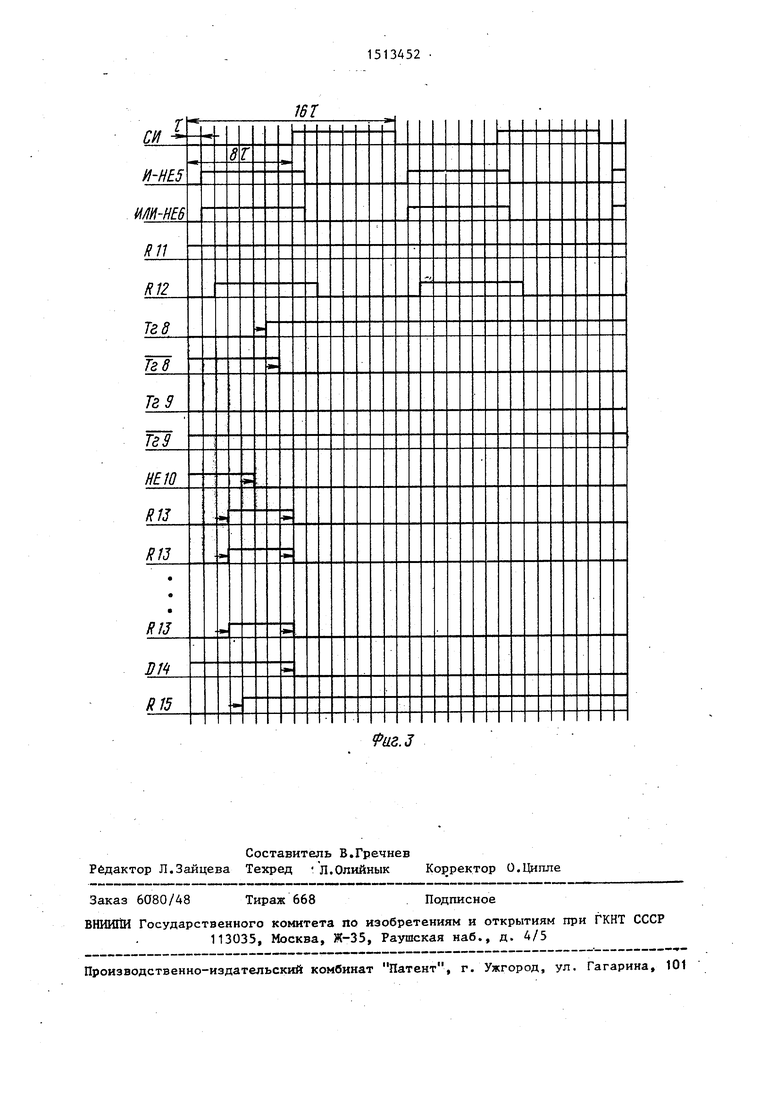

На фиг.1 приведена функциональная схема дешифратора на фиг,2 и 3 - временные диаграммы работы дешифратора в режиме контроля для случая нормальной работы и неисправности соответственно.

Дешифратор с контролем (фиг. 1) содержит тактовьй вход 1 дешифратора, входы 2 и 3 задания режима работы дешифратора, группу 4 -информационных входов дешифратора, элемент И-НЕ 5, элемент ИЛИ-НЕ 6, счетный триггер

элементов РАВНОЗНАЧНОСТЬ третьей группы 13, настраивая их на вьшол- нение операции конъюнкции.. В результате в целом на выходах группы -16 реализуется функция дешифратора. При этом сигнал логической 1 с выхода элемента 14 задержки также настраивает элемент РАВНОЗНАЧНОСТЬ 15 на

выполнение функции конъюнкции. Вследствие чего на первом контрольном выходе 17 дешифратора присутствует сигнал логического О, а на втором контрольном выходе 18 дешифратора сигнал логической 1.

В режиме контроля синхросерия (меандр) проходит с тактового входа 1 дешифратора через элементы И-НЕ 5 и ШШ-ИЕ 6, инвертируется и с задерж

| название | год | авторы | номер документа |

|---|---|---|---|

| Контролируемый регистр | 1988 |

|

SU1501063A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1228109A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1786482A1 |

| Устройство для вычисления булевых дифференциалов | 1988 |

|

SU1689942A1 |

| ИМИТАТОР ИР-60-500 ДЛЯ ОТЛАДКИ КОРАБЕЛЬНЫХ ЦИФРОВЫХ УПРАВЛЯЮЩИХ СИСТЕМ | 1998 |

|

RU2138846C1 |

| Универсальный логический модуль | 1988 |

|

SU1520505A1 |

| Дешифратор с самоконтролем | 1988 |

|

SU1614019A1 |

| Устройство для отладки цифровых систем | 1985 |

|

SU1254492A1 |

| Устройство для реализации логических функций | 1990 |

|

SU1739376A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении цифровых узлов повышенной надежности. Цель изобретения - повышение быстродействия контроля дешифратора. Дешифратор содержит тактовый вход 1 дешифратора, входы 2, 3 задания режима работы дешифратора, группу 4 информационных входов дешифратора, элемент И-НЕ 5, элемент ИЛИ-НЕ 6, счетный триггер 7, RSC-ТРИГГЕРЫ 8, 9, ЭЛЕМЕНТ НЕ 10, ГРУППЫ 11-13 ЭЛЕМЕНТОВ РАВНОЗНАЧНОСТЬ, элемент 14 задержки, элемент РАВНОЗНАЧНОСТЬ 15, группу 16 информационных выходов дешифратора, контрольные выходы 17, 18 дешифратора. В режиме контроля на выходах 17, 18 дешифратора при нормальной работе генерируется периодически изменяющийся сигнал. В случае неисправности какого-либо узла дешифратора - на выходах 17, 18 дешифратора присутствует единичный или нулевой потенциал. 3 ил.

триггеры 8 и 9, элемент НЕ 10, 20 кой на f , где 11-13 элементов РАВНОЗНАЧНОСТЬ,

на элементе, си элементы РАВНОЗ рой групп 11 и

элемент 14 задержки, элемент РАВНОЗНАЧНОСТЬ 15, группу 16 информационных выходов дешифратора, контрольные выходы 17 и 18 дешифратора.

Дешифратор с контролем работает следующим образом.

Дешифратор работает в двух режи- мах: в основном и в режиме контроля. Выбор режима осуш;ествляется состоянием входов 2 и 3 задания режима работы дешифратора. В основном ре.жиме на вход 2 дешифратора подается сигнал логического О, а на вход 3 дешифратора - сигнал логической I. В режиме контроля сигналы на входах 2 и 3 дешифратора меняются на противоположные, т.е. на вход 2 дешифратора подается сигнал логической 1, а на вход 3 дешифратора - сигнал логического О.

В основном режиме на выходе элемента И-НЕ 5 и на вторых входах элементов РАВНОЗНАЧНОСТЬ группы 11 присутствует сигнал логической 1. На |выходе элемента ИЛИ-НЕ 6 и на вто- рых входах элементов РАВНОЗНАЧНОСТЬ группы 12 присутствует сигнал логического О. Поэтому на выходах элементов РАВНОЗНАЧНОСТЬ первой группы 11 формируются прямые значения входных сигналов, а на выходах элементов РАВНОЗНАЧНОСТЬ второй группы 12 формируются инверсные значения входных сигналов. Счетньй триггер 7 обнулен и с инверсного выхода RSC-триггера 8 сигнал логической 1, являюш;ийся настроечным выходом счетчного триггера 7, поступает на (п+1)-е входы

средняя задержка

кой на f , где

на элементе, синхронно поступает на элементы РАВНОЗНАЧНОСТЬ первой и второй групп 11 и 12.

Период синхросерии (меандра) ограничивается снизу длительностью переходных процессов и составляет . Вследствие чего возникает необходимость учета рассогласования синхросерии как по фронту, так и по срезу в связи с разбросом длительностей задержек для различных, элементов. С этой целью счетньй триггер работает в режиме настройки. В исходном состоянии на настроечном выходе счетного триггера 7 присутствует уровен логической I и элементы РАВНОЗНАЧНОСТЬ третьей группы 13 и элемент РАВНОЗНАЧНОСТЬ 15 настраиваются на выполнение функции конъюнкции. Работа дешифратора в режиме контроля при тестовом наборе информационных сигналов I I I... I представлена на фиг.2. При первоначальном поступлении положительных импульсов на элементы РАВНОЗНАЧНОСТЬ третьей группы 13, настроенных на функцию конъюнкции, на их выходах вырабатываются сигналы логической I тогда, когда на всех входах этих элементов, .будут присутствовать сигналы логической I, при любом рассогласовании фронтов. Аналогично на выходе элемента РАВНОЗНАЧНОСТЬ 15 выработается сигнал логической | тогда, когда на всех вхо- дах будут присутствовать сигналы логической I. Сигнал логической | с элемента РАВНОЗНАЧНОСТИ 15, поступая на счетньй вход триггера 7, изменяет состояние первого RSC-триг51

гера 8 на противоположное. В результате на настроечном выходе триггера сформируется сигнал логического О при этом полярность входных сигналов на входах элементов РАВНОЗНАЧНОСТЬ третьей группы 13 остается еще положительной. Элементы РАВНОЗНАЧНОСТЬ группы 13 при сигнале на настроечном выходе, равном логическому О, настраиваются на функцию ИЛИ-НЕ. В результате на выходах элементов РАВНОЗНАЧНОСТЬ третьей группы 13 формируются сигналы логического О через время, равное величине задержки на соответствующем элементе РАВНОЗНАЧНОСТЬ группы 13. Именно этому времени и соответствует величина задержки элемента 14. Сигналы логического О с выходов элементов РАВНОЗНАЧНОСТЬ группы 13 поступают одновременно с сигналом логического О с выхода элемента задержки 14, в результате чего на выходе элемента РАВНОЗНАЧНОСТЬ 15 остается сигнал, равный логической I.

К времени прихода на входы элементов РАВНОЗНАЧНОСТЬ третьей группы 13 нулевых сигналов эти элементы, а также элемент РАВНОЗНАЧНОСТЬ 15 настроены на выполнение функции ИЛИ-НЕ На выходах элементов РАВНОЗНАЧНОСТЬ 13 вырабатьшаются сигналы логической 1 по совпадению всех сигналов логического О на входах. На вьрсо де элемента РАВНОЗНАЧНОСТЬ 15 вьфа- батывается сигнал логического О, что приводит к переписи информации с первого RSC-триггера 8 во второй RSC-триггер 9.

Таким образом, при исправном состоянии всех элементов устройства и связей между ними на контролируемых выходах 17 и 18 вьфабатьшаются серии импульсов.

В случае константных неисправностей любого из элементов И-НЕ 5, ИЛИ- НЕ 6, элементов РАВНОЗНАЧНОСТЬ группы 11-13 на контрольных выходах 17 и 18 дешифратора через время не более одного периода входной синхро- серии будут сформированы сигналы логического О или логической I. Один из примеров приведен на фиг.З.

Отсутствие синхросерии на входе 1 дешифратора приводит к появлению на выходах И-НЕ 5 и ИЛИ-НЕ 6 константных сигналов, что выявляется в режиме контроля.

452 6

Константная неисправность элемента РАВНОЗНАЧНОСТЬ 15, эквивалентная 1, проверяется в. основном режиме, когда исходное состояние первого контрольного выхода 17 дешифратора должно соответствовать логическому О.

Константная неисправность на пер-

0 вом входе 2 задания режима работы дешифратора, соответствующая констан- те 1, проверяется в основном режиме при тестовом наборе 000...О.

Константная неисправность на вто15 ром-еходе 3 задания режима работы дешифратора, эквивалентная О, выявляется также в основном режиме при тестовом наборе И 1 ... I . При этом в обоих случаях на первом контрольном

20 выходе 17 дешифратора будет выраба- тьшаться серия импульсов. Счетный триггер 7 и элемент 14 задержки проверяются в режиме контроля, деля частоту с выхода элемента РАВНО-

25 ЗНАЧНОСТЬ 15 на втором контрольном выходе 18 дешифратора.

Таким образом, производится автономное диагностирование дешифратора по двум контрольным выходам на

30 двух входных наборах.

Формула изобретения

35

Дешифратор с контролем, содержащий три группы элементов РАВНОЗНАЧНОСТЬ, счетный триггер, элемент РАВНОЗНАЧНОСТЬ и элемент И-НЕ, первый вход которого является тактовым вхо- 4Q дом дешифратора, i-й информационный вход группы дешифратора (14 , где п - число информационных входов группы дешифратора), соединен с первыми входами i-x элеме.нтов РАВНОЗНАЧ/5 НОСТЬ первой и второй групп, выход элемента И-НЕ соединен с вторьм входом первого элемента РАВНОЗНАЧНОСТЬ первой группы, второй вход элемента И-НЕ И нулевой установочньй вход

50 счетного триггера подключены к первому входу задания режима работы дешифратора, входы с первого по п-й элементов РАВНОЗНАЧНОСТЬ третьей группы соединен с выходами элементов

55 РАВНОЗНАЧНОСТЬ первой и второй групп в соответствии с формируемой консти- туентой единицы, инверсный выход счетного триггера соединен с (п+1)-. ми входами всех элементов РАВНОЗНАЧНОСТЬ третьей группы, выходы которых образуют группу информационных выходов дешифратора и соединены с соответствующими входами элемента РАВНОЗНАЧНОСТЬ, выход которого является первым контрольным выходом дешифратора, отличающийся тем, что, с целью повью1ения быстродейстмента РАВНОЗНАЧНОСТЬ и Я|Вляется вто рым контрольным выходом дешифратора первый и второй входы элемента ИЛИ подключены соответственно к тактов входу и второму входу задания режи работы дешифра-цора, выход элемента ИЛН-НЕ соединен с вторыми входами элементов РАВНОЗНАЧНОСТЬ второй гр

вия контроля дешифратора, в него вве- JQ пы, выход элемента И-НЕ соединен с

т А -ПГТ/ЛПГТ А.

дены элемент ИЛИ-НЕ и элемент задержки, причем инверсньй выход счетного триггера соединен с входом элемента задержки, в ыход которого соединен с соответствуюш {м входом элеWT

15

вторыми входами элементов РАВНОЗНА НОСТЬ первой группы с второго по п выход элемента РАВНОЗНАЧНОСТЬ соед нен со счетным входом счетного три гера.

аг.2

мента РАВНОЗНАЧНОСТЬ и Я|Вляется вторым контрольным выходом дешифратора, первый и второй входы элемента ИЛИ-НЕ подключены соответственно к тактовому входу и второму входу задания режима работы дешифра-цора, выход элемента ИЛН-НЕ соединен с вторыми входами элементов РАВНОЗНАЧНОСТЬ второй группы, выход элемента И-НЕ соединен с

т А -ПГТ/ЛПГТ А.

вторыми входами элементов РАВНОЗНАЧНОСТЬ первой группы с второго по п-й выход элемента РАВНОЗНАЧНОСТЬ соединен со счетным входом счетного триггера.

Составитель В.Гречнев Редактор Л.Зайцева Техред - л.Олийнык Корректор О.Цнпле

Заказ 6080/48

Тираж 668

ВНИШШ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г, Ужгород, ул. Гагарина, 101

Риг.З

Подписное

| Устройство для диагностики дешифраторов | 1976 |

|

SU703815A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1300476, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-10-07—Публикация

1988-01-25—Подача