1

Изобретение относится к вычислительной, технике и автоматике и может использоваться для проверки логических схем цифровых узлов ЭВМ.

Цель изобретения - расширение функциональных возможностей устройства за счет окончания контроля в динамическом режиме.

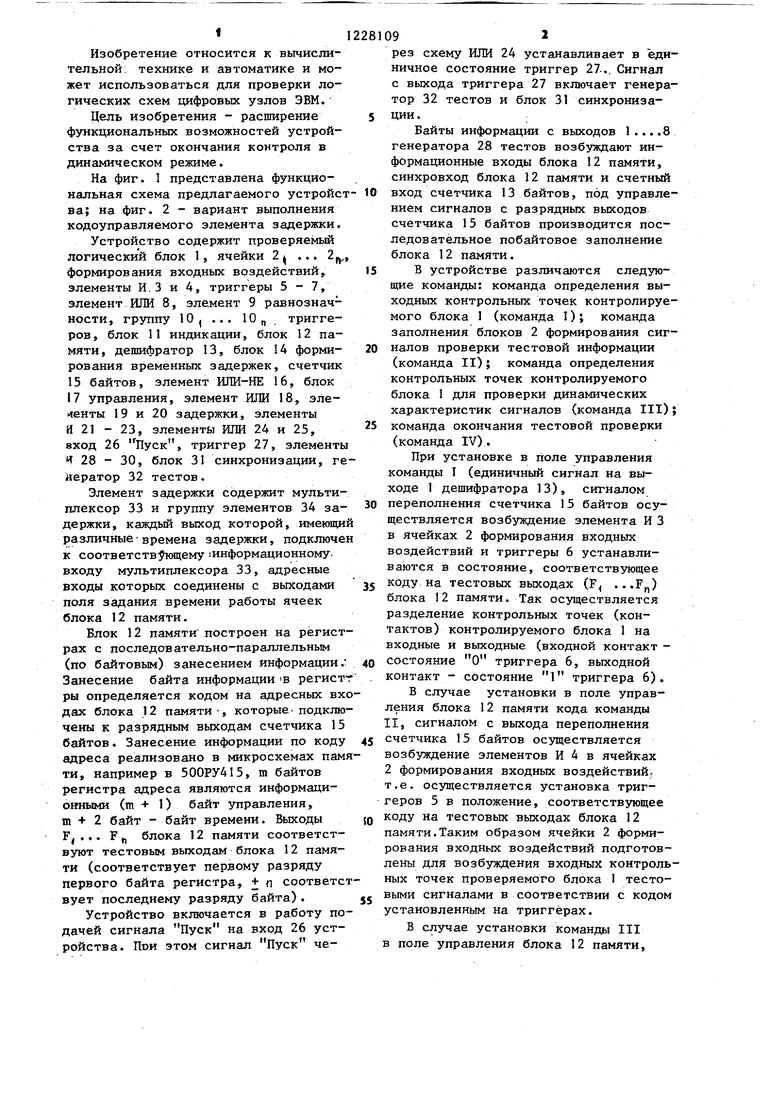

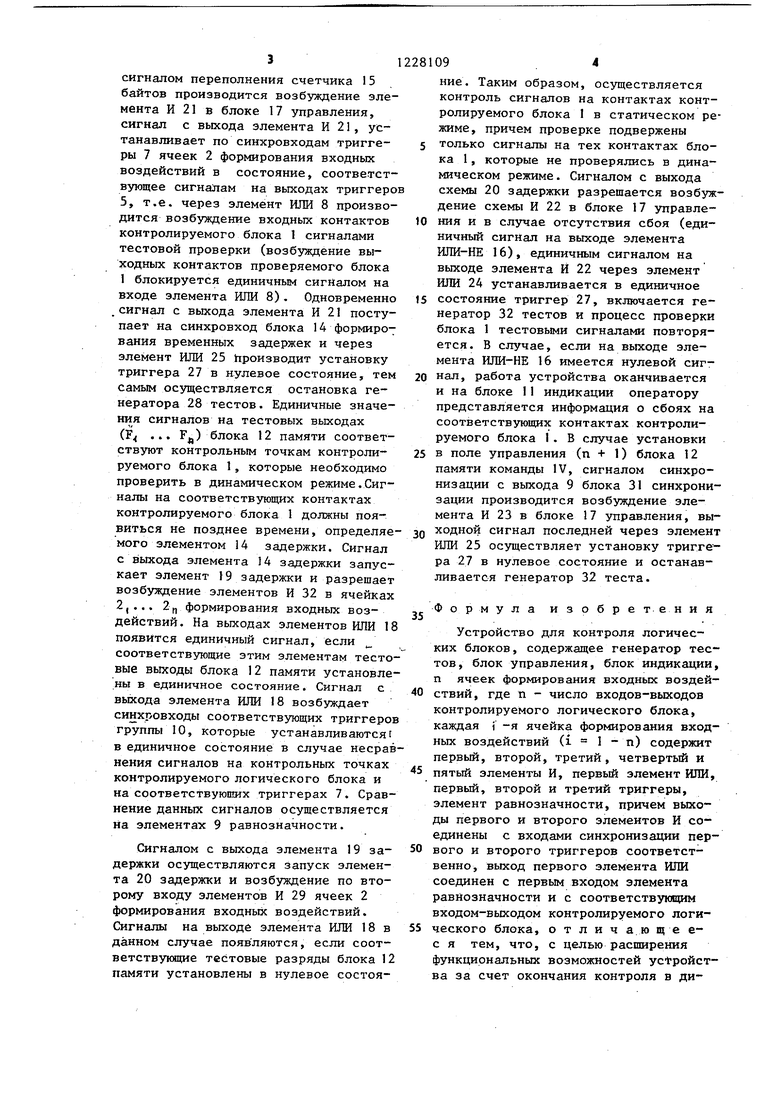

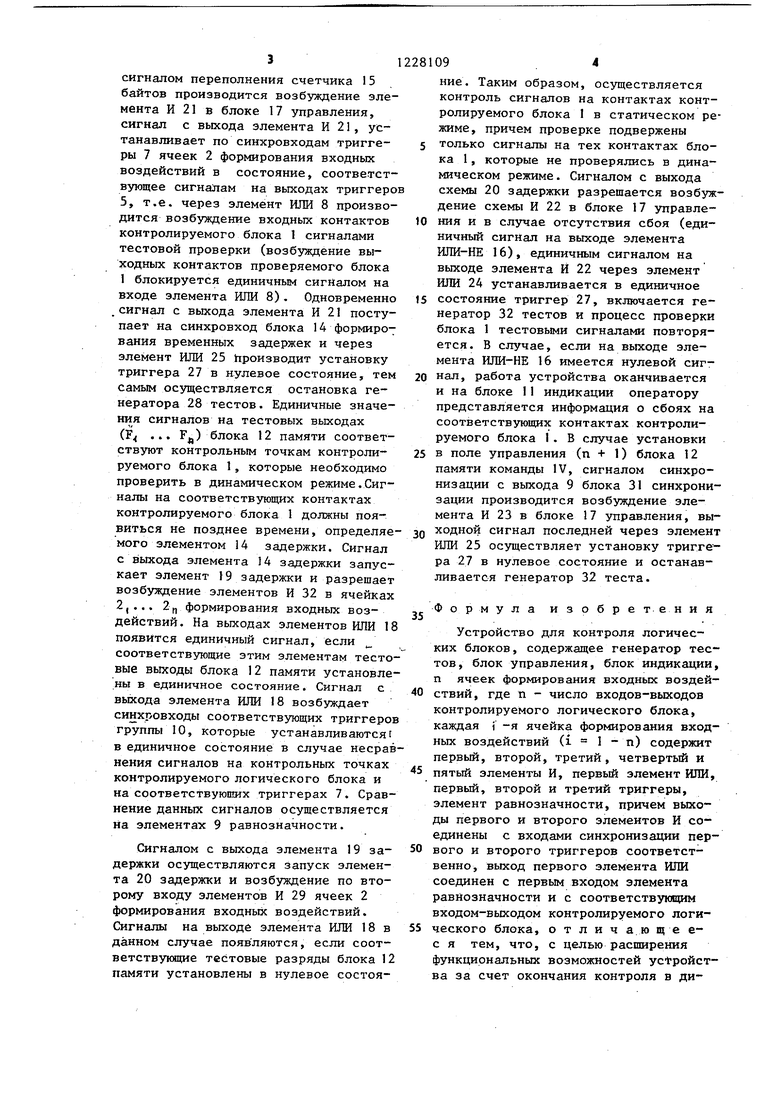

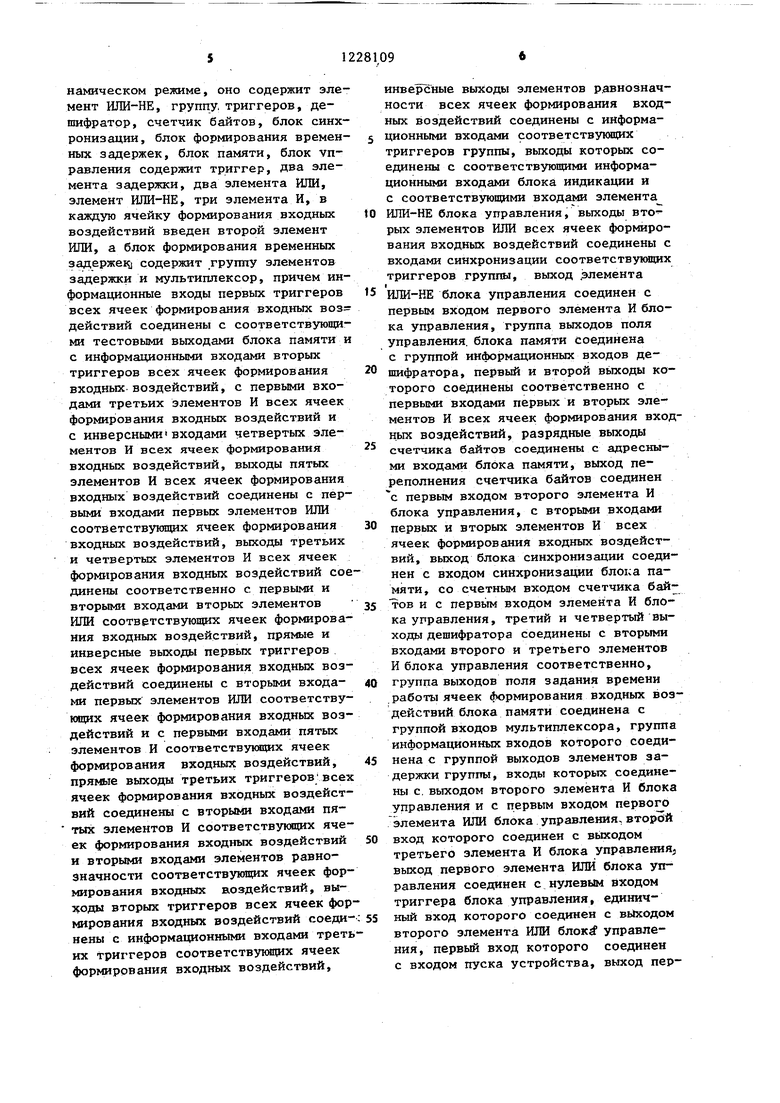

На фиг. 1 представлена функциональная схема предлагаемого устройст ва; на фиг. 2 - вариант выполнения кодоуправляемого элемента задержки. Устройство содержит проверяемьй логический блок 1, ячейки 2 ... 2, формирования входных воздействий, элементы И.З и 4, триггеры 5-7, элемент ИЛИ 8, элемент 9 равнозначности, группу 10, ... 10 „ триггеров, блок 11 индикации, блок 12 памяти , дешифратор 13, блок 14 форми- рования временных задержек, счетчик 15 байтов, элемент ИЛИ-НЕ 16, блок 17 управления, элемент ИЛИ 18, эле- 1енты 19 и 20 задержки, элементы И 21 - 23, элементы ИЛИ 24 и 25, вход 26 Пуск, триггер 27, элементы f 28 - 30, блок 31 синхронизации, ге йератор 32 тестов.

Элемент задержки содержит мультиплексор 33 и группу элементов 34 за- держки, каждый выход которой, имеющий различныевремена задержки, подключен к соответствующему информационному. входу мультиплексора 33, адресные входы которых соединены с выходами поля задания времени работы ячеек блока 12 памяти.

Блок 12 памяти построен на регистрах с последов ательно-параллельным (по байтовым) занесением информации. Занесение байта информации в регистт ры определяется кодом на адресных входах блока 12 памяти-, которые, подключены к разрядным выходам счетчика 15 байтов. Занесение информации по коду адреса реализовано в микросхемах памяти, например в 500РУ415, m байтов регистра адреса являются информационными (т + 1) байт управления, m + 2 байт - байт времени. Выходы F, ... F „ блока 12 памяти соответствуют тестовым выходам блока 12 памяти (соответствует первому разряду первого байта регистра, + п соответствует последнему разряду байта).

Устройство включается в работу подачей сигнала Пуск на вход 26 устройства. Пои этом сигнал Пуск че091

рез схему ИЛИ 24 устанавливает в единичное состояние триггер 27... Сигнал с выхода триггера 27 включает генератор 32 тестов и блок 31 синхронизации.

Байты информации с выходов 1 .... 8 генератора 28 тестов возбуждают информационные входы блока 12 памяти, синхровход блока 12 памяти и счетный вход счетчика 13 байтов, под управлением сигналов с разрядных выходов счетчика 15 байтов производится последовательное побайтовое заполнение блока 12 памяти.

В устройстве различаются следующие команды: команда определения выходных контрольных точек контролируемого блока 1 (команда I); команда заполнения блоков 2 формирования сигналов проверки тестовой информации (команда II); команда определения контрольных точек контролируемого блока 1 для проверки динамических характеристик сигналов (команда III) команда окончания тестовой проверки (команда IV).

При установке в поле управления команды I (единичный сигнал на выходе 1 дешифратора 13), сигналом переполнения счетчика 15 байтов осуществляется возбуждение элемента И 3 в ячейках 2 формирования входных воздействий и триггеры 6 устанавливаются в состояние, соответствующее коду.на тестовых выходах (F ...F) блока 12 памяти. Так осуществляется разделение контрольных точек (контактов) контролируемого блока 1 на входные и выходные (входной контакт - состояние О триггера 6, выходной контакт - состояние 1 триггера 6). В случае установки в поле управления блока 12 памяти кода команды II, сигналом с выхода переполнения счетчика 15 байтов осуществляется возбуждение элементов И 4 в ячейках 2 формирования входных воздействий- т.е. осуществляется установка триггеров 5 в положение, соответствующее коду на тестовьк выходах блока 12 памяти.Таким образом ячейки 2 формирования входных воздействий подготовлены для возбуждения входных контрольных точек проверяемого блока 1 тестовыми сигналами в соответствии с кодом установленным на триггерах.

В случае установки команды III в поле управления блока 12 памяти.

сигналом переполнения счетчика 15 байтов производится возбуждение элемента И 21 в блоке 17 управления, сигнал с выхода элемента И 21, устанавливает по синхровходам триггеры 7 ячеек 2 формирования входных воздействий в состояние, соответствующее сигналам на выходах триггеров 5, т.е. через элемент ИЛИ 8 производится возбуждение входных контактов контролируемого блока 1 сигналами тестовой проверки (возбуждение выходных контактов проверяемого блока 1 блокируется единичным сигналом на входе элемента ИЛИ 8). Одновременно сигнал с выхода элемента И 21 поступает на синхровход блока 14 формирования временных задержек и через элемент ИЛИ 25 йроизводит установку триггера 27 в нулевое состояние, тем самым осуществляется остановка генератора 28 тестов. Единичные значения сигналов на тестовых выходах (F ... F,) блока 12 памяти соответствуют контрольным точкам контролируемого блока 1, которые необходимо проверить в динамическом режиме.Сигналы на соответствующих контактах контролируемого блока 1 должны пояиться не позднее времени, определяемого элементом 14 задержки. Сигнал с выхода элемента 14 задержки запускает элемент 19 задержки и разрешает возбуждение элементов И 32 в ячейках 2,... 2f, формирования входных возействий. На выходах элементов ИЛИ 18 появится единичный сигнал, если соответствующие этим элементам тестовые выходы блока 12 памяти установлены в единичное состояние. Сигнал с ыхода элемента ИЛИ 18 возбуждает синхровходы соответствующих триггеров группы 10, которые устанавливаются единичное состояние в случае несравнения сигналов на контрольных точках контролируемого логического блока и на соответствующих триггерах 7. Сравение данных сигналов осуществляется а элементах 9 равнозначности.

Сигналом с выхода элемента 19 заержки осуществляются запуск элемента 20 задержки и возбуждение по второму входу элементов И 29 ячеек 2 формирования входных воздействий. Сигналы на выходе элемента ИЛИ 18 в анном случае появляются, если соотетствующие тестовые разряды блока 12 памяти установлены в нулевое состоя28109 . 4

ние. Таким образом, осуществляется контроль сигналов на контактах контролируемого блока 1 в статическом режиме, причем проверке подвержены

5 только сигналы на тех контактах блока 1, которые не проверялись в динамическом режиме. Сигналом с выхода схемы 20 задержки разрешается возбуждение схемы И 22 в блоке 17 управлеJO ния и в случае отсутствия сбоя (единичный сигнал на выходе элемента ШШ-НЕ 16), единичным сигналом на выходе элемента И 22 через элемент ИЛИ 24 устанавливается в единичное

15 состояние триггер 27, включается генератор 32 тестов и процесс проверки блока 1 тестовыми сигналами повторяется. В случае, если на выходе элемента ИЛИ-НЕ 16 имеется нулевой сиг

нал, работа устройства оканчивается и на блоке 11 индикации оператору представляется информация о сбоях на соответствующих контактах контролируемого блока I. В случае установки

в поле управления (п + 1) блока 12 памяти команды IV, сигналом синхронизации с выхода 9 блока 31 синхронизации производится возбуждение элемента И 23 в блоке 17 управления, выходной сигнал последней через элемент ИЛИ 25 осуществляет установку триггера 27 в нулевое состояние и останавливается генератор 32 теста.

Формула изобретения

Устройство для контроля логических блоков, содержащее генератор тестов, блок управления, блок индикации, п ячеек формирования входных воздействий, где п - число входов-выходов контролируемого логического блока, каждая i -я ячейка формирования входных воздействий (i 1 - п) содержит первый, второй, третий, четвертый и

пятый элементы И, первый элемент ИЛИ, первый, второй и третий триггеры, элемент равнозначности, причем выходы первого и второго элементов И соединены с входами синхронизации первого и второго триггеров соответственно, выход первого элемента ИЛИ соединен с первым входом элемента равнозначности и с соответствующим входом-выходом контролируемого логического блока, о т л и ч а ю щ е е- с я тем, что, с целью расширения функциональные: возможностей устройства за счет окончания контроля в динамическом режиме, оно содержит элемент ИЛИ-НЕ, группу, триггеров, дешифратор, счетчик байтов, блок синхронизации, блок формирования времен- ных задержек, блок памяти, блок управления содержит триггер, два элемента задержки, два элемента ИЛИ, элемент ИЛИ-НЕ, три элемента И, в калсдую ячейку формирования входных воздействий введен второй элемент ИЛИ, а блок формирования временных зa.дepжeкJ содержит .группу элементов задержки и мультиплексор, причем информационные входы первых триггеров всех ячеек формирования входных воз: действий соединены с соответствующими тестовыми выходами блока памяти и с информационными входами вторых триггеров всех ячеек формирования входных воздействий, с первыми входами третьих элементов И всех ячеек формир ования входных воздействий и с инверсными входами четвертых элементов И всех ячеек формирования входньк воздействий, выходы пятых элементов И всех ячеек формирования входных воздействий соединены с первыми входами первых элементов ИЛИ соответствукшщх ячеек формирования входных воздействий, выходы третьих и четвертых элементов И всех ячеек формирования входных воздействий соединены соответственно с первыми и вторы1«1 входами вторых элементов ИЛИ соответствующих ячеек формирования входных воздействий, и инверсные выходы первых триггеров всех ячеек формирования входных воздействий соединены с вторыми входа- ми первых элементов ИЛИ соответствующих ячеек формирования входных воздействий и с первыми входами пятых элементов И соответствующих ячеек формирования входных воздействий, прямлю выходы третьих триггеров всех ячеек формирования входных воздействий соединены с вторыми входами пятых элементов И соответствующих ячеек формирования входных воздействий и вторыми входами элементов равнозначности соответствующих ячеек формирования входных воздействий, выходы вторых триггеров всех ячеек формирования входных воздействий соединены с информационными входами третьих триггеров соответствукщих ячеек формирования входных воздействий.

инверсные выходы элементов равнозначности всех ячеек формирования входных воздействий соединены с информационными входами соответствукицих триггеров группы, выходы которых соединены с соответствующими информационными входами блока индикации и с соответствующими входами элемента ИЛИ-НЕ блока управления, выходы вто- рых элементов ИЛИ всех ячеек формирования входных воздействий соединены с входами синхронизации соответствующих триггеров групгал, выход Элемента

ШШ-НЕ блока управления соединен с первым входом первого элемента И блока управления, труппа выходов поля управления, блока памяти соединена с группой информационных входов дешифратора, первый и второй выходы которого соединены соответственно с первьпуи входами первых и вторых элементов И всех ячеек формирования вход ньгх воздействий, разрядные выходы счетчика байтов соединены с адресными входами блока памяти, выход переполнения счетчика байтов соединен с первым входом второго элемента И блока управления, с вторыми входами первых и вторых элементов И всех ячеек формирования входных воздействий, выход блока синхронизации соединен с входом синхронизации блока памяти, со счетным входом счетчика бай- тов и с первьтм входом элемента И блока управления, третий и четвертый выходы дешифратора соединены с вторыми входами второго и третьего элементов И блока управления соответственно, группа выходов поля задания времени работы ячеек формирования входных воздействий блока памяти соединена с группой входов мультиплексора, группа информационных входов которого соединена с группой выходов элементов задержки группы, входы которых соединены с, выходом второго элемента И блока управления и с первым входом первого элемента ИЛИ блока управления, второй вход которого соединен с выходом третьего элемента И блока управления. выход первого элемента ШШ блока управления соединен с нулевым входом триггера блока управления, единичный вход которого соединен с выходом второго элемента ИЛИ блок управления, первый вход которого соединен с входом пуска устройства, выход первого элемента И блока управления соединен с вторым входом второго элемента ИЛИ блока управления, выход мультиплексора соединен с вторым входом третьих элементов И всех ячеек формирования входных воздействий и через первый элемент задержки .блока управления с прямыми входами четвертых элементов И всех ячеек формирования входных воздействий и с входом второго элемента задержки блока 2

2281098

управления, выход которого соединен с вторым входом первого элемента И блока управления, выход триггера блока управления .соединен с входами 5 пуска блока синхронизации и генератора тестов, выходы которого соеди - нены с информационными входами блока памяти, синхровходы третьих триггеров всех ячеек формирования вход- 10 ных воздействий соединены с выходом второго элемента И блока управления.

9 i

,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1986 |

|

SU1339568A1 |

| Устройство для контроля монтажа | 1990 |

|

SU1785001A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1319035A1 |

| Устройство для контроля интегральных схем | 1983 |

|

SU1182520A1 |

| Устройство тестового контроля цифровых блоков | 1985 |

|

SU1315982A1 |

| Устройство для контроля | 1981 |

|

SU1072052A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано: для тестового контроля логических блоков. Цель изобретения обеспечение контроля в динамическом режиме. Устройство содержит блок ввода, блок памяти тестов, п ячеек формирования входных воздействий, блок управления, который синхронизирует по времени п ячеек формирования входных воздействий (где п - число входов-выходов контролируемого логического блока), запускает и останавливает блок ввода. В зависимости от информации поля управления блока памяти тестов происходит разделение контрольных вьгоодов логического блока на входные и выходные. Причем возможен контроль в статическом режиме тех контактов, которые не проверялись в динамическом режиме. Выходная реакция логического блока записьшается в регистр, а с него попадает на блок индикации. 2 ил. i (Л

фиг, 2

Редактор Ю.Середа

Составитель А.Сиротская Техред И.Попович

Заказ 2288/50

Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Корректор А.Обручар

| Устройство для проверки функционирования логических схем | 1980 |

|

SU955072A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление в центрифугах для регулирования количества жидкости или газа, оставляемых в обрабатываемом в формах материале, в особенности при пробеливании рафинада | 0 |

|

SU74A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-04-30—Публикация

1984-02-29—Подача