Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2012 |

|

RU2503993C1 |

| Устройство ассоциативного распознавания образов | 1985 |

|

SU1330644A1 |

| Устройство для вычисления булевых дифференциалов | 1988 |

|

SU1689942A1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1997 |

|

RU2146840C1 |

| Устройство для реализации булевых функций | 1982 |

|

SU1032451A1 |

| Универсальный вычислительный автомат | 1983 |

|

SU1196844A1 |

| Конвейерное устройство для вычисления сумм произведений | 1989 |

|

SU1686437A1 |

| Ячейка однородной структуры | 1989 |

|

SU1674104A1 |

| Устройство для лексического анализа программ | 1987 |

|

SU1418757A1 |

| Программируемое логическое устройство | 1991 |

|

SU1777133A1 |

Использование: в машинах логического вывода систем искусственного интеллекта. Сущность изобретения: устройство позволяет расширить функциональные возможности за счет реализации режима конъюнкции символьных конъюнкций. Устройство содержит две группы элементов И 3, 4, четыре группы элементов ИЛИ 7, 10-12, четыре группы триггеров 1, 2, 8, 9, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 5, группу элементов РАВНОЗНАЧНОСТЬ 6, группу элементов И-НЕ 13, элемент И 14. 7-8-12- 6-13-14-3, 1-11-5-13-14-3, 10-9-11-3, 10-9-5-13-14-4, 1-5-13-14-3.1 ил.

VJ

GJ

о

CJ

VI

о

Изобретение относится к области вычислительной техники и может быть использовано в машинах логического вывода систем искусственного интеллекта.

Известно устройство для объединения множеств, содержащее элементы И, ИЛИ, НЕ.

Недостатком такого устройства являются малые функциональные возможности.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее первый и второй счетчики, первый, второй, третий и четвертый блоки элементов И, первый и второй блоки элементов ИЛИ, блок памяти, первый и второй регистры, первый и второй дешифраторы, схему сравнения и блок управления, причем вход адреса элементов первого множества устройства соединен с информационным входом первого сметчика, выходы первого и второго счетчиков соединены с первыми входами первого и второго блоков элементов И соответственно, выходы которых соединены с первым и вторым входами первого блока элементов ИЛИ, выход которого соединен с адресным входом блока памяти, выход которого соединен с информационным входом первого регистра, выход которого соединен с первым входом схемы сравнения и первым входом третьего блока элементов И, выходы третьего и четвертого блоков элементов И соединены соответственно с первым и вторым входами второго блока элементов ИЛИ, выход которого является информационным выходом устройства, установочный вход и вход запуска устройства соединены с первым и вторым входами блока управления соответственно, первый выход которого соединен с выходом сигнала окончания работы устройства, второй, третий, четвертый, пятый и шестой выходы блока управления соединены соответственно с вторым входом первого блока элементов И, вторым входом второго блока элементов И, со счетным входом второго счетчика, с вторым входом третьего блока элементов И и с вторым входом четвертого блока элементов И, выход первого дешифратора соединен с третьим входом блока управления, седьмой выход которого соединен со счетным входом первого счетчика и входом записи первого регистра, информационный вход второго счетчика соединен с входом адреса элементов второго множества устройства, выход первого регистра соединен с входом первого дешифратора, выход блока памяти соединен с информационным входом второго регистра, выход которого соединен с вторым входом схемы сравнения,

с первым входом четвертого блока элементов И и входом второго дешифратора, выход которого соединен с четвертым входом блока управления, пятый и шестой входы которого соединены с выходом Равно и входом Меньше схемы сравнения соответственно, четвертый выход блока управления соединен с входом записи второго регистра, причем блок управления содержит счетчик

0 команд, узел памяти команд, регистр, дешифратор команд, первую группу из двенадцати элементов И, первый, второй, третий элементы задержки, генератор импульсов, первый, второй и третий элементы

5 ИЛИ, первый вход первого элемента ИЛИ соединен с первым входом блока управления, выход первого элемента ИЛИ соединен с входом основа генератора импульсов, второй вход блока управления соединен с вхо0 дом запуска генератора, выход которого соединен с первыми входами первой группы элементов И блока управления, вторые входы первой группы элементов И блока управления соединены с выходами дешиф5 ратора команд, причем выходы первого, второго, третьего, четвертого, пятого, шестого элементов И первой группы блока управления соединены с вторым, седьмым, третьим, четвертым, пятым и шестым выхо0 дами блока управления соответственно, выходы с седьмого по одинадцатый элементов И первой группы блока управления соединены с первыми входами элементов И второй группы блока управления, выход

5 двенадцатого элемента И первой группы блока управления соединен с первым выходом блока управления и вторым входом первого элемента ИЛИ, вторые входы первого и второго элементов И второй группы

0 блока управления соединены с третьим входом блока управления, вторые входы третьего, четвертого, пятого элементов И второй группы блока управления соединены с четвертым, пятым и шестым входами

5 блока управления соответственно, четвертый вход блока управления соединен с третьим входом первого элемента И второй группы блока управления, выходы элементов И второй группы блока управления сое0 динены с входами второго элемента ИЛИ, выход которого соединен с входом первого элемента задержки, выход которого соединен со счетным входом счетчика команд, установочный вход которого соединен с вы5 ходом второго элемента задержки, вход которого соединен с выходом первого элемента ИЛИ, вход третьего элемента задержки соединен с установочным входом регистра и выходом генератора импульсов, входы дешифратора команд соединены с

группой выходов поля микрокоманды узла памяти команд, группа выходов поля местного управления которого присоединена к информационным входам регистра, выход которого соединен с первыми входами элементов И третьей группы блока управления, вторые входы элементов И которой соединены с выходом третьего элемента задержки, выходы элементов И третьей группы блока управления соединены с информационными входами счетчика команд, выход которого соединен с адресным входом узла памяти команд.

Недостатком известного устройства являются малые функциональные возможности.

Технические средства известного устройства ориентированы на микропрограммное вычисление объединения двух множеств элементов, в числовом или символьном виде, причем каждое множество представляется кодами чисел. В ряде задач в области искусственного интеллекта, кроме операций объединения множеств, часто бывает необходимо решать задачи логического вывода. В этом случае необходимо, например, определить конъюнкции некоторых посылок. Однако устройство не позволяет получать конъюнкции посылок, заданных в виде символов.

Целью изобретения является расширение функциональных возможностей.

Поставленная цель достигается тем, что в устройство для реализации логических функций, содержащее две группы п триггеров (2п - количество аргументов), две группы п элементов И, группу п элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, группу п элементов РАВНОЗНАЧНОСТЬ и первую п элементов ИЛИ, причем выходы i-x (i 1, п) триггеров первой и второй групп соединены соответственно с первым и вторым входами 1-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы, выходы 1-х элементов И первой и второй групп являются соответственно i-ми выходами первой и второй групп устройства, дополнительно введены третья и четвертая группы п элементов ИЛИ, группа п элементов И-НЕ и элемент И, причем i-й вход первой группы устройства подключен к входу установки в 1 i-ro триггера первой группы и первому входу 1-го элемента ИЛИ первой группы, выход которого подключен к входу установки 1 i-ro триггера третьей группы, i-вход второй группы устройства подключен к входу установки в 1 i-ro триггера второй группы и первому входу i-ro элемента ИЛИ второй группы, выход которого соединен с входом установки в 1 i-ro триггера четвертой группы, i-входы

третьей и четвертой групп устройства подключены к вторым входам 1-х элементов ИЛИ соответственно первой и второй групп, вход сброса устройства подключен к входам

установки в О всех триггеров с первой по четвертую групп, i-x триггеров первой и второй групп соединены соответственно с первым и вторым входами i-ro элемента ИЛИ третьей группы, выход которого соединен

0 с первым входом i-ro элемента И первой группы, выход i-ro триггера третьей группы соединен с первыми входами i-ro элемента ИЛИ четвертой группы и i-ro элемента РАВНОЗНАЧНОСТЬ группы,

5 второй вход которого соединен с выходом 1-го триггера четвертой группы, и вторым входом 1-го элемента ИЛИ четвертой группы, выход которого соединен с первым входом i-ro элемента И второй группы, вто0 рые входы элементов И первой и второй групп соединены с выходом элемента И, i-й вход которого соединен с выходом i-ro элемента И-НЕ группы, первый и второй входы которого соединены с выходом соответсг5 венно i-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы и i-ro элемента РАВНОЗНАЧНОСТЬ группы.

Сущность изобретения заключается в расширении функциональных возможно0 стей путем реализации режима конъюнкции символьных конъюнкций.

Этот режим заключается в приеме на первую и третью, вторую и четвертую группы триггеров импульсов неинверсного и

5 инверсного значений переменных символьных конъюнкций первой и второй конъюнкций соответственно и в получении на выходах элементов И первой и второй групп объединения двух множеств символьных

0 конъюнкций. В том случае, если хотя бы в одном разряде переменные ортогональны (противоположны по знаку инверсирова- ния) формируется пустая (нулевая) конъюнкция.

5 При использовании предлагаемого устройства для реализации логических функций может быть получен положительный эффект расширения функциональных возможностей путем реализации функции

0 конъюнкции символьных конъюнкций, необходимой, например, в системах логического вывода.

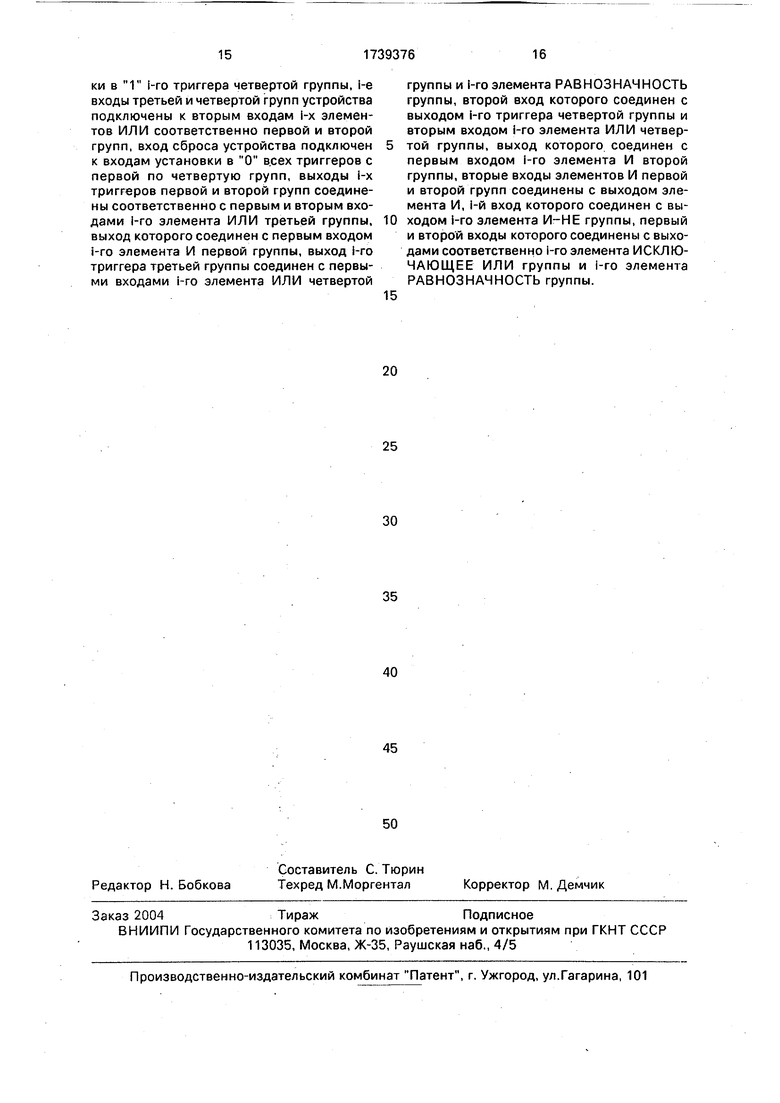

На чертеже представлена функциональная схема устройства.

5 Устройство для реализации логических функций содержит две группы п триггеров 1.1-1.П и 2.1-2.П (п - количество аргументов), две группы п элементов И 3.1-З.п и 4.1-4.П, группу п элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 5.1-5.П, группу п элементов РАВНОЗНАЧНОСТЬ 6.1-б.п, первую группу п элементов ИЛИ 7.1-7.П, третья и четвертая группы п триггеров 8.1-S.n, 9.1-Э.п, вторую 10.1-10.п, третью 11.1-11.п и четвертую 12.1-12.п группы п элементов ИЛИ, группу п элементов И-НЕ 13.1-13.пи элемент И 14, первая группа выходов 15.1-15.П, первая группа входов 16.1-16.п, вторая группа входов 17.1-17.П, третья группа входов 18.1- 18.п, четвертая группа входов 19.1-19.п, вход 20 сброса, вторая группа выходов 21.1- 21.п.

Выходы 1-х (i 1, п) триггеров первой 1.1-1.П и второй 2.1-2.П групп соединены соответственно с первым и вторым входами 1-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы 5.1-5.п. Выходы i-x элементов И первой 3.1-З.п и второй 4.1-4.П групп являются соответственно i-ми выходами первой 15.1- 15.п и второй 21.1-21.п групп устройства. 1-й вход первой группы входов 16.1-16.п устройства подключен к входу установки в 1 1-го триггера 1.1 -1.п первой группы и первому входу i-ro элемента ИЛИ 7.1-7.П первой группы, выход которого подключен к входу установки в 1 i-ro триггера третьей группы 8.1-8.п. i-й вход второй группы входов 17.1-17.п устройства подключен к входу установки в 1 i-ro триггера 2.1-2.П второй группы и первому входу i-ro элемента ИЛИ 10.1-10.п второй группы, выход которого соединен с входом установки в 1 i-ro триггера четвертой группы 8.1-8.п. 1-е входы третьей 18.1-18.п и четвертой 19.1- 19.п групп входов устройства подключены к вторым входам i-x элементов ИЛИ соответственно первой 7.1-7.П и второй 10.1-10.п групп. Вход 20 сброса устройства подключен к входам установки в О всех триггеров 1, 2, 8 и 9 с первой по четвертую групп. Выходы i-x триггеров первой 1.1-1.П и второй 2.1-2.П групп соединены соответственно с первым и вторым входами i-ro элемента ИЛИ 11.1-11.п третьей группы, выход которого соединен с первым входом i-ro элемен- та И 3.1-З.п первой группы. Выход i-ro триггера третьей группы соединен с первыми входами i-ro элемента ИЛИ 12.1-12.п четвертой группы и i-ro элемента РАВНОЗНАЧНОСТЬ 6.1-б.п, второй вход которо- го соединен с выходом i-ro триггера 9.1-9.П четвертой группы и вторым входом i-ro элемента ИЛИ 12.1-12.п четвертой группы, выход которого соединен с первым входом i-ro элемента И 4.1-4.П второй группы. Вторые входы элементов И первой 3.1-З.п и второй 4.1-4.П групп соединены с выходом элемента И 14, i-й вход которого соединен с выходом i-ro элемента И-НЕ 13.1-13. п, первый и второй входы которого

соединены с выходом соответственно i-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5.1-5.п и i-ro элемента РАВНОЗНАЧНОСТЬ 6.1-б.п.

Первая группа п триггеров 1.1-l.n предназначена для запоминания импульсов записи i-x (i 1, п неинверсных переменных в первой символьной конъюнкции с соответствующих входов 16.1-16.П и может быть реализована на интегральных микросхемах 155ТМ2.

Вторая группа п триггеров 2.1-2.п предназначена для запоминания импульсов записи i-x (i 1, п) неинверсных переменных во второй символьной конъюнкции с соответствующих входов 17.1-17.п и может быть реализована на интегральных микросхемах 155ТМ2.

Первая группа п элементов И 3.1-З.п предназначена для формирования на группе выходов 15 первого разряда кода символа конъюнкции двух символьных конъюнкций, заданных кодами на выходах триггеров групп 1,8 и 2,9 соответственно.

Вторая группа п элементов И 4.1-4.П предназначена для формирования на группе выходов 16 второго разряда кода символа конъюнкции двух символьных конъюнкций.

Группа п элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 5.1-б.п предназначена для фиксации наличия в первых разрядах кодов первой и второй символьных конъюнкций одной единицы (с выходов соответствующих триггеров 1 и 2), что в дальнейшем используется для определения факта ортогональности в i-м разряде, т.е. наличия противоположных существенной переменных: инверсная - неинверсная, неинверсная - инверсная. Группа п элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 5.1-S.n может быть реализована, например, на интегральных микросхемах 555ЛП12.

Группа п элементов РАВНОЗНАЧНОСТЬ 6.1-б.п предназначена для фиксации во вторых разрядах кодов первой и второй символьных конъюнкций наличия одинаковых значений логических сигналов, что в дальнейшем используется для определения ортогональности в i-м разряде, и мо- .жет быть реализована, например, на интегральных микросхемах 155ЛП5.

Первая группа п элементов ИЛИ 7.1-7.П предназначена для установки соответствующих триггеров 8.1-8.П в случае записи неинверсного значения существенной символьной переменной в первой символьной конъюнкции импульсами по входам 16 или записи инверсного значения переменной импульсами по входам 18.

Третья группа п триггеров 8.1-S.n предназначена для запоминания импульсов записи инверсных или неинверсных символьных переменных первой символьной конъюнкции, поступающих с выходов группы элементов ИЛИ 7. Таким образом, i-й триггер группы 8 установлен, если 1-я символьная переменная в первой символьной конъюнкции существенна, т.е. имеется, а на выходах групп триггеров и 8 устанавливается код первой символьной конъюнкции, имеющий три комбинации для каждой пары триггеров групп 1 и 8: 11 - символьная переменная неинверсна, 01 символьная переменная инверсна, 00 - символьная переменная отсутствует (несущественна). Код 10 не может быть сформирован. Третья группа триггеров 8.1-8,п может быть реализована на интегральных микросхемах 155ТМ2.

Четвертая группа п триггеров 9.1-Э.п предназначена для запоминания импульсов записи инверсных или неинверсных символьных переменных второй символьной конъюнкции, поступающих с выходов групп элементов ИЛИ 10 аналогично группе триггеров 8. Четвертая группа триггеров 9.1-Э.п также может быть реализована на интегральных микросхемах 155ТМ2.

Вторая группа п элементов ИЛИ 10.1- Ю.п предназначена для установки соответствующих триггеров группы 9 в случае поступления импульсов записи инверсного или неинверсного значения символьной переменной по группам входов 19 и 17 соответственно.

Третья группа п элементов ИЛИ 11.1- 11.п предназначена для формирования сигнала логической единицы в случае наличия на выходах i-x триггеров групп 1 и 2 логической единицы, т.е. неинверсного значения символьной переменной хотя бы в одной из двух символьных конъюнкций для последующего формирования кода символьной конъюнкции двух символьных конъюнкций.

Четвертая группа п элементов ИЛИ 12.1-12.п предназначена для формирования сигнала логической единицы в случае наличия на входах i-x триггеров групп 8 и 9 логической единицы, т.е. инверсного значения символьной конъюнкции хотя бы в одной из двух символьных конъюнкций для последующего формирования кода символьной конъюнкции двух символьных конъюнкций.

Группа п элементов И-НЕ 13.1-13.п предназначена для определения ортогональности символьных существенных переменных по одновременному наличию на выходах одноименных элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, РАВНОЗНАЧНОСТЬ групп

5 и 6 логических единиц, свидетельствующих о том, что символьные переменные существенны (на входах элемента группы 6 логические единицы) и ортогональны (на

входах элемента группы 5 одна логическая единица).

Элемент И 14 предназначен для фиксации факта ортогональности хотя бы в одном одноименном разряде двух символьных

конъюнкций. В этом случае обнуляются выходы элементов И групп 3 и 4.

Первая группа выходов 15.1-15.ri предназначена для выдачи первого разряда кода символьной конъюнкции двух символьных

конъюнкций.

Первая группа входов 16.1-16.П предназначена для приема импульса записи неинверсного значения разрядов первой символьной конъюнкции. Вторая группа

входов 17.1-17.П предназначена для приема импульса записи неинверсного значения разрядов второй символьной конъюнкции. Третья группа входов 18.1- 18.п предназначена для приема импульса

записи инверсного значения разрядов первой символьной конъюнкции. Четвертая группа входов 19.1-19.п предназначена для приема импульса записи инверсного значения разрядов второй символьной конъюнкции.

Вход 20 сброса предназначен для обнуления триггеров групп 1, 2, 8 и 9. Вторая группа выходов 21.1-21.п предназначена для выдачи второго разряда кода символь-.

ной конъюнкции двух символьных конъюнкций.

Устройство для реализации логических функций работает следующим образом. Настройка. В исходном все триггеры обнулены по входу 20. На первую 16.1-16.п и третью 18.1-18.ri группы входов поступают импульсы записи первой символьной конъюнкции. При этом, если на i-й вход группы 16 поступает импульс, то это означает

вхождение i-й переменной в первую конъюнкцию без инверсии; если на i-й вход группы 18 поступает импульс, то это означает вхождение i-й переменной в первую конъюнкцию с инверсией; если импульсы

на i-e входы групп 16 и 18 не поступают, то это означает, что i-я переменная не входит в конъюнкцию.

Импульс установки неинверсного зна- чения символьной переменной в первой конъюнкции устанавливает соответствующий триггер 1.1 первой группы триггеров, а через соответствующий элемент ИЛИ группы 7 устанавливает соответствующий триггер третьей группы триггеров 8.

Импульс установки инверсного значения символьной переменной в первой конъюнкции устанавливает через соответствующий элемент ИЛИ группы 7, соответствующий триггер третьей группы триггеров 8.

Аналогично происходит запись второй символьной конъюнкции. При этом импульсы установки неинверсного значения i-й символьной переменной с i-ro входа второй группы входов 17 устанавливает соответствующий триггер второй группы триггеров 2, а через соответствующий элемент ИЛИ 10 второй группы - соответствующий триггер четвертой группы триггеров 9. Импульс установки инверсного значения символьной переменной во второй конъюнкции устанавливает через соответствующий триггер четвертой группы триггеров 9.

Таким образом на выходах пар триггеров первой 1 и третьей 8 групп устанавливается код первой символьной конъюнкции, где комбинация 11 в i-й паре соответствует неинверсному значению i-й символьной переменной, комбинация 01 в i-й паре соответствует инверсному значению i-й символьной переменной, комбинация 00 соответствует отсутствию i-й символьной переменной в конъюнкции.

Аналогично устанавливаются коды второй символьной конъюнкции на выходах второй 2 и четвертой 9 групп триггеров.

Формирование n-разрядной символьной конъюнкции двух символьных п-разряд- ных конъюнкций.

Результат символьной конъюнкции двух n-разрядных символьных конъюнкций, каждая из которых закодирована 2п-разрядным кодом на выходах групп триггеров 1,8 и 2,9, происходит на первой 15 и второй 21 группах выходах устройства через первую 3 и вторую 4 группу элементов И.

При этом возможны следующие случаи.

В первом случае i-e переменные в первой и второй символьных конъюнкциях имеются (существенны) и имеют различные знаки инверсирования, т.е. первая неинверсная, вторая инверсная или первая инверсная, вторая неинверсная. Тогда результат символьной конъюнкции должен быть нулевым, т.е. получается пустая конъюнкция, не имеющая символьных переменных. На всех выходах 15 и 21 устанавливаются логические нули. Это происходит в случае одновременной фиксации соответствующими элементами ИСКЛЮЧАЮЩЕЕ ИЛИ 5 на выходах соответствующих триггеров 1 и 2 групп комбинаций сигналов 01, 10 и фиксации соответствующими элементами РАВНОЗНАЧНОСТЬ 6 на выходах

соответствующих триггеров 3 и 4 групп комбинации сигналов 11. Тогда на входы соответствующих элементов И-НЕ 13 поступают две логические единицы и на их выходах

устанавливается логический нуль.

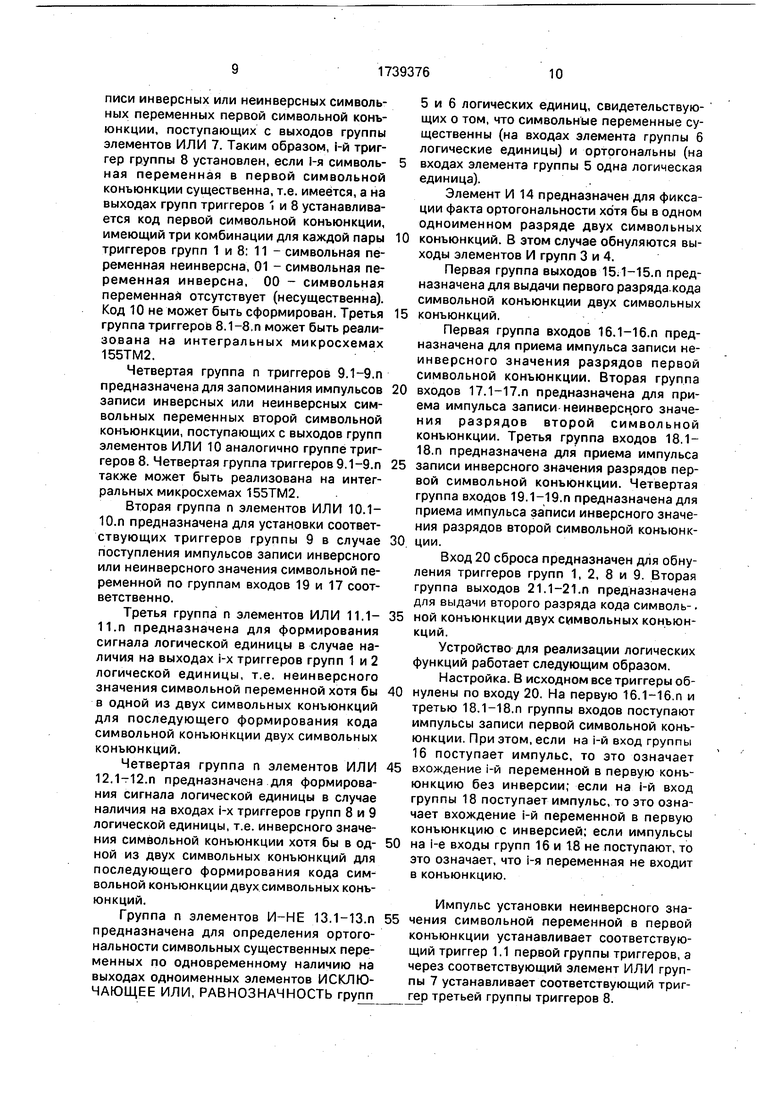

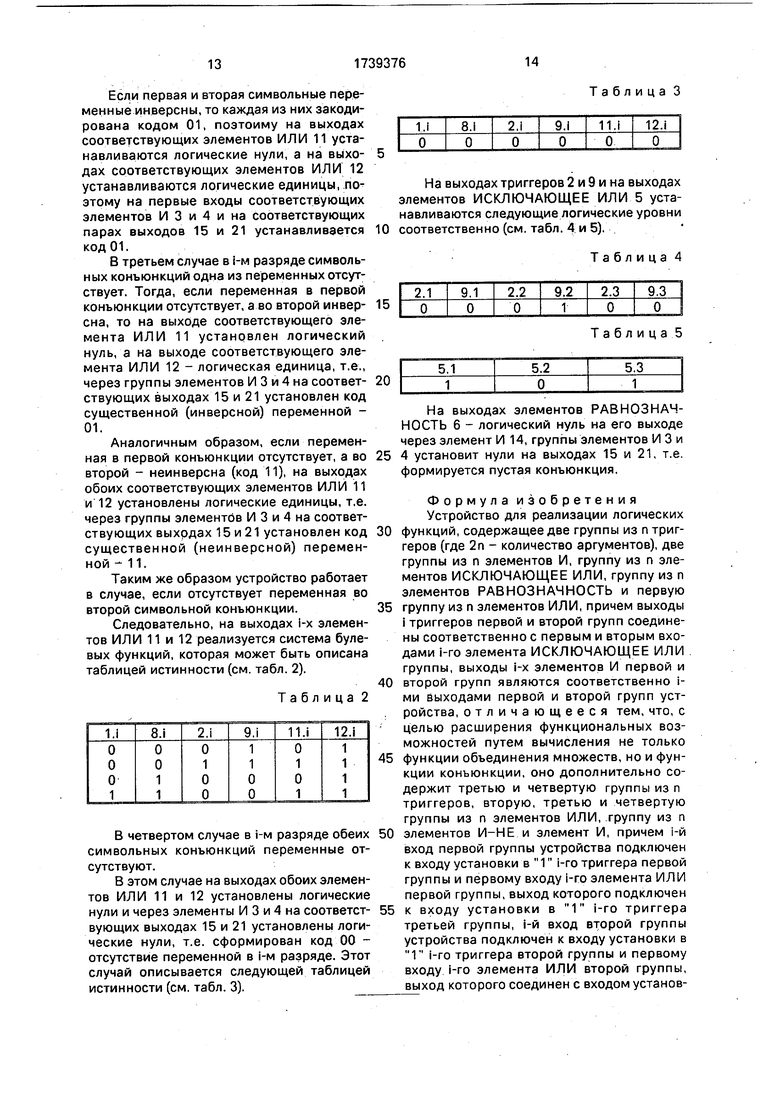

Таким образом, для каждого i-ro разряда символьной конъюнкции двух символьных конъюнкций совокупностью i-x элементов 5, 6 и 13 вычисляется булева функция, описываемая таблицей истинности (см. табл. 1).

Таблица 1

Следовательно, выделяются ситуации наличия различных знаков инверсирования

i-x символьных переменных в двух символьных конъюнкциях. Остальные восемь комбинаций не имеют места в устройстве по условию задания кодов символьных конъюнкций.

Таким образом, если на выходе хотя бы одного элемента И-НЕ 13 имеется логический нуль, то на выходе элемента И 14 также имеется логический нуль, который через элементы И 3 и 4 обнуляет группы выходов

15 и 21, т.е. формируется пустая символьная конъюнкция.

Если на выходах всех элементов И-НЕ 13 установлены логические единицы, то и на выходе элемента И 14 имеется логическая

единица. Тогда на выходах формируется непустая конъюнкция.

Во втором случае i-e переменные в символьных конъюнкциях (существенны) и имеют одинаковые знаки инверсирования, т.,е.

первая инверсная и вторая инверсная или первая неинверсная и вторая неинверсная. В этом случае, как описано на выходе элемента И 14 установлена логическая единица.

Тогда, если первая и вторая символьные переменные неинверсны, то на выходах соответствующих элементов ИЛИ 11 и 12 устанавливаются логические единицы, поступающие на первые входы соответствующих

элементов И 3 и 4 и на соответствующих первых выходов групп 15 и 21 устанавливается код 11, что соответствует символьной конъюнкции двух одноименных неинверсных переменных, каждая из которых закодирована аналогичным кодом.

Если первая и вторая символьные переменные инверсны, то каждая из них закодирована кодом 01, поэтоиму на выходах соответствующих элементов ИЛИ 11 устанавливаются логические нули, а на выходах соответствующих элементов ИЛИ 12 устанавливаются логические единицы, поэтому на первые входы соответствующих элементов И 3 и 4 и на соответствующих парах выходов 15 и 21 устанавливается код 01.

В третьем случае в i-м разряде символьных конъюнкций одна из переменных отсутствует. Тогда, если переменная в первой конъюнкции отсутствует, а во второй инверсна, то на выходе соответствующего элемента ИЛИ 11 установлен логический нуль, а на выходе соответствующего элемента ИЛИ 12 - логическая единица, т.е., через группы элементов И 3 и 4 на соответствующих выходах 15 и 21 установлен код существенной (инверсной) переменной - 01.

Аналогичным образом, если переменная в первой конъюнкции отсутствует, а во второй - неинверсна (код 11), на выходах обоих соответствующих элементов ИЛИ 11 и 12 установлены логические единицы, т.е. через группы элементов И 3 и 4 на соответствующих выхрдах 15 и 21 установлен код существенной (неинверсной) переменной -11.

Таким же образом устройство работает в случае, если отсутствует переменная во второй символьной конъюнкции.

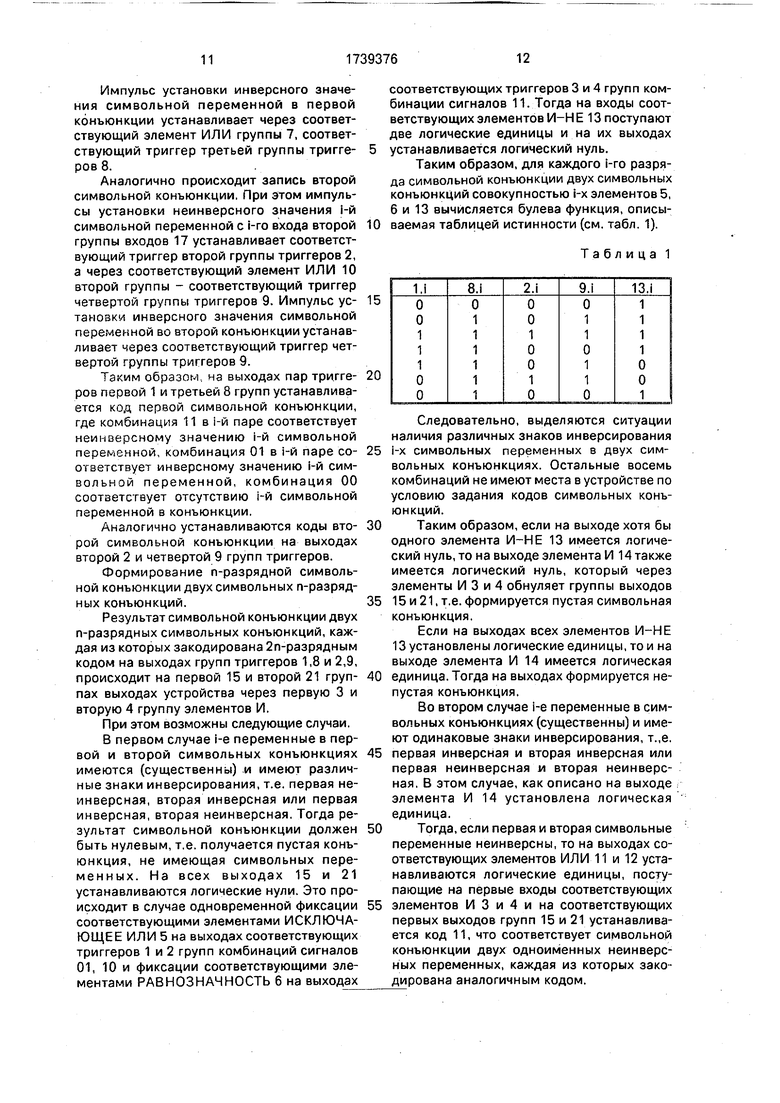

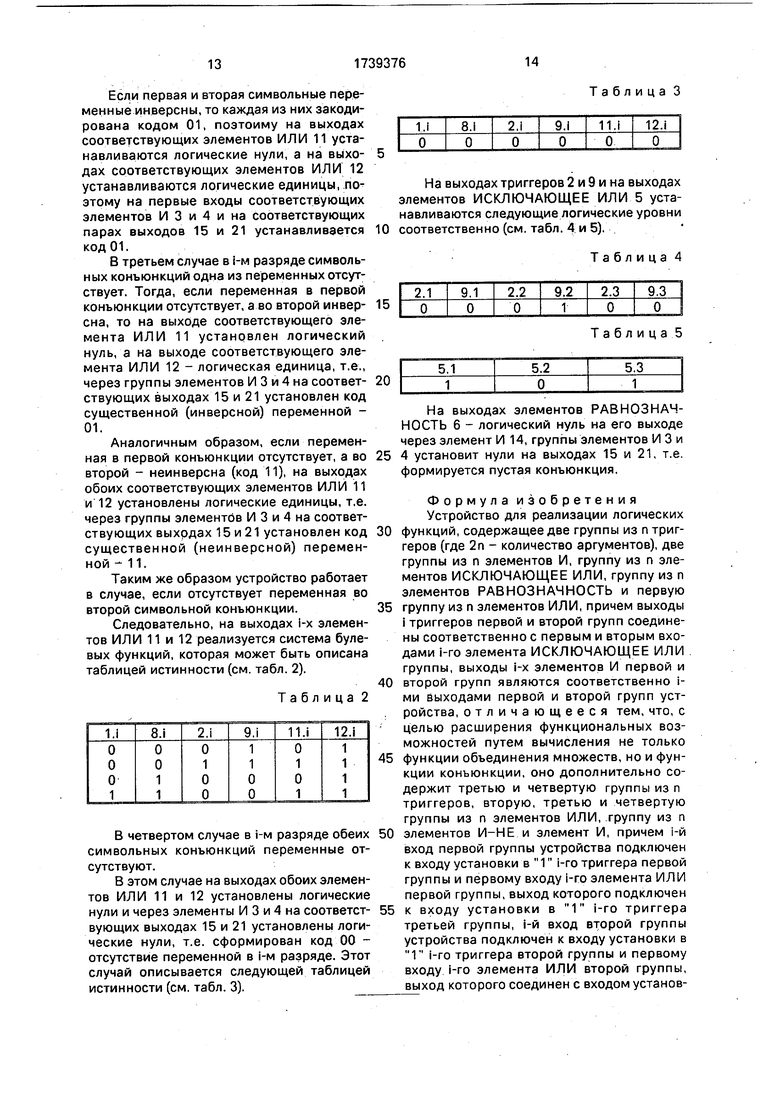

Следовательно, на выходах i-x элементов ИЛИ 11 и 12 реализуется система булевых функций, которая может быть описана таблицей истинности (см. табл. 2).

Таблица 2

В четвертом случае в i-м разряде обеих символьных конъюнкций переменные отсутствуют.

В этом случае на выходах обоих элементов ИЛИ 11 и 12 установлены логические нули и через элементы И 3 и 4 на соответствующих выходах 15 и 21 установлены логические нули, т.е. сформирован код 00 - отсутствие переменной в i-м разряде. Этот случай описывается следующей таблицей истинности (см. табл. 3).

Таблица 3

На выходах триггеров 2 и 9 и на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 5 устанавливаются следующие логические уровни соответственно (см. табл. 4 и 5).

Таблица 4

Таблица 5

На выходах элементов РАВНОЗНАЧНОСТЬ 6 - логический нуль на его выходе через элемент И 14, группы элементов И 3 и 4 установит нули на выходах 15 и 21, т.е. формируется пустая конъюнкция.

Формула изобретения Устройство для реализации логических

функций, содержащее две группы из п триггеров (где 2п - количество аргументов), две группы из п элементов И, группу из п элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, группу из п элементов РАВНОЗНАЧНОСТЬ и первую

группу из п элементов ИЛИ, причем выходы i триггеров первой и второй групп соединены соответственно с первым и вторым входами i-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы, выходы i-x элементов И первой и

второй групп являются соответственно i- ми выходами первой и второй групп устройства, отличающееся тем, что, с целью расширения функциональных возможностей путем вычисления не только

функции объединения множеств, но и функции конъюнкции, оно дополнительно содержит третью и четвертую группы из п триггеров, вторую, третью и четвертую группы из п элементов ИЛИ, группу из п

элементов И-НЕ и элемент И, причем i-й вход первой группы устройства подключен к входу установки в 1 i-ro триггера первой группы и первому входу 1-го элемента ИЛИ первой группы, выход которого подключен

к входу установки в 1 i-ro триггера третьей группы, i-й вход второй группы устройства подключен к входу установки в 1 i-ro триггера второй группы и первому входу i-ro элемента ИЛИ второй группы, выход которого соединен с входом установки в 1 i-ro триггера четвертой группы, i-e входы третьей и четвертой групп устройства подключены к вторым входам i-x элементов ИЛИ соответственно первой и второй групп, вход сброса устройства подключен к входам установки в О всех триггеров с первой по четвертую групп, выходы i-x триггеров первой и второй групп соединены соответственно с первым и вторым входами 1-го элемента ИЛИ третьей группы, выход которого соединен с первым входом i-ro элемента И первой группы, выход 1-го триггера третьей группы соединен с первыми входами 1-го элемента ИЛИ четвертой

0

5

группы и i-ro элемента РАВНОЗНАЧНОСТЬ группы, второй вход которого соединен с выходом i-ro триггера четвертой группы и вторым входом i-ro элемента ИЛИ четвертой группы, выход которого соединен с первым входом i-ro элемента И второй группы, вторые входы элементов И первой и второй групп соединены с выходом элемента И, i-й вход которого соединен с выходом i-ro элемента И-НЕ группы, первый и второй входы которого соединены с выходами соответственно i-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы и i-ro элемента РАВНОЗНАЧНОСТЬ группы.

| Авторское свидетельство СССР Ms 1119373, кл.С 06 F 15/38, 1982 | |||

| Устройство для объединения множеств | 1985 |

|

SU1278890A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-06-07—Публикация

1990-05-08—Подача