Изобретение относится к вычислительной технике и может быть использовало для построения процессоров быстрого преобразования Фурье, цифровых фильтров, вычислительных машин с комплексной арифметикой, решения систем линейных алгебраических уравнений.

Цель изобретения - повышение быст родействпя.

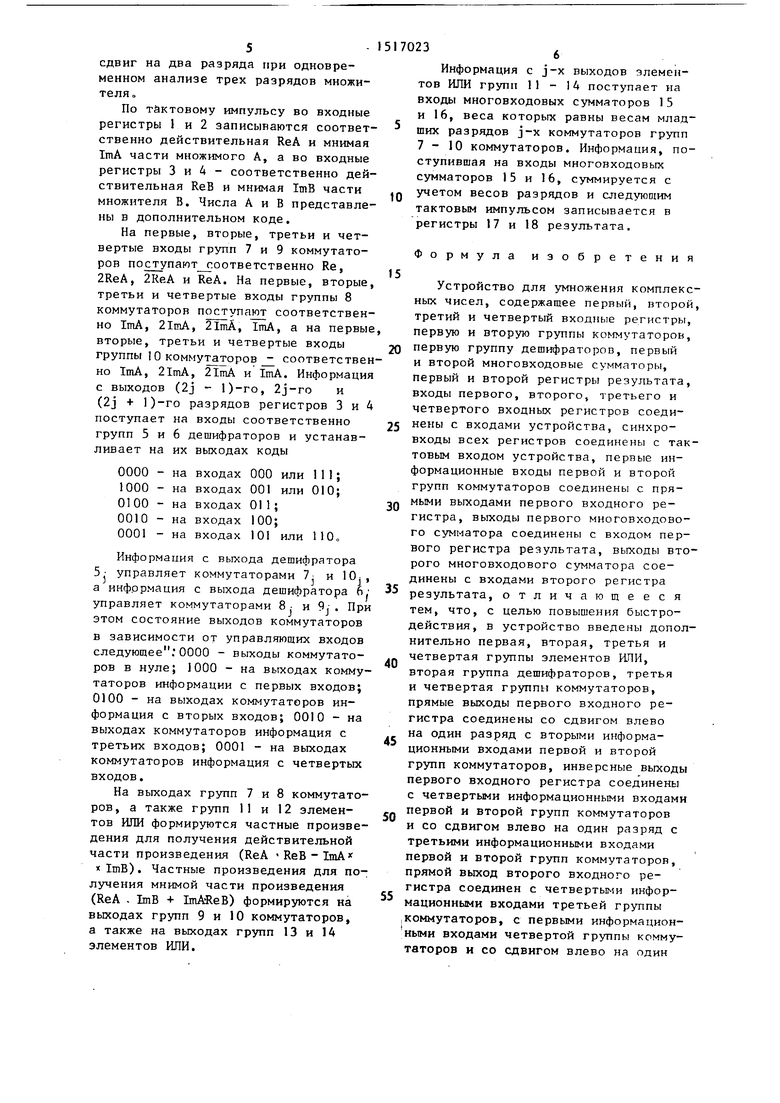

Па чертеже представлена схема устройства.

Устройство содержит пе1:1вый, второй, третий и четвертый входные ре- гистры 1-4, первую и вторую группы 5 и 6 дешифраторов (каждая группа содержит п/2 дешифраторов, где п - разрядность множителя), пе1)вую, вторую, третью и четвертую группы 7 - Ю коммутаторов (каждая группа содержит п/2 коммутаторов), первую, вторую, третью и четвертую группы 11 - 14 элементов ОТИ, содержащие по п/2 элементов miH, первый и второй мпоговхо довые сумматоры 15 и 16, первый и - второй регистры 17 и 18 произведений Коммутаторы групп 7-10 могут быть 1 ыполнепь из паборов по четыре элемента И, объединенных элементом ШИ.

Прямые выходы регистра 1 соединены с первыми информационными входами коммутаторов групп 7 и 9, со сдвигом на один разряд влево с вторыми информащюнньми входами коммутаторов группы 7, инверсные выходы регистра 1 соединены с четвертьми информационными входами коммутаторов групп 7 и 9 и со сдвигом на один разряд влево с третьими информацион- ными входами коммутаторов групп 7 и

9,прямые выходы регистра 2 соединены с четвертыми информационными вхо- дамр коммутаторов группы 8, с первыми информационными входами коммута- торов группы 10 и со сдвигом на

один разряд влево с третьими и вторыми информационными входами соответственно коммутаторов групп 8 и

10,инверсные выходы регистра 2 соединены с первыми информационными входами коммутаторов группы 8, с четвертьми информационными входами коммутаторов группы 10 и со сдвигом на разряд влево с вторыми и третьими информационными входами соответственно коммутаторов групп 8 и 10; первый, второй и третий входы j-ro дешифратора 5j (j 1,..., n/2) сое

Q

о 5 ,,

д

5

0

5

динены соответственно с (2j - 1)-м, 2J-M, (2J + 1)-м выходами регистра 3, (2J - 1)-й, и (2J + )-й выходы регистра 4 соединены соответственно с первым, вторьм и третьим входами j-ro дешифратора 6;, первый, второй, третий и четвертый выходы j-ro дешифратора 5; соединены соответственно с первыми, вторыми, третьими и четвертыми управляющими входами коммутаторов 7.- и 10-, первый, второй, третий и четвертый выходы дешифратора 6- соединены соответственно с первыми, вторыми, третьими и четвертыми входами коммутаторов 8: и 9.-; первые и вторые входы j-x элементов ИЛИ соединены соответственно с третьим и четвертым выходами дешифратора 5, первый и второй вход j-ro элемента ИЛИ 12. соединен соответственно с первым и вторым выходами дешифратора 6-, третий и четвертый выходы которого соединены соответственно с первым и вторым входами j-ro элемента ИЛИ группы 13; выход коммутатора 7j соединен со сдвигом вправо на (2j - 2) разрядов с J-M входом многовходового сумматора 15, (п/2 + j)-й вход которого соединен со сдвигом на (2J - /О разрядов вправо с выходом коммутатора 8;, выход коммутатора 9; соединен со сдвигом вправо на (2J - 2) разрядов с J-M входом многовходового сумматора 16, (п/2 + j)-й вход которого соединен со сдвигом на (2j - 2) разрядов вправо с выходом коммутатора 10:, выход элемента ИЛИ 11j соединен с (п + j)-M входом многовходового сумматора 15, (п + п/2 + j)-й вход которого соединен с выходом элемента ИЛИ группы 12, выход J-ro элемента ИЛИ группы 13 соединен с (п + j)-M входом многовходового сумматора 16, (п + п/2 + j)-й вход которого соединен с выходом элемента ИЛИ 14j, выход многовходового сумматора 15 соединен с входом регистра 17, вход регистра 18 соединен с выходом многовходового сумматора 16.

Устройство работает следующим образом.

Формирование частных произведений в устройстве производится по модифицированному алгоритму Бута, который предусматривает постоянный

сдвиг на два разряда при одновременном анализе трех разрядов множителя

По тактовому импульсу во входные регистры 1 и 2 записываются соответственно действительная ReA и мнимая ImA части множимого А, а во входные регистры 3 и 4 - соответственно действительная ReB и мнимая ImB части множителя В, Числа А и В представлены в дополнительном коде.

На первые, вторые, третьи и четвертые входы групп 7 и 9 коммутаторов поступают соответственно Re, 2ReA, 2ReA и ReA. На первые, вторые, третьи и четвертые входы группы 8 коммутаторов поступают соответственно ImA, 2ImA, 21mA., ImA, a на первые вторые, третьи и четвертые входы группы IО коммутаторов соответственно 1шА, 2lmA, 2ImA и ImA. Информация с выходов (2J - 1)-го, 2j-ro и (2J + 1)-го разрядов регистров 3 и 4 поступает на входы соответственно групп 5 и 6 дешифраторов и устанавливает на их выходах коды

0000- на входах 000 или 111; 1000 - на входах 001 или 010; 0100 - на входах 011;

0010 - на входах 100;

0001- на входах 101 или 110„

Информация с выхода дешифратора 5- управляет коммутаторами 7: и 10;, а информация с выхода дешифратора 6 управляет кo fмyтaтopaми 8 и 9j . При этом состояние выходов коммутаторов в зависимости от управляющих входов следующее 0000 - выходы коммутаторов в нуле; 1000 - на выходах коммутаторов информации с первых входов; 0100 - на выходах коммутаторов информация с вторых входов; 0010 - на выходах коммутаторов информация с третьих входов; 0001 - на выходах коммутаторов информация с четвертых входов.

На выходах групп 7 и 8 коммутаторов, а также групп 11 и 12 элементов ИЛИ формируются частные произведения для получения действительной части произведения (ReA «ReB-ImAf кImB). Частные произведения для получения мнимой части произведения (ReA - ImB + ЬпАЖеВ) формируются на выходах групп 9 и 10 коммутаторов, а также на выходах групп 13 и 14 элементов ИЛИ.

0

5

0

5

0

5

0

5

Информация с J-X выходов элементов ИЛИ групп 11 - 14 поступает на входы многовходовых сумматоров 15 и 16, веса которых равны весам младших разрядов J-X коммутаторов групп 7-10 коммутаторов. Информация, поступившая на входы многовходовых сумматоров 15 и 16, суммируется с учетом весов разрядов и следуюпгим тактовым импульсом записывается в регистры 17 и 18 результата.

Формула изобретения

Устройство для умножения комплексных чисел, содержащее первый, второй, третий и четвертый входные регистры, первую и вторую группы коммутаторов, первую группу дешифраторов, первый и второй многовходовые сумматоры, первый и второй регистры результата, входы первого, второго, третьего и четвертого входных регистров соединены с входами устройства, синхро- входы всех регистров соединены с тактовым входом устройства, первые информационные входы первой и второй групп коммутаторов соединены с прямыми выходами первого входного регистра, выходы первого многовходово- го сумматора соединены с входом первого регистра результата, выходы второго многовходового сумматора соединены с входами второго регистра результата, отличающееся тем, что, с целью повышения быстродействия, в устройство введены дополнительно первая, вторая, третья и четвертая группы элементов ИЛИ, вторая группа дешифраторов, третья и четвертая группи коммутаторов, прямые выходы первого входного регистра соединены со сдвигом влево на один разряд с вторыми информационными входами первой и второй групп коммутаторов, инверсные выходы первого входного регистра соединены с четвертыми информационными входами первой и второй групп коммутаторов и со сдвигом влево на один разряд с третьими информационными входами первой и второй групп коммутаторов, прямой вьиод второго входного регистра соединен с четвертыми информационными входами третьей группы коммутаторов, с первыми информационными входами четвертой группы коммутаторов и со сдвигом влево на один

разряд с третьими и вторыми информационными входами соответст1зенио третьей и 1етпертой групп KONiMyTHTopoB, инверсные выходы второго входного регистра соединены с первыми инфор- мацноит1ыми входами третьей группы коммутаторов, с четвертыми информационными входами четвертой группы коммутаторов и со сдвигом влево на один разряд с вторыми и третьими информационными входами соответс венно третьей и четвертой групп коммутаторов, первый, второй и третий входы каждого j-ro дешифратора (j 1,..,, п/2, где п - разрядиостгГ операндов) пер- noi i группы соединены соответственно с (2J - 1)-м, 2J-M и (2J + 1)-м выходами разрядов третьего входного регистра, первый, второй и третий пхоцы j-ro дешифратора второй группы соединены соответственно с (2j - 1)2J-M и (2J + 1)-м выходами разрядов четвертого входного регистра, первый, второй, трети11 и четвертый выходы J-го дешифратора первой группы соединены соответственно с первыми, вторыми, третьими и четвертыми управ ляюиитми входами j-х коммутаторов первой и четвертой групп коммутаторов, первый, второй, третий и четвер тьт выходы j-ro деши(1)ратора второй группы дешифраторов соединены соответственно с первыми, вторьЕ-П1, третьими и -четвертыми управляющими входами j-X коммутаторов второй и третьей групп коммутаторов, первые и вторые входы j-x элемептов ИЛИ перво и четвертой групп элементов 1ШИ сое- соответственно с третьим и

0

5

0

5

O

5

0

четвертым выходами j-ro дешифратора первой группы дешифраторов, первый и второй входы j-ro элемента ИЛИ второй группы элементов ИЛИ соединены соответственно с первым и вторым выходами j-ro дешифратора второй группы, третий и четвертый выходы которого соединены соответственно с первым и вторым входами j-ro элемента ИЛИ третьей группы элементов ИЛИ, выход j-ro коммутатора первой группы коммутаторов соединен со сдвигом вправо на (2J - 2) разрядов с j-м входом первого многовходового сумматора, выход j-ro коммутатора третьей группы соединен со сдвигом вправо на (2J - 2) разрядов с (п/2 J)-M входом первого многовходового сумматора, выход j-ro коммутатора второй группы соединен со сдвигом вправо на (2J - 2) разрядов с j-м входом второго многовходового сумматора, выход j-ro коммутатора четвертой группы коммутаторов соединен со сдвигом вправо на (2j - 2) разрядов с (п/2 + j)-M входом второго многовходового сумматора, выход j-ro элемента -ШИ первой группы элемептов ИЛИ соединен с (п + J)-M входом первого многовходового сумматора, (п + п/2 + + j)-й вход которого соединен с выходом j-ro элемента ИЛИ второй группы элементов ИЛИ, выход j-ro элемента ИЛИ третьей rpynni)i элементов ИЛИ соединен с (п + J)-M входом второго многовходового сумматора, (п + п/2 + + j)-й вход которого соединен с выходом j-ro элемента ИЛИ четвертой группы элементов ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения комплексных чисел | 1985 |

|

SU1297034A1 |

| Устройство для умножения комплексных чисел | 1986 |

|

SU1388851A1 |

| Устройство для сортировки чисел | 1988 |

|

SU1564611A1 |

| Устройство для умножения комплексных чисел | 1981 |

|

SU1103222A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1619300A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1984 |

|

SU1242986A1 |

| Устройство для поворота вектора | 1983 |

|

SU1144104A1 |

| Арифметическое устройство | 1982 |

|

SU1089577A1 |

| Устройство для быстрого преобразования Фурье | 1981 |

|

SU1078433A1 |

| Арифметическое устройство для быстрого преобразования Фурье | 1986 |

|

SU1383394A2 |

Изобретение относится к вычислительной технике и может быть использовано для построения процессоров быстрого преобразования Фурье, цифровых фильтров, вычислительных машин с комплексной арифметикой. Цель изобретения - повышение быстродействия. Для достижения поставленной цели в состав устройства входят шесть регистров 1-4, 17, 18, четыре группы 7-10 коммутаторов, четыре группы 11-14 элементов ИЛИ, две группы 5, 6 дешифраторов, два многовходовых сумматора 15, 16. Повышение быстродействия достигается за счет уменьшения времени на формирование частных произведений. 1 ил.

| Семотюк М.В., Богон ВоП | |||

| Операционные устройства для суммирования парных произведений и умножения комплексных чисел о - Управляющие системы и машины, 1978, № 3, с | |||

| Пожарный двухцилиндровый насос | 0 |

|

SU90A1 |

| Устройство для умножения комплексных чисел | 1981 |

|

SU1103222A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-10-23—Публикация

1987-10-19—Подача