выходом I -го триггера блока управления , выход генератора тактовых импульсов соединен со счетным входом сдвигового регистра блока управления и с установочными входами триггеров и регистров каящой ячейки, разрядные выходы первого и второго регистров (i+l)-H ячейки соединены с первыми информационными входами соответственно первого и второго коммутаторов (+1)-й ячейки, вторые информационные входы которых соединены с единичными выходами соответственно первого и второго триггеров (i +1)-й ячейки, единичные входы которых соединены с информационными входами соответственно первого и второго регистров (1+1)-й ячейки, знаковые входы первого и второго сумматоров-вычитателей 1-и ячейки соединены с t-м входом группы входов направления поворота устройства, первый и второй информационные выходы которого соединены с информационными выходами соответственно первого и второго сумматороввычитателей И -и ячейки, выход генератора тактовых импульсов блока управления соединен с установочными входами сдвигового регистра блока управления и с управляющим входом запуска устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

| Арифметическое устройство | 1982 |

|

SU1089577A1 |

| Вычислительное устройство | 1983 |

|

SU1167604A1 |

| Вычислительное устройство для поворота вектора | 1982 |

|

SU1109742A1 |

| Устройство для вычисления функции @ = @ | 1982 |

|

SU1062693A1 |

| Вычислительное устройство | 1986 |

|

SU1361546A1 |

| Вычислительное устройство | 1981 |

|

SU1136147A1 |

| Вычислительное устройство | 1988 |

|

SU1522196A1 |

| Устройство для преобразованияКООРдиНАТ | 1979 |

|

SU836636A1 |

| Функциональный преобразователь | 1983 |

|

SU1136154A1 |

УСТРОЙСТВО ДЛЯ ПОВОРОТА ВЕКТОРА, содержащее генератор тактовых импульсов, И ячеек (где п- разрядность устройства) ка.ждая из которых, начиная с второй, содержит первый и второй регистры, первый и второй сумматоры-вычитатели, первый и второй коммутаторы, а первая ячейка содержит первый и второй сумматоры-вычитатели и первый и второй регистр, причем в каждой ячейке, начиная с второй, разрядные выходы первого и второго регистров соединены с первыми информационными входами соответственно первого и второго сумматоров-вычитателей, выходы первого и второго коммутаторов соединены с вторыми информационньми входами соответственно второго и первого сумматороввьгчитателей, а информационные выхода первого и второго сумматоров-вычитателей (-и ячейки

.Изобретение относится к вычислительной технике и предназначено для использования в специализированных вычислительных системах для выполнения операции поворота вектора,

Известны устройства, выполняюи(ие преобразования координат вектора при его повороте на угол ( по алгоритму Волдера LlJ .

Недостатком устройства является низкое быстродействие, так как каждое новое данное можно начать обрабатывать только после того, как закончена обработка предыдущего.

Наиболее близким по технической сущности к изобретению является вычислительное устройство для реализации алгоритма Волдера, содержащее п ячеек, каждая из которых содержит три регистра, три коммутатора и три сумматора. Известное устройство реализует алгоритм Во.пдера по конвейерному принципу, причем в каждой ячейке s являющейся ступенью конвейера, вьтолняется одна итерация алгоритма Скорость выполнения операции поворота вектора в устройстве равна

Т, (icм рт , где t , И - задержка информации

в коммутаторе и сумматоре.;

-рг - время записи информации в регистр,

.Так как, в устройстве производится па раллельная обработка даннь х, то о

M tirM+n cM + tpr .

Затраты оборудования на устройство составляют

W, (3nV +(ЗпЪ,+(3, ),м, где первое слагаемое - количество триггеров, второе - одноразрядных суг 1маторов, третье - одноразрядных коммутаторов zj ,

Недостаток устройства - большие затраты оборудования.

Цель изобретения - сокращение затрат оборудования,

Поставледная цель достигается тем что в устройство, содержащее генератор тактовых импульсов, п ячеек ( 2, ..,, п, где П - разрядность устройства) каждая из которых, начиная с второй, содержит первый и второй регистры, первый и второй сумматорывычитатели, первый и второй коммутаторы, а первая ячейка содержит первый и второй сумматоры-вьгчитатели и первый и второй регистр, причем в каждой ячейке, начиная с второй, разрядные выходы первого и второго регистров соединены с первыми информационными входами соответственно первого и второго сумматоров-вычитателей, выходы первого и второго коммутаторов соединены с вторыми информационными входами соответственно второго и первого сумматоров-вычитате31144

лей, а информационные выходы первого и второго сумматоров-вычитателей i-й ячейки (, ..., п ) соединены с информационными входами соответственно первого и второго регистров (i + 1)-ri 5 ячейки, дополнительно введен блок управления, содержащий генератор тактовых импульсов, сдвиговый регистр п-1 элементов И, (и-1) триггеров, в бло-ке управления первые входы i-ro и }0 ()-гo элементов И соединены с выходом ()-ro разряда сдвигового регистра, второй вход i-ro элемента И соединен с выходом И-го разряда сдвигового рег1у;тра, в каждую ячейку is устройства, начиная с второй, допол- нительно введены первый, второй, третий и четвертый триггеры, а первая ячейка содержит первый и второй триггеры, причем информационные входы 20 первого и второго регистров первой

ячейки соединены соответственно с первым и вторым информационными входами устройства, единичные входы первого и второго триггеров (1-ь1)-й 25 ячейки соединены с третьими информационными входами соответственно первого и второго сумматоров-вычитателей (1+1)-й ячейки, выходы переносов которых соединены с единичными входа-зо ми соответственно первого и второго триггеров этой ячейки, разрядные выходы первого и второго регистров первой ячейки соединены соответственно . с первыми и вторыми информационными j, входами первого и второго сумматороввычитателей первой ячейки, установочные входы первого и второго триггеров i-й ячейки соединены с инверсным выходом (i-1-l ) . i/2J-ro разряда сдви- 40 гового регистра блока управления, выход t(i+1) 1/2 -1-разряда сдвигового регистра блока управления соединен с установочными входами третьего и четвертого триггеров (i+O-й 45 ячейки, управляющие входы первого и второго коммутаторов (1-н1)-й ячейки соединены с единичным в кодом i-ro

триггера блока управления, выход генератора тактовых импульсов соединен 50 со счетным входом сдвигового регистра блока управления и с установочными входами триггеров и регистров каждой ячейки, разрядные выходы первого и второго регистров (1-ь1)-й ячейки 55 соединены с первыми информационными входами соответственно первого и второго коммутаторов (i+1)-й ячейки; ,

104

вторые информационные входы которых соединены с единичными выходами соответственно первого и второго триггеров (1-н1)-й ячейки, единичные входы которых соединены с информационными входами соответственно первого и второго регистров ()-й ячейки, знаковые входы первого и второго- сумматоров-вычитателей i-й ячейки соединены с i-M входом группы входов направления поворота устройства, первый и второй информационные выходы которого соединены с информационнымИвыходами сеотв.етственно первого и. второго сумматоров-вычитателей ячейки,выход генератора тактовых импульсов блока управления соединен с установочными входами сдвигового регистра блока управления и с управляющим входом запуска устройства.

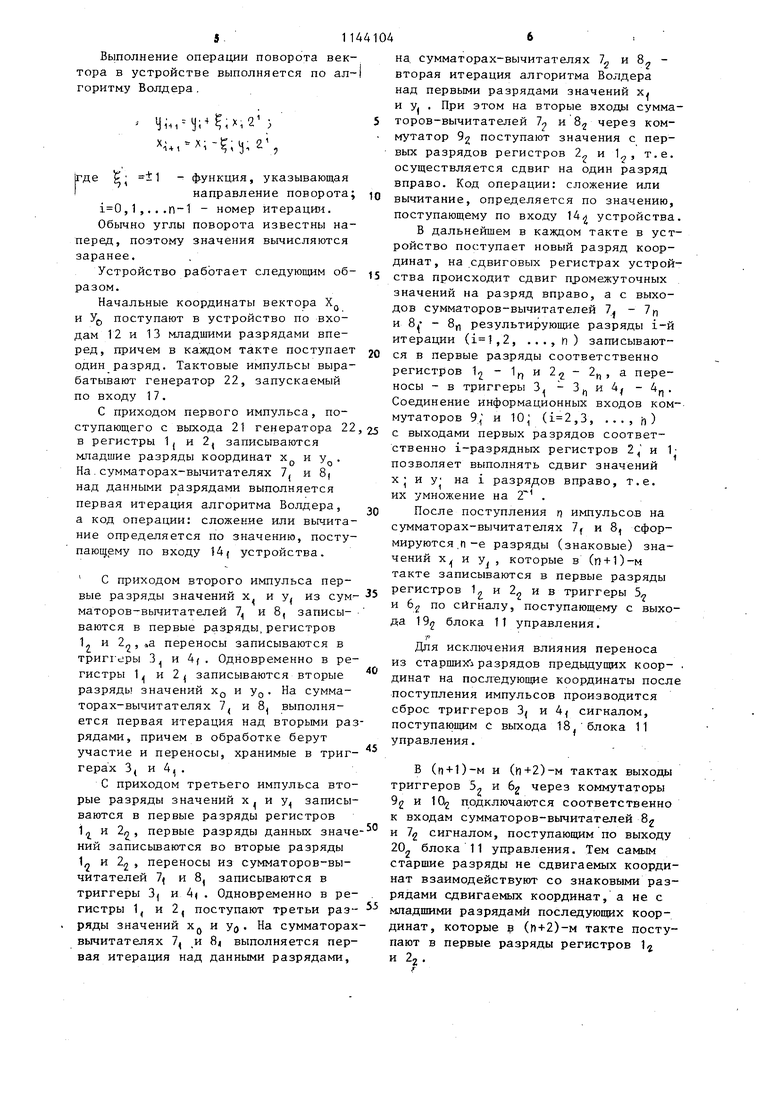

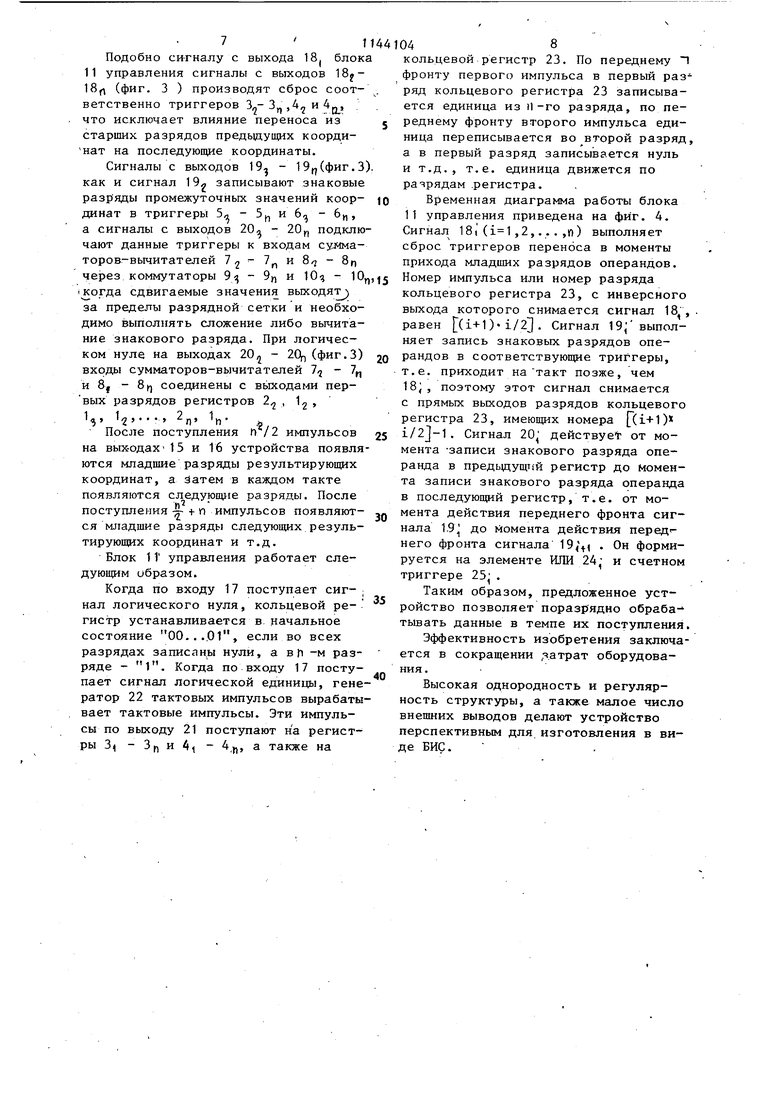

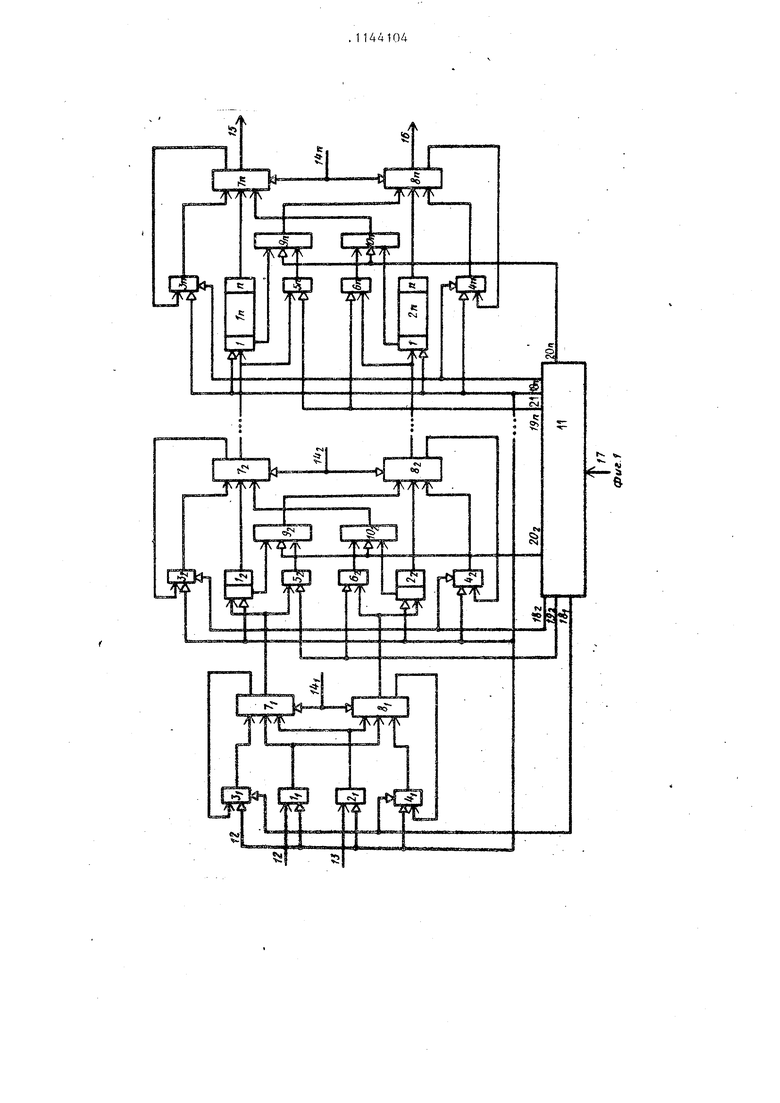

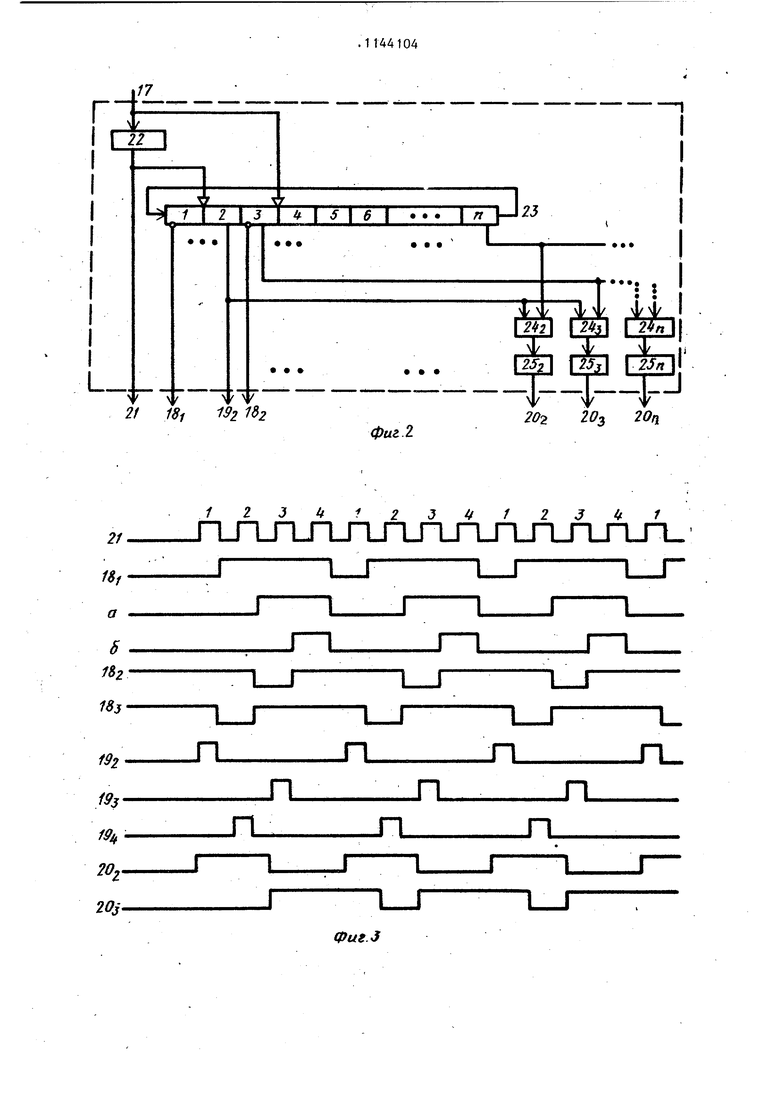

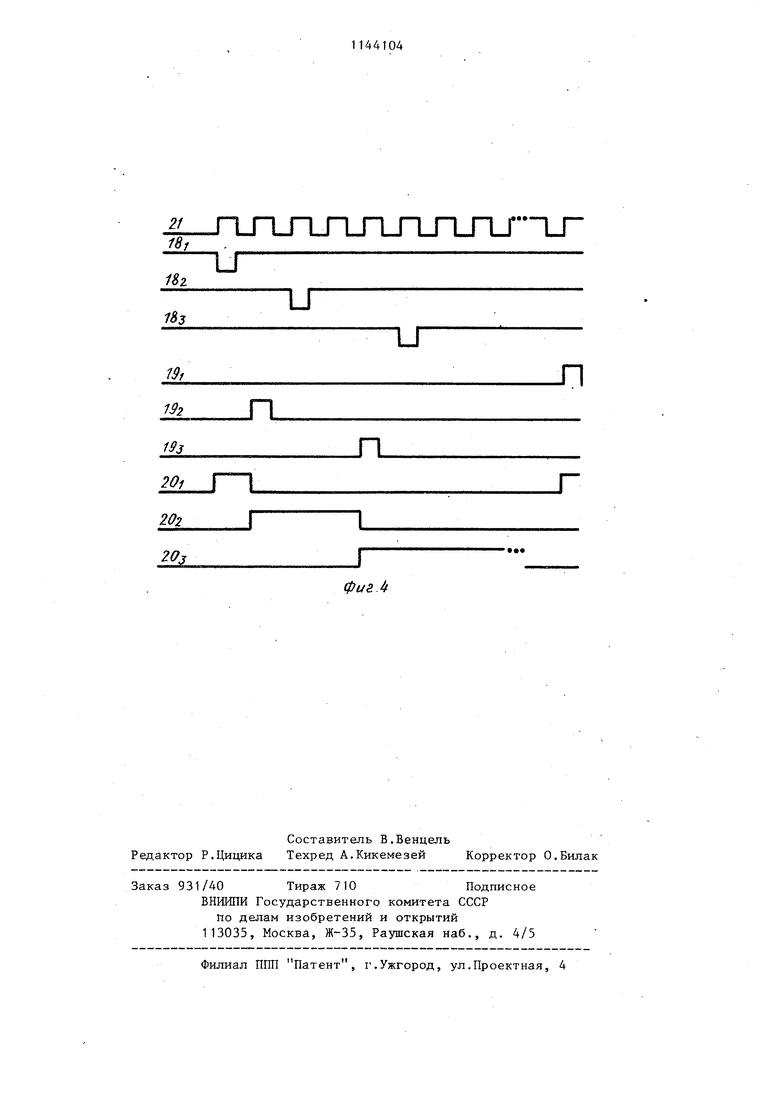

На фиг. 1 показана функциональная схема,устройства поворота вектора; на фиг. 2 - функциональная схема блока управления; на фиг. 3 - временная диаграмма работы устройства для поворота вектора; на фиг. 4 - временная

диаграмма работы блока управления.

. I

Устройство (фиг. 1) содержит первые сдвиговые регистры 1, - 1, вторые сдвиговые регистры 2 - 2, первые триггеры 3, - 3„ , вторы,е триггеры 4 ;| - п, третьи триггеры 5 - 5, четвертые триггеры 6 - 6,, первые сумматоры-вычитатели 7. - 7,, вторые сумматоры-вычитатели 8, 8f,, первые коммутаторы 9 - 9, вторые коммутаторы 10 - lOj, блок 11 управления, первый 12 и второй 13 информационные входы устройства, управляющие входы 1 устройства, первый. 15 и второй 16 информационные входы устройства, управляющий вход 17 запуска устройства, первую группу выходов 18,- 18 блока управления, вторую группу выходов 19 - 19 блока управления , третью группу выходов 20 - 20 блока управления, установочный выход 21 блока управления. Блок 11 управления (фиг. 2) содержит генератор 22 тактовых импульсов, сдвиговый регистр 23, элементы И 24 - 24„, триггеры .

Регистры - 1„ и 2, - 2 - соответственно 1, 2, 3, ...,п - разрядные (л - разрядность устройства). Сумматоры-вычитатели и коммутаторы одноразрядные. i11 Выполнение операции поворота вектора в устройстве выполняется по алгоритму Волдера. . lj, ,2 ) х,,;(, 2, |где ± 1 - функция, указывающая направление поворота ,1,... - номер итерации. Обычно углы поворота известны наперед, поэтому значения вычисляются заранее. Устройство работает следующим образом. Начальные координаты вектора Х и Ур поступают в устройство по входам 12 и 13 младшими разрядами вперед, причем в каждом такте поступает один разряд. Тактовые импульсы вырабатывают генератор 22, запускаемый по входу 17. С приходом первого импульса, поступающего с выхода 21 генератора 2 в регистры 1j и 2 записываются младшие разряды координат х и у . На.сумматорах-вычитателях 7, и 8( над данными разрядами выполняется первая итерация алгоритма Волдера, а код операции: сложение или вычита ние определяется по значению, посту пающему по входу 14J устройства. С приходом второго импульса первые разряды значений х и у из сум маторов-вычитателей 7 и 8, записываются в первые разряды,регистров 1. и 2„, а переносы записываются в триггеры 3 и 4f . Одновременно в регистры 1 и 2 записываются вторые разряды значений XQ и у,.,. На сумматорах-вычитателях 7 и 8 выполняется первая итерация над вторыми раз рядами, причем в обработке берут участие и переносы, хранимые в триггерах 3j и 4 . С приходом третьего импульса вторые разряды значений х и у записываются в первые разряды регистров 1 и 2, первые разряды данных значе НИИ записьшаются во вторые разряды „ и 22, переносы из сумматоров-вы читателей 7( и 8, записываются в триггеры 3, и 4( . Одновременно в регистры 1, и 2, поступают третьи разряды значений х и уд . На сумматорах вычитателях 7 и 8| выполняется первая итерация над данными разрядами, на. сумматорах-вычитателях 7 и 8 вторая итерация алгоритма Волдера над первыми разрядами значений х и у. . При этом на вторые входы сумматоров-вычитателей 7о и 8 через коммутатор 9 поступают значения с первых разрядов регистров 2 и 1, т.е. осуществляется сдвиг на один разряд вправо. Код операции: сложение или вычитание, определяется по значению, поступающему по входу 14 устройства. В дальнейшем в каждом такте в устройство пос;тупает новый разряд координат, на сдвиговых регистрах устройства происходит сдвиг промежуточных значений на разряд вправо, а с выходов сумматоров-вычитателей 7j - 7f) и 8/ - 8fl результирующие разряды i-й итерации (,2, ...,п) записываются в первые разряды соответственно регистров 12 - 1п и 2 - 2f, , а переносы - в триггеры 3. - 3 и 4| п Соединение информационных входов коммутаторов 9, и (,3, ..., h) с выходами первых разрядов соответственно 1-разрядных регистров и 1позволяет выполнять сдвиг значений Xj и у на 1 разрядов вправо, т.е. их умножение на . После поступления п импульсов на сумматорах-вычитателях 7f и 8, сформируются,п-е разряды (знаковые) значений х и у , которые в (п + 1)-м такте записываются в первые разряды регистров 1 и 2 и в триггеры 5 и 6 по сигналу, поступающему с выхода 19 блока 11 управления. Дпя исключения влияния переноса из старших разрядов предьщущих коор- . динат на последующие координаты после поступления импульсов производится сброс триггеров 3 и 4 сигналом, поступающим с выхода 18 блока 11 управления. В ((1 + 1)-м и (|1+2)-м тактах выходы триггеров 5у и 6 через коммутаторы 9 и 102 подключаются соответственно к входам сумматоров-вычитателей 8 и 7 сигналом, поступающим по выходу 20- блока 11 управления. Тем самым старшие разряды не сдвигаемых координат взаимодействуют со знаковыми разрядами сдвигаемых координат, а не с младшими разрядами последующих координат, которые в (Г)+2)-м такте поступают в первые разряды регистров Ц и 22. 7 t Подобно си-гналу с выхода 18( блок 11 управления сигналы с выходов (фиг. 3 ) производят сброс соответственно триггеров 3„-3 ,4, и 4, что исключает влияние переноса из старших разрядов предьщущих координат на последующие координаты. Сигналы с выходов 19 - 19,(фиг.З как и сигнал 19л записывают знаковые разряды промежуточных значений координат в триггеры 5,, - 5, и 6 - 6,, а сигналы с выходов 20 - 20 подклю чают данные триггеры к входам сумматоров-вычитателей 72 7 и 8/2 - 8п через коммутаторы Э-ц - 9 и 10 - Ю i когда сдвигаемые значения выходят) за пределы разрядной сетки и необходимо выполнять сложение либо вычитание знакового разряда. При логическом нуле на выходах 20 - 2С(фиг.З) входы сумматоров-вычитатепей 7 - 7, и 8, - 8fj соединены с вькодами первых разрядов регистров 2 , 1, 1,, 1-2,. . . , 2, 1j,. После поступления П /2 импульсов на вых-одах15 и 16 устройства появля ются младшие разряды результирующих координат, а Аатем в каждом такте появляются следующие разряды. После поступления -5- f п импульсов появляются младшие разряды следующих результирующих координат и т.д. Блок 11 управления работает следующим образом. Когда по входу 17 поступает сигнал логического нуля, кольцевой ре гистр устанавливается в начальное состояние 00....01, если во всех разрядах записаны нули, а вп -м разряде - 1. Когда по входу 17 поступает сигнал логической единицы, гене ратор 22 тактовых импульсов вырабаты вает тактовые импульсы. Эти импульсы по выходу 21 поступают на регистры 3 - 3 и 4 - 4,1,, а также на 48 кольцевой регистр 23. По переднему 1 фронту первого импульса в первый разряд кольцевого регистра 23 записывается единица из П-го разряда, по переднему фронту второго импульса единица переписывается во второй разряд, а в первый разряд записывается нуль и т.д., т.е. единица движется по разрядам .регистра. Временная диаграмма работы блока 11 управления приведена на фиг. 4. Сигнал 18i(,2,...,п) выполняет сброс триггеров переноса в моменты прихода младших разрядов операндов. Номер импульса или номер разряда кольцевого регистра 23, с инверсного выхода которого снимается сигнал , . равен (i+1)i/2. Сигнал 19j выполняет запись знаковых разрядов операндов в соответствующие триггеры, т.е. приходит на такт позже, чем 18j, поэтому этот сигнал снимается с прямых вьпсодов разрядов кольцевого регистра 23, имеющих номера (i+1)x i/2J-1 . Сигнал действует от момента -записи знакового разряда операнда в предьщущтш регистр до момента записи знакового разряда операнда в последующий регистр, т.е. от момента действия переднего фронта сигнала 1.9 до йомента действия перед него фронта сигнала 19) . Он формируется на элементе ИЛИ 24, и счетном триггере 25 . Таким образом, предложенное устройство позволяет поразрядно обраба- тьшать данные в темпе их поступления. Эффективность изобретения заключается в сокращении датрат оборудования. Высокая однородность и регулярность структуры, а также малое число внешних выводов делают устройство перспективным для изготовления в виде БИС.

Фиг.

L«JTJTJTJTJ LJlJnJlJ n

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Банков В.Д | |||

| и др | |||

| Аппаратурная реализация элементарных функций в ЦВМ | |||

| Л., 1975, с | |||

| Приспособление для получения кинематографических стерео снимков | 1919 |

|

SU67A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Вычислительное устройство дляРЕАлизАции АлгОРиТМА ВОлдЕРА | 1979 |

|

SU813423A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-03-07—Публикация

1983-03-22—Подача