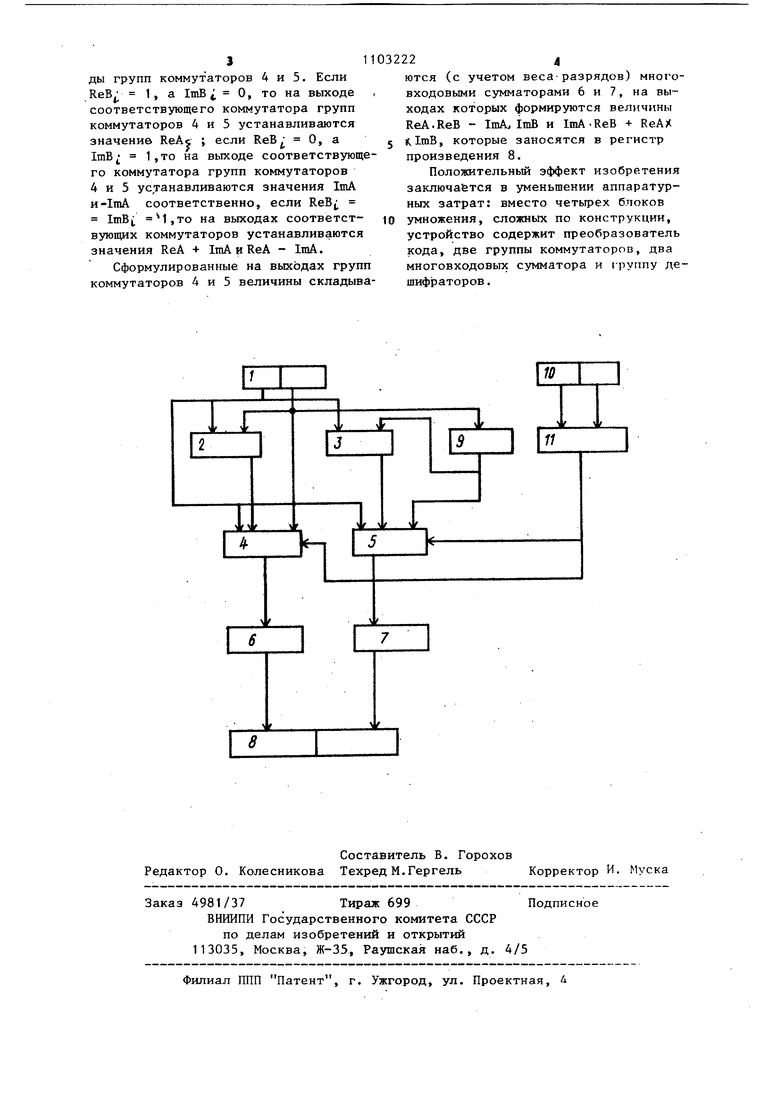

«1 Изобретение относится к вычислительной технике и может быть использовано для построения процессоров быстрого преобразования Фурье, цифровых фильтров, вычислительных машин с комплексной арифметикой, решения систем линейных алгебраических уравнений. Известно устройство умножения, со держащее накапливаюпшй сумматор, регистры множимого и множителя, группу элементов И lj . Недостатком этого устройства явля ется низкое быстродействие. Известно устройство для умножения комплексных чисел, содержащее регист множимого, регистр множителя, регист произведения, первьй, второй, третий и четвертый блоки умножения, сумматор и вычислитель, причем первая группа входов регистра множимого соединена с первыми группами входов первого и второго блока умножения, выходы которого соединены с первыми группами входов вы числителя и сумматора соответственно выходы которых соединены с первой и второй группами входов регистра произведения соответственно, вторая группа выходов регистра множимого со единена с первыми группами входов третьего и четвертого блоков умножения, выходы которых соединены с вторыми группами входов вычитателя и сумматора соответственно, первая гру па выходов регистра множителя соединена с вторыми группами входов первого и четвертого блоков умножения, вторая группа выходов регистра множителя со единена с вторыми группами входов второго и третьего блоков умножения 2 . Недостатком этого устройства является большой объем аппаратурных затрат, так как оно содержит четыре блока умножения, Цель изобретения - упрощение устройства. Поставленная Цель достигается тем, что устройство для умножения комплексных чисел,содержащее регистр множимого, регистр множителя, регистр произведения и первьй сумматор, содержит преобразователь прямого кода в дополнительный, второй сумматор, группу дешифраторов, первую и вторую группу коммутаторов, первьй и второй многовходовые сумматоры, причем первая группа выходов регистра множимо2го соединена с первыми группами входов первого и второго сумматоров и первыми группами информационных входов коммутаторов первой и второй групп, вторая группа выходов регистра множимого соединена с второй группой ВХОДОВпервого сумматора, вторыми группами информационных входов коммутаторов первой группы и группой входов преобразователя прямого кода в дополнительный, выходы которого соединены С второй группой входов второго сумматора и вторыми группами информационных входов коммутаторов второй группы, выходы первого и второго сумматоров соединены с третьими группами информационных входов коммутаторов первой и второй групп, выходы которых соединены с входами первого и второго многовходовых сумматоров соответственно, выходы которых соединены с первой и второй группами входов регистра произведения соответственно, вькоды регистра множителя соединены с входами дешифраторов группы, выходы которых соединены с управляющими входами соответствующих Коммутаторов первой и второй групп. На чертеже приведена схема устройства. Устройство содержит регистр множимого 1, первьй и второй сумматоры 2, 3, первую и вторую группы коммутаторов 4, 5, первьй и второй многовходовые сумматоры 6, 7, регистр произведения 8, преобразователь 9 гфямого кода в дополнительньй, регистр множителя 10, группу дешифраторов 11-. В регистрах 1, 10, 8 хранятся действительные и мнимые части следуюпщх величин, множимого А, множителя В и произведения С.Устройство работает следующим образом. На выходах сумматоров 2 и 3 формируются соответственно величины ReA + IraA и ReA - ImA. На первую, вторую и третью группы информационных входов первого и второго коммутатора поступают соответственно величины ReA, ItnA, ReA + ImA, ReA, - ImA, ReA - ImA. В зависимости от значений i-го азряда действительной и мнимой часей множителя ReBj и ImB ; на выходах оответствующего дешифратора группы ешифраторов 11 устанавливается код, оторьй поступает на управляющие вхоJды групп коммутаторов 4 и 5. Если ReBj 1, а ImB 4 0, то на выходе соответствующего коммутатора групп коммутаторов 4 и 5 устанавливаются значение ReAt ; если ReB О, а ImB J 1,то на выходе соответствующ го коммутатора групп коммутаторов 4 и 5 устанавливаются значения ImA и-ImA соответственно, если ReB,; ImB Ч,то на выходах соответствующих коммутаторов устанавливаются значения ReA + ImA и ReA - ItnA. Сформулированные на выходах груп коммутаторов 4 и 5 величины складыв 224 ются (с учетом веса-разрядов) многовходовыми сумматорами 6 и 7, на выходах которых формируются величины ReA.ReB - 1mA, ImB и ImA-ReB + ReAX ;.ImB, которые заносятся в регистр произведения 8. Положительный эффект изобретения заключается в уменьшении аппаратурных затрат: вместо четырех блоков умножения, сложных по конструкции, устройство содержит преобразователь кода, две группы коммутаторов, два многовходовых сумматора и сруппу дешифраторов .

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство для быстрого преобразования Фурье | 1986 |

|

SU1327120A1 |

| Устройство для умножения комплексных чисел | 1985 |

|

SU1297034A1 |

| Устройство для умножения комплексных чисел | 1987 |

|

SU1517023A1 |

| Устройство для умножения комплексных чисел | 1986 |

|

SU1388851A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1984 |

|

SU1242986A1 |

| Вычислительное устройство для цифровой обработки сигналов | 1985 |

|

SU1295414A1 |

| СПЕЦИАЛИЗИРОВАННОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ОПЕРАЦИЙ С КОМПЛЕКСНЫМИ ЧИСЛАМИ | 1973 |

|

SU399859A1 |

| Устройство для быстрого преобразования Фурье | 1982 |

|

SU1101836A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1619300A1 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ КОМПЛЕКСНЫХ ЧИСЕЛ содержащее регистр множимого, регистр множителя, регистр произведения и первый сумматор, отличающееся тем, что, с целью упрощения устройства, оно содержит преобразователь прямого кода а дополнительный, второй сумматор, группу дешифраторов, первую и вторую группы коммутаторов, первый и второй многовходовые сумматоры, причем первая группа выходов регистра множимого соединена с первыми группами входов первого и второго сумматоров и первыми группами информационных входов коммутаторов первой и второй групп, вторая группа выходов регистра множимого соединена с второй группой входов первого сумматора, вторыми группами информационных входов коммутаторов первой группы и группой входов преобразователя прямого кода в дополнительный, выходы которого Соединены с второй группой входов второго сумматора и вторыми группами информационных входов коммутаторов второй группы, выходы первого и второго сумматоров соединены i с третьими группами информационных входов коммутаторов первой и второй (Л групп, выходы которых соединены с входами первого и второго многовходовых сумматоров соответственно, выходы которых соединены с первой и второй группами входов регистра произведения соответственно, выходы регистра множителя соединены с входами дешифраторов группы, выходы которых о :о соединены с управляющими входами соответствующих коммутаторов первой и второй групп. о с

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Папернов А.А | |||

| Логические основы ЦВТ | |||

| М., Сов.радио, 1972, с | |||

| Кран машиниста для автоматических тормозов с сжатым воздухом | 1921 |

|

SU194A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Рабинер Л., Гоулд Б | |||

| Теория и применение цифровой обработки сигналов | |||

| М., Мир, 1978, с | |||

| Устройство для выпуска сточных вод в реки | 1923 |

|

SU572A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1984-07-15—Публикация

1981-10-22—Подача