Изобретение относится к вычислительной технике и может быть использовано для построения процессоров быстрого преобразования Фурье, цифровых фильтров, вычислительных машин с комплексной арифметикой решения систем линейных алгебраических уравнений.

Цель изобретения - расширение функциональных возможностей за счет умножения комплексных чисел, представленных в дополнительном коде.

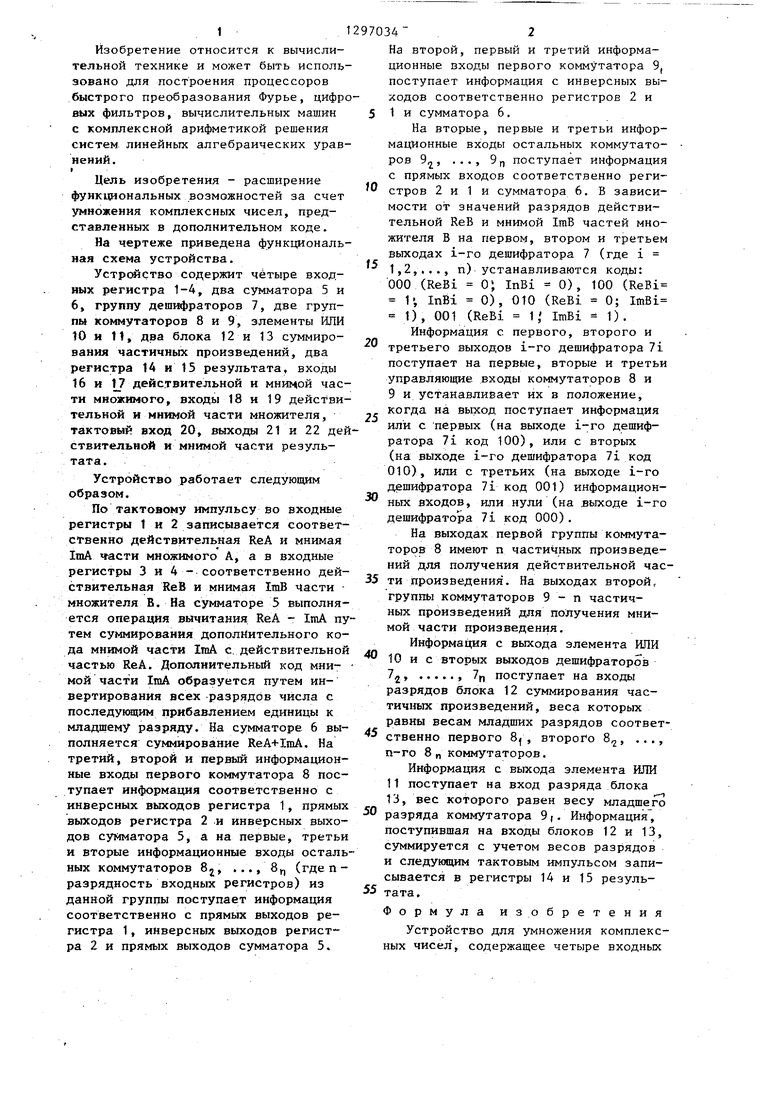

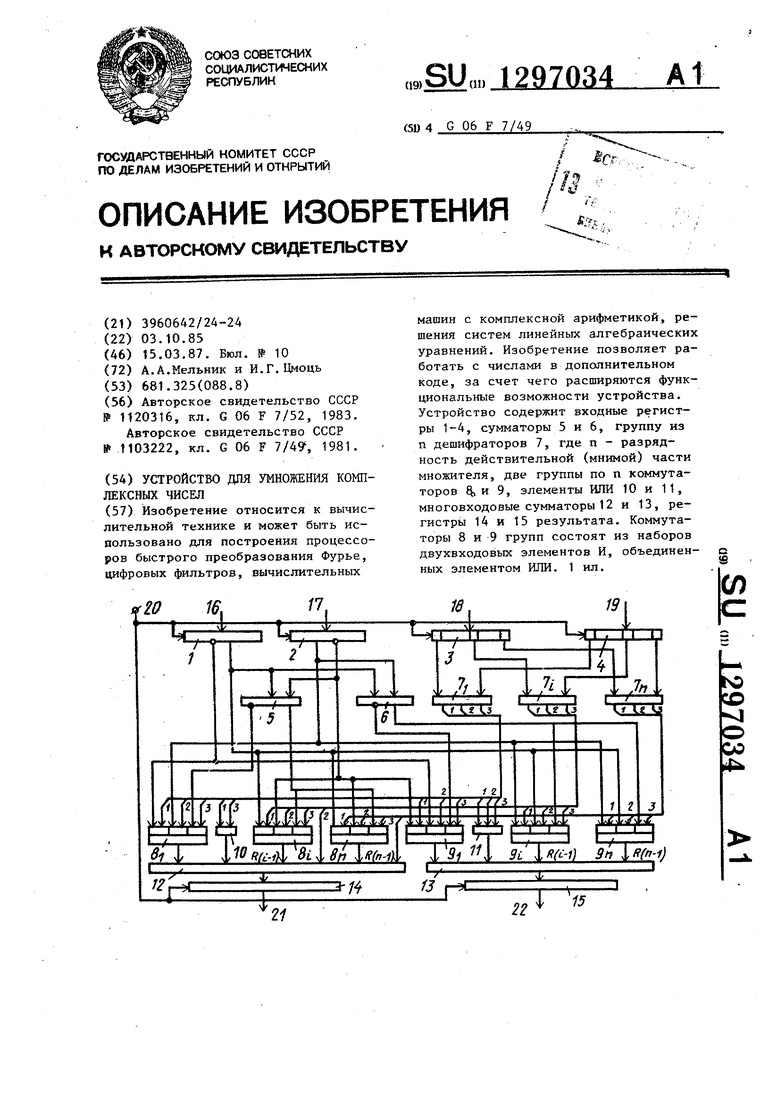

На чертеже приведена функциональная схема устройства.

Устройство содержит четыре входных регистра 1-А, два сумматора 5 и 6, группу дешифраторов 7, две группы коммутаторов 8 и 9, элементы ИЛИ 10 и 11, два блока 12 и 13 суммирования частичных произведений, два регистра 14 и 15 результата, входы 16 и 17 действительной и мнимой части множимого, входы 18 и 19 действительной и мнимой части множителя, тактовый вход 20, выходы 21 и 22 действительной и мнимой части результата.

Устройство работает следующим образом.

По тактовому импульсу во входные регистры 1 и 2 записывается соответственно действительная ReA и мнимая ImA множимого А, а в входные регистры 3 и 4 - соответственно действительная ReB и мнимая ImB части множителя В. На сумматоре 5 выполняется операция вычитания ReA - ImA путем суммирования дополйительного кода мнимой части ImA с. действительной частью ReA. Дополнительный код мни- мой части ImA образуется путем инвертирования всех разрядов числа с последующим прибавлением единицы к младшему разряду. На сумматоре 6 выполняется суммирование ReA+ImA. На третий, второй и первый информационные входы первого коммутатора 8 поступает информация соответственно с инверсных выходов регистра 1, прямых выходов регистра 2 и инверсных выходов сумматора 5, а на первые, третьи и вторые информационные входы остальных коммутаторов 8, . .., 8, (где п - разрядность входных регистров) из данной группы поступает информация соответственно с прямых выходов регистра 1, инверсных выходов регистра 2 и прямых выходов сумматора 5.

5

0

5

На второй, первый и третий информационные входы первого комму татора 9, поступает информация с инверсных выходов соответственно регистров 2 и

Iи сумматора 6.

На вторые, первые и третьи информационные входы остальных коммутаторов 9, ..., 9 поступает информация с прямых входов соответственно регистров 2 и 1 и сумматора 6. В зависимости от значений разрядов действительной ReB и мнимой ImB частей множителя В на первом, втором и третьем выходах i-ro дешифратора 7 (где i 1,2,..., п) устанавливаются коды: 000 (ReBi о; InBi 0), 100 (ReBi 1, InBi 0), 010 (ReBi 0; ItnBi 1), 001 (ReBi 1, ImBi 1).

Информация с первого, второго и третьего выходов i-ro дешифратора 7i поступает на первые, вторые и третьи управляющие- входы коммутаторов 8 и

9и устанавливает их в положение, когда на вьпсод поступает информация или с первых (на выходе i-ro дешифратора 7i код 100), или с вторых (на выходе i-ro дешифратора 7i код 010), или с третьих (на выходе i-ro дешифратора 7i код 001) информационных входов, или нули (на выходе i-ro дешифратора 7i код 000).

На выходах первой группы коммутаторов 8 имеют п частичных произведений для получения действительной час- 5 ти произведения. На выходах второй, группы коммутаторов 9 - п частичных произведений для получения мнимой части произведения.

Информация с выхода элемента ИЛИ

10и с вторых выходов дешифраторе:в

7, , 7f, поступает на входы

разрядов блока 12 суммирования частичных произведений, веса которых равны весам младших разрядов соответственно первого 8f, второго

п-го 8п коммутаторов.

Информация с выхода элемента ИЛИ

IIпоступает на вход разряда блока 13, вес которого равен весу младшего

разряда коммутатора 9,. Информация, поступившая на входы блоков 12 и 13, суммируется с учетом весов разрядов и следуюпщм тактовым импульсом записывается в регистры 14 и 15 результата.

Формула изобретения

Устройство для умножения комплексных чисел , содержащее четыре входных

0

0

5

-2

5

регистра, два сумматора, две группы коммутаторов, два блока суммирования частичных произведений, два регистра результата и группу дешифраторов , причем информационные входы. первого и второго входных регистров являются соответственно входами действительной и мнимой-части множимого устройства, информационные входы третьего и четвертого регистров являются соответственно входами действительной и мнимой части множителя устройства, тактовый вход устройства соединен с входами синхронизации первого, второго, третьего и четвертого входных регистров результата, выходы первого и второго регистров результата являются соответственно вьгходами действительной и мнимой части результата устройства, прямой выход первого входного регистра соединен с первыми информационными входами первого и второго сумматоров и с первыми информационными входами i-x коммутаторов первой и второй групп (где i 2,3,..,, n,n - разрядность действительной и мнимой частей сомножителей), прямой выход второго входного регистра соединен с вторым информационным входом второго сумматора и вторыми информационными входами i-x коммутаторов второй группы, третьи информационные входы которых соединены с прямым выходом второго сумматора, прямой выход первого сумматора соединен с вторыми информационными входами i-x коммутаторов первой группь, выходы J-X раз рядов (где j 1,2, ... п) третьего и четвертого входных регист ров соединены с первым и вторым входами- j-ro дешифратора группы, первый второй и третий выходы которого соединены с первыми, вторыми и третьими управляющими входами j -x коммутаторов первой и второй групп, выходы которых соединены соответственно с j-ми информационными входами первого и второго блоков суммирования частич

Редактор И.Касарда

Составитель Н.Маркелова

Техред М.Ходанич Корректор И.Муска

Заказ 781/51

.Тираж 673- Подписное ВНИИ1Ш Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушскця наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

O

5

0

0

5

0

5

5

ных произведении, выходы которых соединены с информационными входами соответственно первого и второ ро- регистров результата, отличающееся тем, что, с целью расширения функциональных возможностей за счет умножения комплексных чисел, представленных в дополнительном коде , в устройство введены nepsbrii и второй элементы ИЛИ, при этом инверсный выход первого входного регистра соединен с первыми информационными входами первых коммутаторов перквой и второй групп, инверсный выход второго входного регистра еоедимен с вторым информационным входом перво-ро сумматора, с третьшли информационными входами i-x коммутаторов перввй группы и вторьм информационным Bxq- дом первого коммутатора второй группы, третий информа1 онный вход которого соединен с инверсным выходом второго сумматора, второй и третий информационные входы первого коммутатора первой группы сое.-.инены соответственно с прямым выходом второго входного регистра и инверсным вводом первого сумматора, первый и третий выходы первого дешифратора группы соединены соответственно с первыми и -вторьши входами первого и второго элементов ИЛИ, второй выход первого дешифратора группы соединен с третьим входом второго элемента ИЛИ. выход первого элемента ИЛИ соединен с первым информационным входом младшего разряда первого блока суммирования частичных произведений, второй выход i-ro дешифратора группы соединен с i-M информационным входом младшего разряда первого блока суммирования частичных произведений, выход второго элемента ИЛИ соединен с первым информационным входом младшего разряда второго блока суммирования частичных произведений, вход переноса первого блока суммирования частичных произведений соединен с входом логической единицы устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения комплексных чисел | 1987 |

|

SU1517023A1 |

| Устройство для умножения комплексных чисел | 1986 |

|

SU1388851A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1984 |

|

SU1242986A1 |

| Устройство для умножения комплексных чисел | 1981 |

|

SU1103222A1 |

| Устройство для быстрого преобразования Фурье | 1982 |

|

SU1170462A1 |

| Процессорный элемент устройства для быстрого преобразования Фурье | 1985 |

|

SU1288716A1 |

| Вычислительное устройство для цифровой обработки сигналов | 1985 |

|

SU1295414A1 |

| Устройство для быстрого преобразования Фурье | 1982 |

|

SU1101836A1 |

| Арифметическое устройство для быстрого преобразования Фурье | 1986 |

|

SU1383394A2 |

| УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНЫХ ОРТОГОНАЛЬНЫХ ПРЕОБРАЗОВАНИЙ | 1990 |

|

RU2024931C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения процессоров быстрого преобразования Фурье, цифровых фильтров, вычислительных машин с комплексной арифметикой, решения систем линейных алгебраических уравнений. Изобретение позволяет работать с числами в дополнительном коде, за счет чего расширяются функциональные возможности устройства. Устройство содержит входные регистры 1-4, сумматоры 5 и 6, группу из п дешифраторов 7, где п - разрядность действительной (мнимой) части множителя, две группы по п коммутаторов % и 9, элементы ИЛИ 10 и 11, мн о говходо вые сумматоры 12 и 13, регистры 14 и 15 результата. Коммутаторы 8 и 9 групп состоят из наборов двухвходовых элементов И, объединенных элементом ИЛИ. 1 ил. с S (Л

| Устройство для умножения комплексного числа на комплексную константу | 1983 |

|

SU1120316A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения комплексных чисел | 1981 |

|

SU1103222A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-15—Публикация

1985-10-03—Подача