Изобретение относится к вычислительной технике и может быть использовано для регистрации и обработки статистической информации

Целью изобретения является повышение быстродействия и упрощение устройства.

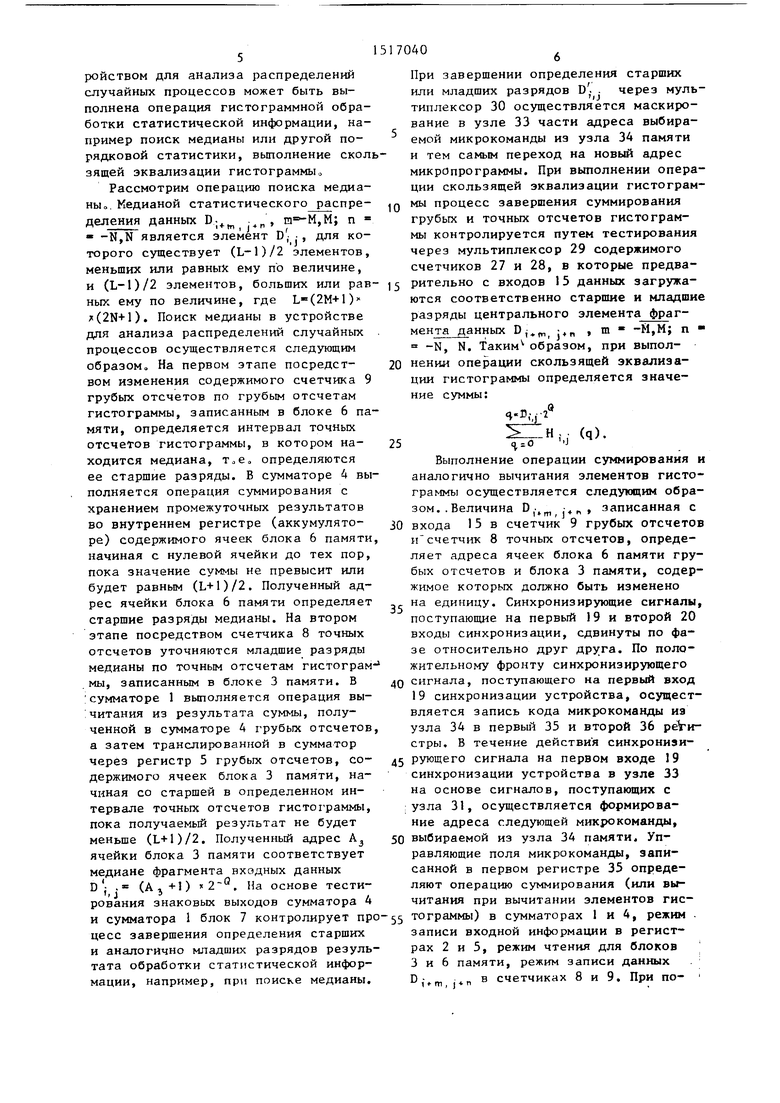

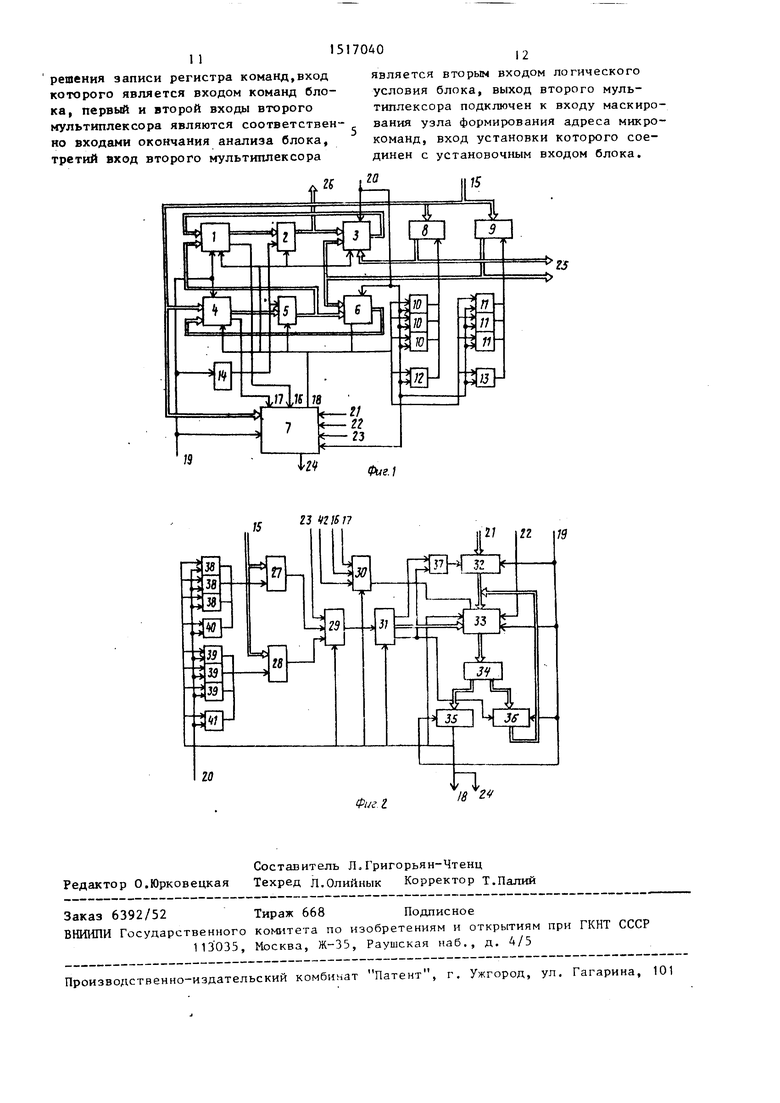

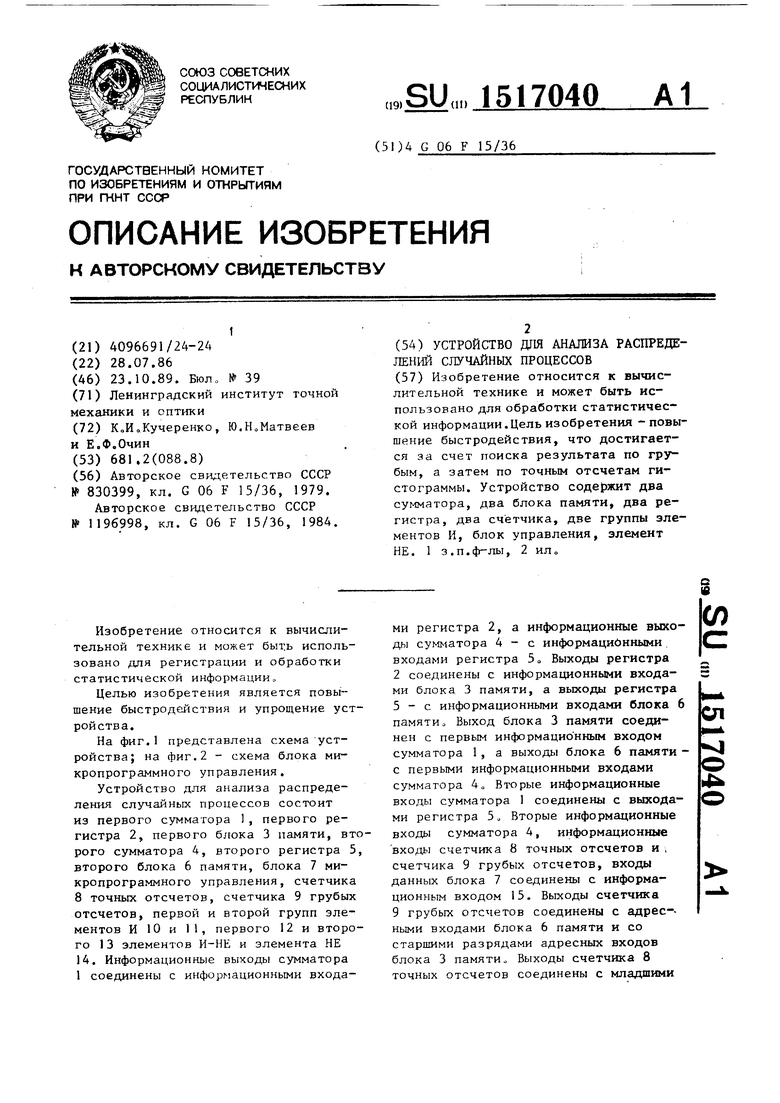

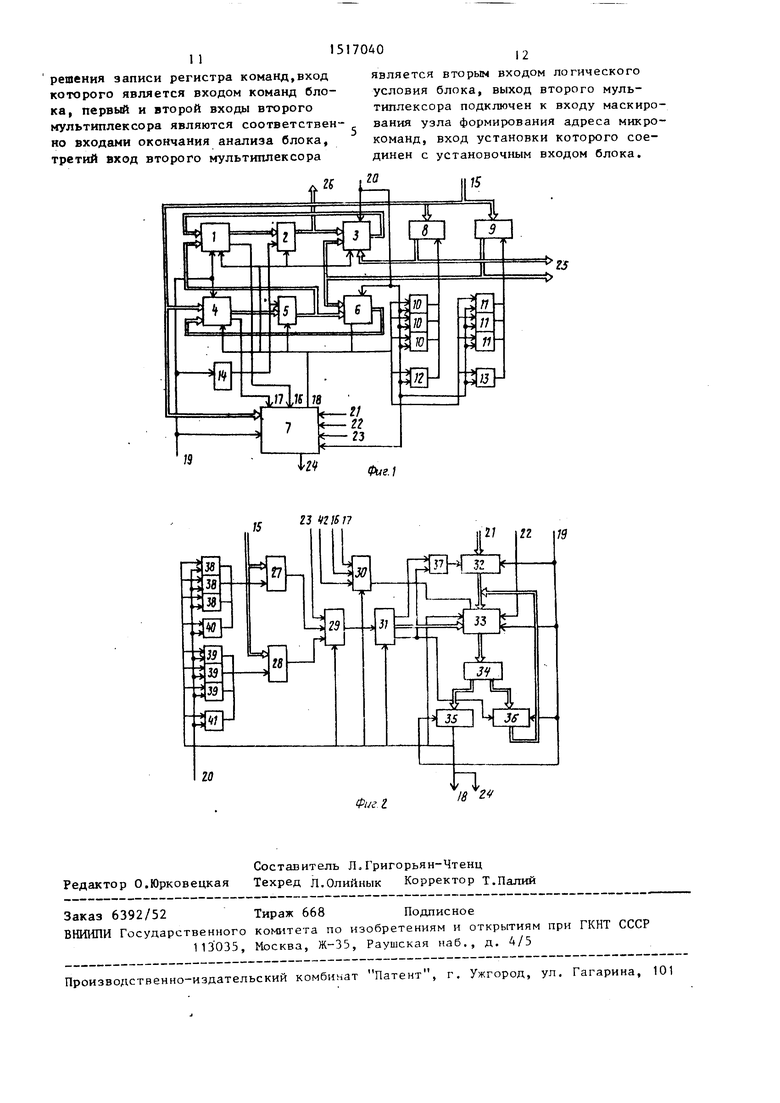

На фиг.1 представлена схема устройства; на фиг.2 - схема блока микропрограммного управления.

Устройство для анализа распределения случайных процессов состоит из первого сумматора 1, первого регистра 2, первого блока 3 памяти, второго сумматора 4, второго регистра 5, второго блока 6 памяти, блока 7 микропрограммного управления, счетчика 8 точных отсчетов, счетчика 9 грубых отсчетов, первой и второй групп элементов И 10 и 11, первого 12 и второго 13 элементов И-НЕ и элемента НЕ 14. Информационные выходы сумматора 1 соединены с информационными входами регистра 2, а информационные выходы сумматора 4 - с информацийнными входами регистра 5 Выходы регистра 2 соединены с информационными входами блока 3 памяти, а выходы регистра 5 - с информационными входами блока 6 памяти о Выход блока 3 памяти соединен с первым информацио нным входом сумматора 1, а выходы блока 6 памяти - с первыми информационными входами сумматора 4„ Вторые информационные входы сумматора 1 соединены с выходами регистра 5. Вторые информационные входы сумматора 4, информационные входы счетчика 8 точных отсчетов и , счетчика 9 грубых отсчетов, входы данных блока 7 соединены с информационным входом 15. Выходы счетчика 9 грубых отсчетов соединены с адрес-- ными входами блока 6 памяти и со старшими разрядами адресных входов блока 3 памяти Выходы счетчика 8 точных отсчетов соединены с младшими

ё

(Л

О1

о

разрядами адресных входов блока 3 памяти. На схеме обозначены: входы 16 и 17 окончания анализа блока 7 микрокоманд, выход 18 микрокоманд блока 7, первый и второй синхронизирующие входы 19 и 20 устройства, вход 21 загрузки команд блока 7,вход 22 установки исходного состояния блока микрокоманд, вход 23 задания режима работы устройства, выход 24 режима функционирования устройства и информационные выходы 25 и 26 устройства, В состав блока 7 входят первый

и второй счетчики 27 и 28, первый и 15 х (2N+J)О-разрядных злементов D; j,, второй мультиплексоры 29 и 30, узел ,М; ,N, паралелльно форми- 31 задания следующего адреса, регистр руются точные отсчеты гистограммы

Н... (q)-i:: XZlDi.,j,. -q-2- l, q e |0,1 ,. .. , ( )(О

гистограммы

IJ т:-ЛЛ П.Ц

в блоке 3 памяти и грубые отсчеты

М N Q/1

Л «-О/Зт Л Г /-V 1 /Т

,,„,, 2 -q 2 , qE 0,1,...,(2

т w

H..(q)-x:x:

Q/3

1)Ь

(2)

т«-ДЛ Пг-N

r

В блоке 6. При этом что Q четно В выра предполагается, что

.q.2«.

CD.

tA.

n,j

32 команд, узел 33 формирования адреса микрокоманд, узел 34 постоянной памяти, первый и второй регистры 35 и 36 микрокоманд, первый элемент И-НЕ 37, первая группа 38 элементов И, вторая группа 39 злементов И, элементы И-НЕ 40 и 41, вход 42 логического сигнала.

Устройство работает следующим образом.

Для анализа распределений случайных процессов обрабатьшаемого фрагмента данных, состоящего из ()

Q/3

1)Ь

(2)

а

II d i, j , г 2 ,

q положительные целые числа; 2 2 - коэффициенты нормирования:

-в

q

«q

2-%

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки данных гистограмм | 1984 |

|

SU1196898A1 |

| Устройство для гистограммной обработки изображений объектов | 1989 |

|

SU1667106A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Микропрограммный процессор | 1987 |

|

SU1517034A1 |

| Вычислительное устройство для ранговой фильтрации | 1989 |

|

SU1656554A1 |

| Устройство для формирования адресов процессора быстрого преобразования Фурье | 1989 |

|

SU1691853A1 |

| Микропрограммное устройство управления с самоконтролем | 1985 |

|

SU1247871A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1425706A1 |

| Микропрограммное устройство управления (его варианты) | 1984 |

|

SU1159020A1 |

Изобретение относится к вычислительной технике и может быть использовано для обработки статистической информации. Цель изобретения - повышение быстродействия, что достигается за счет поиска результата по грубым, а затем по точным отсчетам чистограммы. Устройство содержит два сумматора, два блока памяти, два регистра, два счетчика, две группы элементов И, блок управления, элемент НЕ. 2 ил.

i + m , 1 4- ъ , г

А

q

2-.

входных данных о Блок 7 вырабатЕ шает управляющие сигналы записи-чтения для блоков 3 и 6 памяти, сигналы хранения информации/записи входных данных для первого 2 и второго 5 ре- 45 гистров, а также код операции для первого 1 и второго 4 сумматоров. В сумматоре 1 и сумматоре 4 грубых отсчетов при рекурсивной обработке пересекающихся фрагментов входных данляет адрес ячейки А блока 6 памяти 50 вьтолняются операция суммирования содержимого выбранных ячеек блоков 3 и 6 памяти с единицей, если входные данные входят в новый фрагмент, и Операция вычитания из содержимого выбранных ячеек блоков 3 и 6 памяти единиц, если входные данные входят в предьщущий фрагмент.

После завершения формирования грубых отсчетов и точных отсчетов уст-

Блок 7 посредством управляющих сигналов устанавливает в режим приема входных данных счетчик 8 точных отсчетов и счетчик 9 грубых отсчетов. Причем в счетчик 9 грубых отсчетов записьгоаются Q/2 старших разрядов входных данных 0,Чт, j+n поступающих с входа 15, а в счетчик 8 точных отсчетов - младшие Q/2 разрядов ,. j.n . Величина D ., , опредеQ/-2

грубых отсчетов:

At (D,-.,j.Jcl,:da,J)-2 и адрес ячейки А блока 3 памяти

Aj (D

..j.Jd , : d,).

55

содержимое которых изменяется на единицу для каждого нового значения-.

a/2

О, если

.,,,..,,, -2

-all

если

-.-f

+m, j + n, f

л r.

-q 2

-Qll

ройством для анализа распределений случайных процессов может быть выполнена операция гистограммной обработки статистической информации, например поиск медианы или другой порядковой статистики, выполнение сколзящей эквализации гистограммы.

Рассмотрим операцию поиска медианы, Медианой статистического распределения данных D; ., ,М; п -N,N является элемент D; . , для которого существует (L-l)/2 элементов, меньщих или равных ему по величине, и (L-l)/2 элементов, больших или равных ему по величине, где L CZM-t-l) ;(2N+1). Поиск медианы в устройстве для анализа распределений случайных процессов осуществляется следующим образом. На первом этапе посредством изменения содержимого счетчика 9 грубых отсчетов по грубым отсчетам гистограммы, записанным в блоке 6 памяти, определяется интервал точных отсчетов гистограммы, в котором находится медиана, определяются ее старшие разряды. В сумматоре 4 выполняется операция суммирования с хранением промежуточных результатов во внутреннем регистре (аккумуляторе) содержимого ячеек блока 6 памяти начиная с нулевой ячейки до тех пор, пока значение суммы не превысит или будет равным (L+1)/2. Полученный адрес ячейки блока 6 памяти определяет старшие разряды медианы. На втором этапе посредством счетчика 8 точных отсчетов уточняются младшие разряды медианы по точным отсчетам гистограм мы, записанным в блоке 3 памяти. В :сумматоре 1 выполняется операция вы- читания из результата суммы, полученной в сумматоре А грубых отсчетов а затем транслированной в сумматор через регистр 5 грубых отсчетов, содержимого ячеек блока 3 памяти, на- чнная со старшей в определенном интервале точных отсчетов гистограммы, пока получаемый результат не будет меньше (L+l)/2. Полученньй адрес А ячейки блока 3 памяти соответствует медиане фрагмента входных данных D j . (Aj-t-1) 2. На основе тестирования знаковых выходов сумматора 4 и сумматора 1 блок 7 контролирует процесс завершения определения старших и аналогично младших разрядов результата обработки статистической информации, например, при поиске медианы.

При завершении определения старших или младших разрядов D; . через мультиплексор 30 осуществляется маскирование в узле 33 части адреса выбираемой микрокоманды из узла 34 памяти и тем самым переход на новый адрес микропрограммы. При выполнении операции скользящей эквализации гистограмд мы процесс завершения суммирования грубых и точных отсчетов гистограммы контролируется путем тестирования через мультиплексор 29 содержимого счетчиков 27 и 28, в которые предва5 рительно с входов 15 данных загружаются соответственно старшие и младшие разряды центрального элемента фрагмента данных Dj -,„ , m -М,М; п -N, N. Таким образом, при выпол0 нении операции скользящей эквалиэа- ции гистограммы определяется значение суммы:

25

-.0

Н,-, (q).

Выполнение операции суммирования аналогично вычитания элементов гистограммы осуществляется следующим образом. . Величина D|-, i+n записанная с

30 входа 15 в счетчик 9 грубых отсчетов и счетчик 8 точных отсчетов, определяет адреса ячеек блока 6 памяти грубых отсчетов и блока 3 памяти, содержимое которых должно быть изменено

3 на единицу. Синхронизирующие сигналы, поступающие на первый 19 и второй 20 входы синхронизации, сдвинуты по фазе относительно друг друга. По положительному фронту синхронизирующего

40 сигнала, поступающего на первый вход 19 синхронизации устройства, осуществляется запись кода микрокоманды из узла 34 в первьш 35 и второй 36 регистры, В течение действия синхронизид5 рующего сигнала на первом входе 19 синхронизации устройства в узле 33 на основе сигналов, поступающих с ; узла 31, осуществляется формирование адреса следующей микрокоманды,

50 выбираемой из узла 34 памяти, Управляющие поля микрокоманды, записанной в первом регистре 35 определяют операцию суммирования (или вычитания при вычитании элементов гис55 тограммы) в сумматорах 1 и 4, режим . записи входной информации в регистрах 2 и 5, режим чтения для блоков 3 и 6 памяти, режим записи даиных .

D

t т , j В счетчиках 8 и 9, При поС1 :. . : .1:;1 . : ,. .о ЯХО, . . . : -. . i: ih; Г i .1,

к)п-его С1;1 :; .а : i -ч - .a o:i4t / } ; ЧЛ-: ; г и . :

:М;.;.. - - - . :4;...j,. -, , , , :

: с 40 ;-х i ; - г.-. п . jjuKHO,, - ; 1-;г1ч 1 :;; i - ,

-.(лД-Г :.- il- . - .

.: ичаип,- ;-.л,. i; : : -. : . ;

..К.НУ-;н)1.1 ,v ;ic ii-v, :: . . :- : , I c liHri-ia,;. И iV . ;

СЯ J li U v - л ;tf ;i .- - i., . . :;

Л Ч ре: у Ч- :.; .-::, - ;. - .

JT 4 I .) . - i; : . : Xp),.;Г: ii ;i U - ..

са;с H - 3a;-epiiiei-ui. ,-u- , i-i;. xi..H3Ji Jia t/ . .-;, // f, v H M V ; Ч- n ; HOCr Tv. ИНчиО vi taji-i ЧИ I у). ; л-й,ау1. :Д.. :.r : i ком,:. .I,; .

,13 .. ...U - 4.i ajj ; . i w i,:j;

M / n y3.;It j .iVTi ; i;-- : pt,. rV

:ia eiuiiKuii; 1пер1-:ч О: о piiy Tni.1 ; . : -етчи;,:э ; . } .. ii i ; b,, t: Hn г;с.ио ;и -:ib ., ,- ч Л 1 с.и.:г: Hf, t :-.;,- : 11. :; i- p . J : ..гл-лк:- :4i- -1 : :. : c: .,;;:-/ t ,.i.., :. . , :

Л V I v i -: ч l

счераг,..- .-, ,. V . ..ч :,. :

. Т. S 1: ч -

V Ь

,TOl i. i ii: ;..l

п -V

i 1И J Ч,,

.TL ,.: i :M ; , ; :i. . nj -; ;.; i-fsi . , :. I --c j i; КЫ;; r. j .. ; . :. .,.: 1., i-,.:06jioK;4- - . -: , -)..: ;.; , u; i jieBoi c ., ,,,; r,,i ., I i,.....i;.c ,:

СТВПМ ;,.. : p. ЛХ t ; , ci i СЯ y-.: -:. ,, :-,,.,..1 , -:;.

ме iv ,;.,: /- м.,; i.iM.. у

32 ,:: , ,,:,.-.-.- i,:.l

1 , : 1. i ч

,. : I г : о ч,. . iV . ri f-tu

..r liO ./. V .. TT;j:...i iMiS : . VlH-с я тем, что, с целью повышения бы- стродейств1-ш и упрощения устройства, в него введены две группы элементов И, два элемента И-НЕ и элемент НЕ, счетчик.точньк отсчетов и счетчик грубых отсчетов, при этом выход счетчика точных отсчетов подключен к первому адресному входу первого блока памяти, второй адресный вход которог объединен с адресным входом второго блока памяти и соединен с выходом счетчика грубых отсчетов, выход первого блока памяти подключен к первому входу первого сумматора, второй вход которого соединен с выходом второго регистра, второй вход второго сумматора объединен с информационным входом блока микропрограммного управления, с информационными входа- ми счетчиков точного и грубого отсчетов и является входом устройства, выход микрокоманд блока микропрограммного управления подключен к первым входам элементов И первой и второй групп и к первым входам первого и второго элемен тов И-НЕ, выходы которых соединены соответственно с входами записи чисел счетчиков точных и,грубых отсчетов,выходы элементов И первой и второй групп подключены соответственно к входам установки в О, сложения и вычитания счетчиков точного и грубого отсчетов, вторые входы элементов И первой и второй групп, вторые входы первого и второго элементов И-НЕ объединены с вторым синхронизирующим входом блока микропрограммного управления и вторым синхронизирующим входом устройства, зна- ковые выходы первого и второго сумматоров подключены к входам окончания анализа блока микропрограммного управления, вход элемента НЕ соединен с первым входом синхронизации устрой- ства, а выход подключен к входам стро бирования регистров, выход первого регистра, выходы счетчиков точных и грубых отсчетов являются информационными выходами устройства,

2, Устройство по п„1, о т л и - чающееся тем, что блок микропрограммного управления содержит первую и вторую группы элементов И, два мультиплексора, первый, второй и тре- тий элементы И-НЕ, узел задания следующего адреса, регистр команд, узел формирования адреса микрокоманды, узел постоянной памяти, порвьй и второй регистры микрокоманд, первый и второй счетчики, при этом выход узла формирования адреса микрокоманды подключен к адресному входу узла постоянной памяти, информационные выходы которого соединены с информационными входами первого и второго регистров микрокоманд, вькод первого регистра микрокоманд подключен к первым входа элементов И первой и второй групп, к первым входам второго и третьего элементов И-НЕ, входам управления мультиплексоров, узла формирования следующего адреса, входу переноса узла формирования адреса микрокоманды и является выходом микрокоманд блока и выходом режима функционирования, выход второго регистра микрокоманд объединен с выходом регистра команд и соединен с информационным входом узла формирования адреса микрокоманд, вторые входы элементов И первой и второй групп объединены с вторыми входами второго и третьего элементов И и являются вторым синхронизирующим входом блока, выходы первой и второй групп элементов И и выходы второго и третьего элементов И- НЕ подключены соответственно к входам установки в О, сложения, вычитания и записи числа соответственно первого и второго счетчиков, информационные входы которых являются информационным входом блока, выходы счетчиков соединены соответственно с первым и вторым информационными входами первого мультиплексора, третий вход которого является первым входом логических условий блока, выход первого мультиплексора подключен к информационному входу узла задания следующего адреса, информационный выход которого соединен с входом управления узла формирования адреса микрокоманды, синхронизирующий вход которого объединен с синхронизирующими входами первого и второго регистрюв микрокоманд, регистра команд и является первым синхронизирующим входом блока, вход разрешения считывания второго регистра микрокоманд объединен с первым входом первого элемента И-НЕ и соединен с выходом разрешения считывания узла задания следую- щего адреса, второй выход разрешения считывания кбторого по-дключен к второму входу первого элемента И-НЕ, выход которого соединен с входом разрешения записи регистра команд,вход которого является входом команд блока, первый и второй входы второго мультиплексора являются соответственно входами окончания анализа блока, третий вход второго мультиплексора

гЗ 421В17

является вторым входом логического условия блока, выход второго мультиплексора подключен к входу маскирования узла формирования адреса микрокоманд, вход установки которого соединен с установочным входом блока.

га

Фиг.1

Фиг. 2

| Устройство для анализа распреде-лЕНий СлучАйНыХ пРОцЕССОВ | 1979 |

|

SU830399A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для защиты от повреждений батареи конденсаторов | 1984 |

|

SU1196998A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-10-23—Публикация

1986-07-28—Подача