сд

о со

16, третий 17 и четвертый 18 мультиплексоры, дешифратор 19 разрядов, зторой элемент ИЛИ 20, второй 21 и третий 22 элементы И, элемент И-НЕ н группу элементов ИЛИ 24. При необходимости выборки из блока 2 микропрограммной памяти константы в К-й микрокоманде на втором выходе пер- 13ОГО регистра 3 микрокоманд выставляется сигнал логической единицы, который запрещает прием на второй регистр 4 микрокоманд и разрешает прием на регистр 15 констант. При

5170344

вьтолнении операции вычисления корня используется итерационньш алгоритм, осуществляющий последовательное оп- с редепение значений разрядов результата. Определение значений р-го разряда производится по знаку разности между значением числа, из которого вычисляется корень,и соответствующим JO ему приближением. При выполнении операций осуществляются ветвление по группе условий на входах первого мультиплексора 5 и управление адресами микропрограммной памяти. 4 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Устройство для управления операцией записи | 1981 |

|

SU1003091A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Устройство для обработки данных гистограмм | 1984 |

|

SU1196898A1 |

| Устройство для сопряжения ЭВМ с периферийной системой | 1989 |

|

SU1635188A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1649540A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1170457A1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке микропрограммных процессоров цифровых вычислительных машин. Цель изобретения - увеличение быстродействия процессора при выполнении операций над разрядами, а также при выполнении операции вычисления корня. Это достигнуто за счет ведения возможности выборки констант из блока памяти микропрограмм на регистр со специальными установочными входами с совмещением выполнения действий над ними, а также за счет введения возможности ветвления по группе условий. Микропрограммный процессор содержит операционный блок 1, блок 2 микропрограммной памяти, первый 3 и второй 4 регистры микрокоманд, первый мультиплексор 5, блок 6 управления, первый элемент ИЛИ 7, элемент НЕ 8, счетчик 9, дешифратор 10 операций, регистр 11 адреса, регистр 12 связи с блоками памяти, первый элемент И 13, регистр 15 констант, второй 16, третий 17 и четвертый 18 мультиплексоры, дешифратор 19 разрядов, второй элемент ИЛИ 20, второй 21 и третий 22 элементы И, элемент И-НЕ и группу элементов ИЛИ 24. При необходимости выборки из блока 2 микропрограммной памяти константы в K-й микрокоманде на втором выходе первого регистра 3 микрокоманд выставляется сигнал логической единицы, который запрещает прием на второй регистр 4 микрокоманд и разрешает прием на регистр 15 констант. При выполнении операции вычисления корня используется итерационный алгоритм, осуществляющий последовательное определение значений разрядов результата. Определение значений P-го разряда производится по знаку разности между значением числа, из которого вычисляется корень и соответствующим ему приближением. При выполнении операций осуществляются ветвление по группе условий на входах первого мультиплексора 5 и управление адресами микропрограммной памяти. 5 ил.

Изобретение относится к вычислител ной технике и может быть использовано при разработке микропрограммных процессоров цифровых вычислительных ма-

И ИН.

Цель изобретения - повышение быст- родействия процессора.

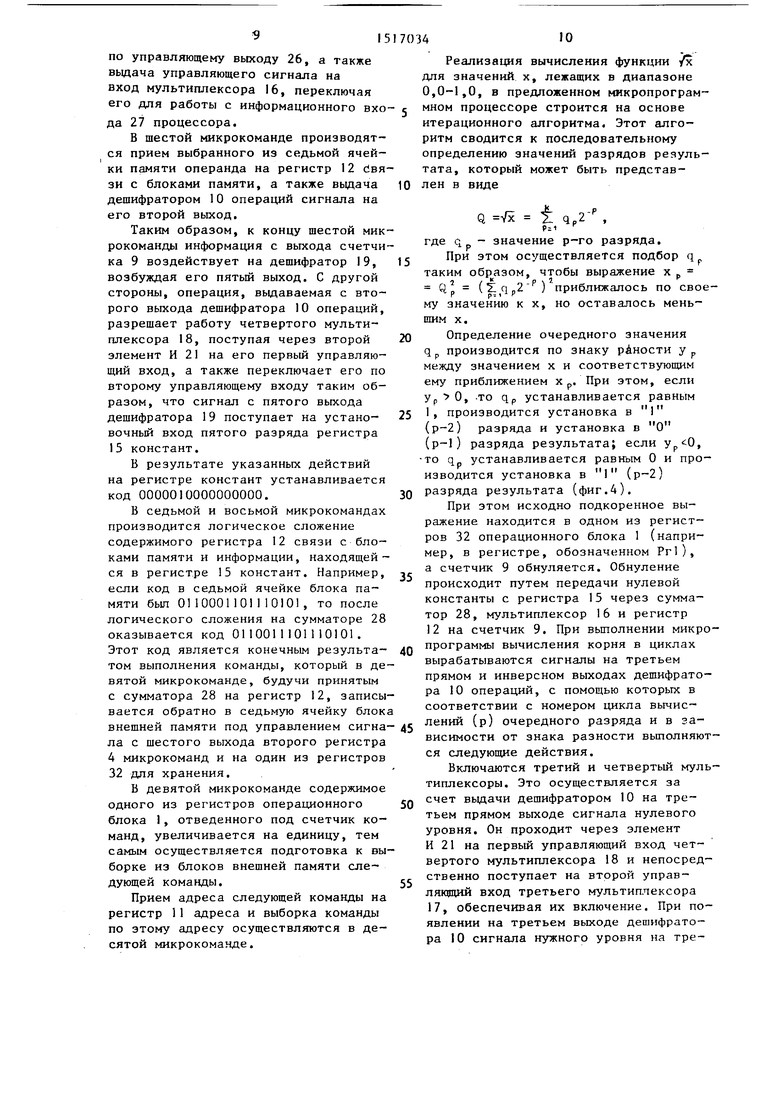

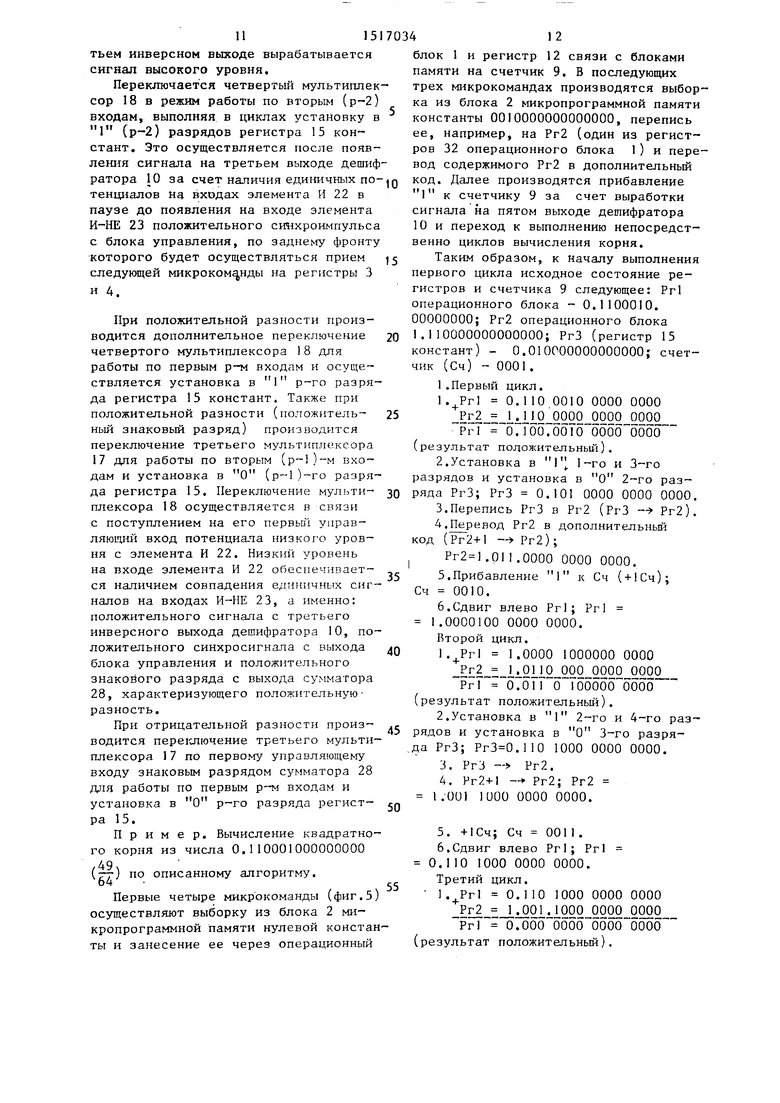

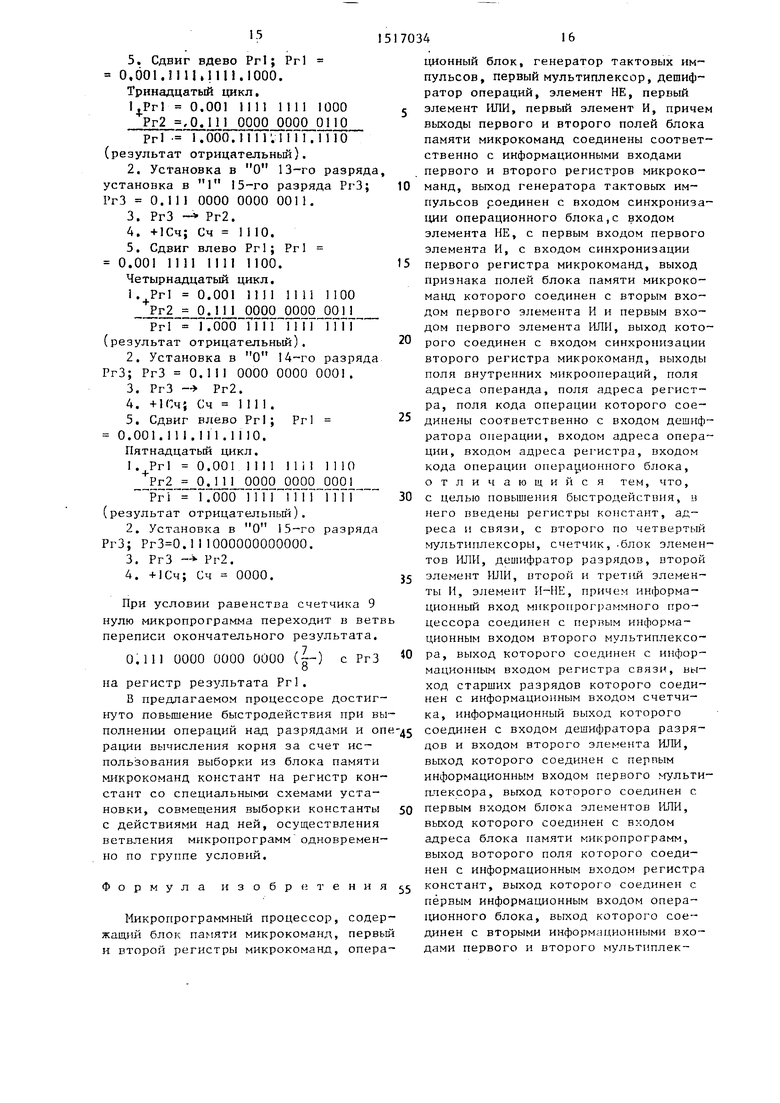

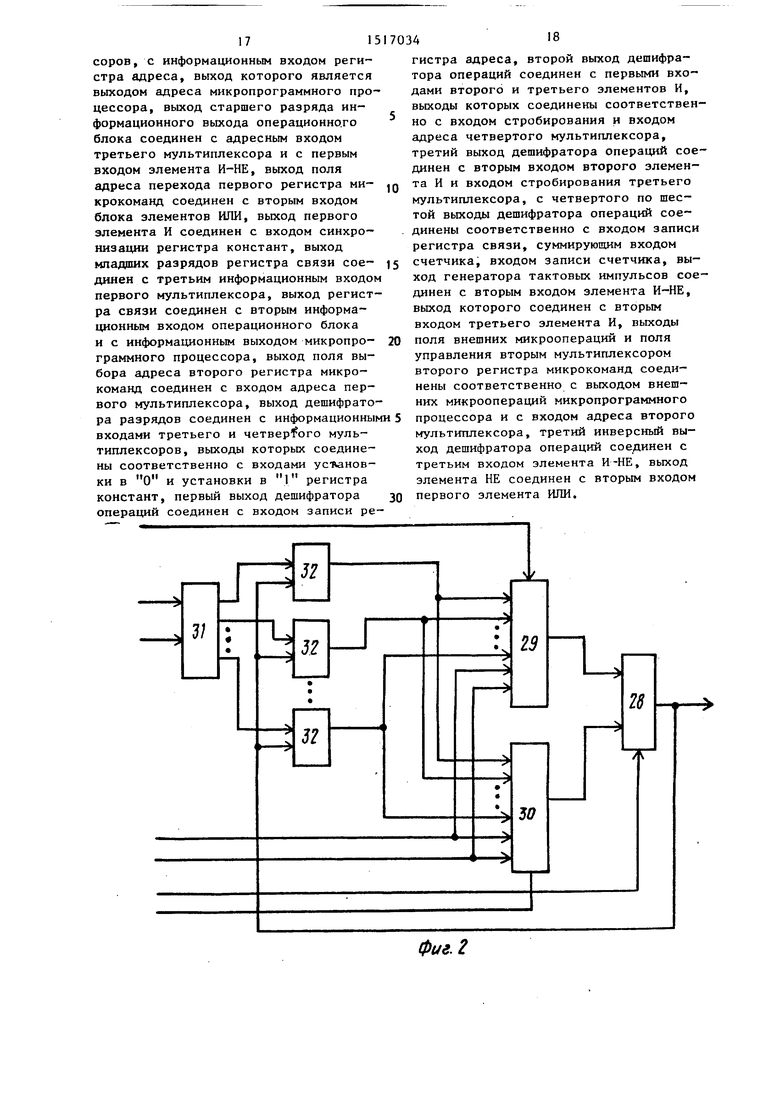

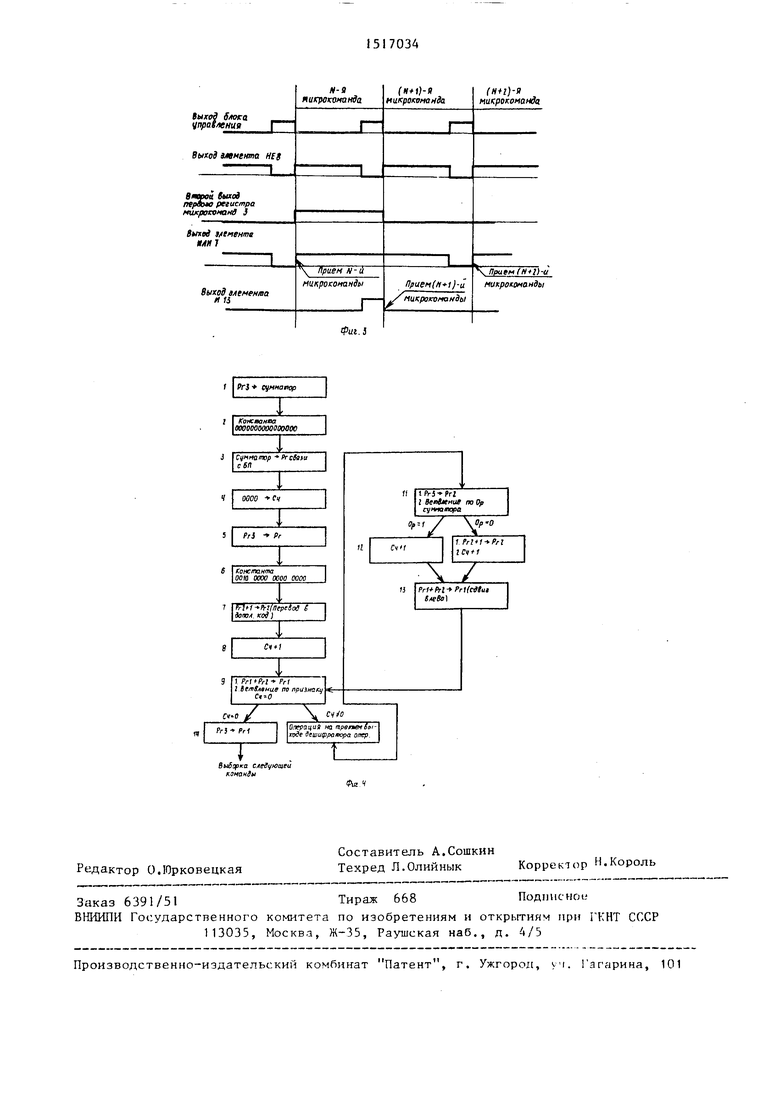

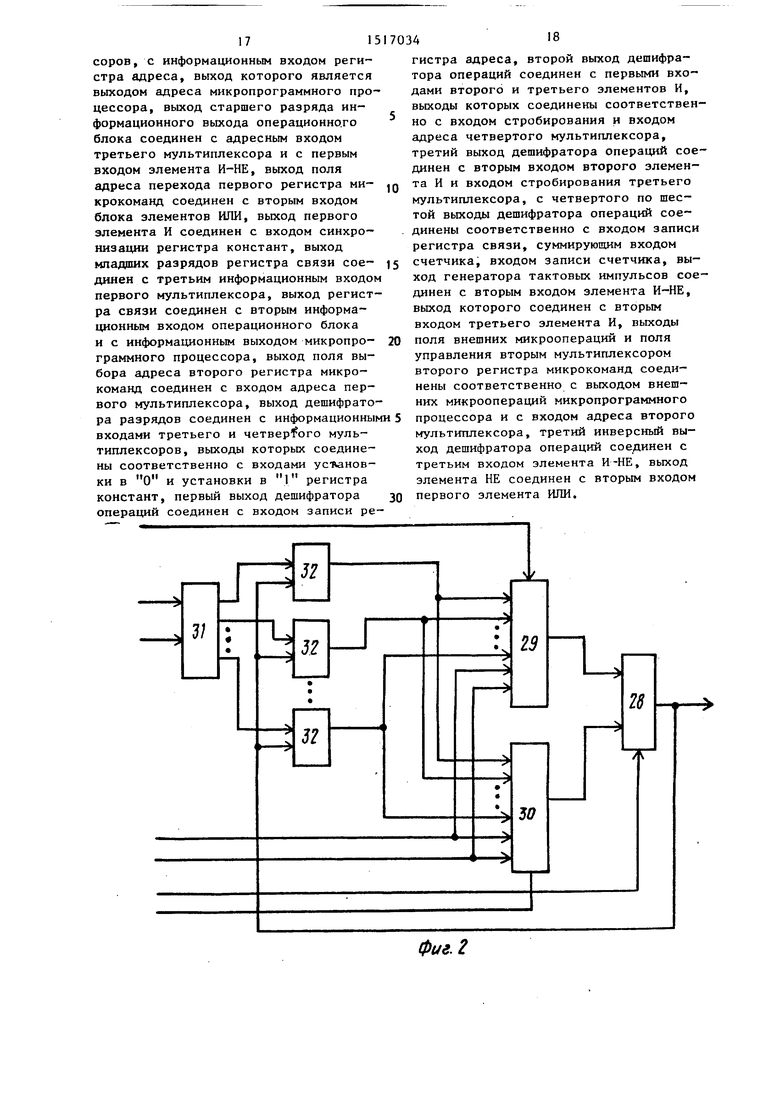

На фиг,1 представлена структурная схема микропрограммного процессора; па фиг. 2 структурная схема операционного блока; на фиг ,3 - временная диа- грамма формирования сигналов приема на констант и второй регистр микрокоманд; на фиг.4 - алгоритмы вычисления квадратного корня.

Микропрограммный процессор (фиг.) содержит онерационрйш блок 1, блок

2микропрограммной памяти, первый

3и второй 4 регистры микрокоманд, первый мультиплексор 5, блок б управления (генератор тактовых импульсов), первьш элемент ИЛИ 7, элемент НЕ 8, счетчик 9, дешифратор 10 операций, регистр 11 адреса, регистр 12 связи, первьш элемент И 13, выход 14 адреса процессора, регистр 15 констант, вто- рой, третий и четвертьш мультиплексоры 16-18. дешифратор 19 разрядов, второй элемент ИЛИ 20, второй и третий элементы И 21 и 22, элемент И-НЕ 23, группу элементов ИЛИ 24, информапионный выход 25 процессора, выход 26 ппешних микропроцессоров и информационный вход 27.

Операционньш блок 1 (фиг.2) содержит сумматор 28, (М-2)-разрядные муль тинлексоры 29 и 30, М-разрядный де- мультиплексор 31 и группу из М регистров 32, выходами соединенных с соот- зетствугощими входами пятого 29 и шес

того 30 мультиплексоров, связанных соответственно с первым и вторым входами сумматора 28, выход которого соединен с выходом блока 1 и входами М регистров 32, синхровходы которых подключены к соответствующим выходам демультинлексора 31, первый и второй входы блока I соединены соответственно с (М-1)-ми и (М-2)-ми входами мультиплексоров 29 и 30, третий и четвертый входы блока 1 - с управляющими входами сумматора 28 и демультиплексора 31, пятый - с управляющими входами пятого 29 и шестого 30 мультиплексоров, синхровход - с входом демультиплексора 31.

Сущность изобретения состоит в повьш1ении быстродействия при выполнении операций над разрядами, а также при выполнении операции вычисления корня за счет введения возможности выборки констант из блока памяти программ с совмещением выполнения действия над ними, а также с введением возможности ветвления по группе условий.

Микропрограммный процессор работает следующим образом.

Выходы регистров 3 и 4 микрокоманд соответствуют определенным полям микрокоманд. Первый выход регистра 3 соответствует полю адреса перехода, второй - полю управления приемом на регистр 15 констант. Первьш выход регистра 4 представляет собой поле операций, второй - поле выбора источника модификации адреса микрокоманды, третий, четвертый и пятый выходы определяют itcuin, управляющие работой операционного блока 1, шее515

той выход представляет собой поле, управляющее работой внешней памяти, седьмой управляет работой мультиплексора 16.

Прием очередной микрокоманды из блока 2 микропрограммной памяти на первый 3 и второй 4 регистры микрокоманд производится синхронно с сигналами с выхода генератора 6, определяющими период следования микрокоманд, и по времени совпадает с задним фронтом этих сигналов. При обычном следовании микрокоманд на втором выходе первого регистра 3 микрокоманд присутствует сигнал логического О, которьш, поступая на первые входы элементов ИЛИ 7 и И 13, разрешает прием информации на второй регистр 4 микрокоманд и запрещает прием на регистр 15 констант.

При необходимости выборки из блока 2 микропрограммной памяти константы в К-1 микрокоманде на втором выходе первого регистра 3 микрокоманд выставляется сигнал логической 1, который sanperiaeT прием на второй регистр 4 микрокоманд и разрешает прием на регистр 15 констант. Таким образом в (К-1)-й микрокоманде на регистр 15 констант будет принята константа. Поскольку содержимое второго регистра 4 микрокоманд не изменяется, в (K-l)-i i микрокоманде выполняется функция, указанная в К-й микро команде. Это позволяет производить действия с константой не в (К-2)-й, а в (К-1)-й микрокоманде (фиг.З).

На регистр 12 связи по управляющему сигналу с четвертого выхода дешифратора 10 операций производится прием команды, выбранной по адресу, находящемуся на регистре 1I адреса, при этом второй мультиплексор 16 сигналом с седьмого выхода второго регистра 4 микрокоманд переключен таким образом, что на его выходе находится информация, поступающая из внешней памяти на информационный вход 27 процессора. Начало выборки команды из внешней памяти определяет сигнал обращения за командой, выдаваемой по окончании предыдущей команды с шестого выхода второго регист- . ра 4 микрокоманд на управляющий выход 26 процессора.

Следующим этапом вьшолнения команды является формирование адреса операнда, при этом вьшолняемые в

70346

микропрограмме действия зависят от вида адресации (прямая, относительная, косвенная), который определяется полем признака адресации команды. Разряды признака адресации поступают с выхода регистра 12 связи с блоками памяти на младшие разряды первого мультиплексора 5 по третьему входу,

Q а на его второй вход поступает управляющая информация с второго регистра 4 микрокоманд, которая подключает информацию с третьего входа на выход мультиплексора 5. Информация с выхо5 Дов первого мультиплексора 5 поступает на входы элементов ИЛИ 24, а на вторые их входы подается информлция с выхода первого регистра 3 микрокоманд, которая представляет собой

20 поле адреса перехода к следующей микрокоманде. Причем младшие разряды адреса перехода, по количеству равные разрядам признака адресации, должны быть О,- например 00101101000 (при

25 количестве разрядов поля признака адресации, равного трем). Результат логического сложения на выходах элементов ИЛИ 24 в зависимости от значения разрядов признака адресации

30 определяет одну из восьми ячеек блока 2 микропрограммной памяти. Таким образом организуется ветвление к группе ячеек блока 2 микропрограммной памяти в зависимости от вида -, признака адресации.

Формирование адреса операнда осуществляется в операционном блоке 1 и представляет собой выделение адресной части команды и передачу ее

40 на регистр 11 адреса (при прямой

адресации) либо сложение выделенной адресной части команды с одним из индексных регистров (при относительной адресации) и передачу результата

де также на регистр 11 адреса.

Выделение адресной части команды осуществляется путем логического умножения константы с количеством единичных битов, равным адресной час50 ти команды, на саму команду. Например, при 16-разрядной команде, когда адресной частью являются младшие 10 разрядов, осуществляется логическое умножение на константу

55 0000001111П1П1, в результате Чего старшие шесть разрядов обнуляются. При этом информация на третьем выходе второго регистра 4 микрокоманд определяет вид вьтолняемой операцион7I5I7034

itbiM блоком 1 функции (арифметическое сложение, логическое сложение и - . т.д.), информация на четвертом выходе онределяет адрес регистра операционного блока 1, в который записывается результат, а информация на пятом выходе второго регистра 4 микрокоманд определяет адреса операн

дов, учггствующих в выполнении указанной функции.

Адрес Операнда, полученный на сумматоре 28, поступает н а ннформа- цнонньй вход регистра 11 адреса и принимается на него при приходе иа управляющий вход сигнала нриема с первого выхода дешифратора 10 онера цшь

Для выполнения действий, онреде- . 1Яемых кодом операций команды, производится выход в начало микропрограммы выполнения текущей команды, для чего разряды кода операции, хранящиеся на регистре 12 связи с блоками памяти, ноступают через старшие разряды первого мультиплексора 5 ;1О третьему входу на первые входы элементов ГИГИ 24 группы. При этом на вторые входы элементов ИЛИ 24 поступ- пает адрес перехода с нулями в старших разрядах, по количеству равных коду операция. При б-разрядном коде (операции на выходах элементов ИЛИ 24 получается информация, определяющая зависимости от значения кода операции одну или 64 ячейки блока 2 микро программной памяти. Каждая из указанных 64 ячеек является началом микропрограммы выполнения одной из 64 команд, составляющих систему команд. образом, осуществляется ветвление одновремен1 О по большему числу 1)азрядов (в данном случае по 6).

При реализации системы команд про н,ессоров цифровых вычислительных машин наиболее сложными, ведущими к большим аппаратурным и временным затратам, представляются обычно оперции над разрядами, а также операция вычисления квадратного корня.

Операции над разрядами реализует запись О или 1 в опеределенный разряд ячейки блока внешней памяти либо п)исвоение значения определенного разряда ячейки внешней памяти признаку результата, либо запись признака результата в определенный разряд ячейки внешней памяти. При ыполн1;;нрп1 команд над разрядами

8

0

5

0

0

. 5

0

5

происходит изменение значения только одного разряда, значение остальных остается неизменным.

Рассмотрим алгоритм выполнения команды над разрядами на примере команды установки в 1 определенного разряда ячейки блока внешней памяти с сохранением неизменными значений остальных разрядов. Номер устанавливаемого, разряда и адрес ячейки внешней памяти, устаствующей в команде, задаются определенным образом в адресе операнда. Пусть, например, в команде адресация производится относительно первого индексного регистра, в котором записан код 01 01 000000000000. Пусть, например, код адресной части команды 0000000111. Адрес операнда формируется описанным образом, причем его старшие четыре разряда указывают номер разряда, который необходимо установить в 1, а младшие - адрес ячейки блока памяти, в который необходимо этот разряд установить в I. Таким образом, адрес операнда в результате сложение первого индексного регистра (один из регистров операционного блока I) с выделенной адресной частью команды нредставляет собой код 0100000000001II, где старшие четыре разряда определяют устанавливаемый разряд, а остальные - седьмую ячейку блока памяти.

В первой микрокоманде исполнения команды производится прием на регистр 12 связи с блоками памяти адреса операнда с сумматора 28, при этом второй мультиплексор 16 переключен в соответствующее состояние.

Во второй и третьей микрокомандах производятся прием по сигналу с шестого выхода дешифратора 10 старших четырех разрядов с регистра 12 на четырехразрядный счетчик 9, а также обнуление старших пяти разрядов адреса операнда. Обнуление старших пяти разрядов адреса операнда производится путем логического умножения константы с нулями в четырех старших разрядах на содержимое регистра 12 связи с блоками памяти, что осуществляется в операционном блоке I.

В четвертой и пятой микрокомандах производятся прием результата логического умножения, полученного на сумматоре 28, на регистр 11 адреса, обнуление регистра 15 констант, выдача сигнала обращения за операндом

915

по управляющему выходу 26, а также выдача управляющего сигнала на вход мультиплексора 16, переключая его для работы с информационного входа 27 процессора.

В шестой микрокоманде производятся прием выбранного из седьмой ячейки памяти операнда на регистр 12 dвя зи с блоками памяти, а также выдача дешифратором 10 операций сигнала на его второй выход.

Таким образом, к концу шестой микрокоманды информация с выхода счетчика 9 воздействует на дешифратор 19, возбуждая его пятый выход. С другой стороны, операция, выдаваемая с второго выхода дешифратора 10 операций, разрешает работу четвертого мультиплексора 18, поступая через второй элемент И 21 на его первый управляющий вход, а также переключает его по второму управляющему входу таким образом, что сигнал с пятого выхода дешифратора 19 поступает на установочный вход пятого разряда регистра 15 констант.

В результате указанных действий на регистре констант устанавливается код 0000010000000000.

В седьмой и восьмой микрокомандах производится логическое сложение содержимого регистра 12 связи с блоками памяти и информации, находящейся в регистре 15 констант. Например, если код в седьмой ячейке блока памяти был 0110001101110101, то после логического сложения на сумматоре 28 оказывается код 0110011101110101. Этот код является конечным результатом выполнения команды, который в девятой микрокоманде, будучи принятым с сумматора 28 на регистр 12, записывается обратно в седьмую ячейку блок внешней памяти под управлением сигнала с шестого выхода второго регистра 4 микрокоманд и на один из регистров 32 для хранения.

В девятой микрокоманде содержимое одного из регистров операционного блока 1, отведенного под счетчик команд, увеличивается на единицу, тем самым осуществляется подготовка к выборке из блоков внешней памяти следующей команды.

Прием адреса следующей команды на регистр 11 адреса и выборка команды по этому адресу осуществляются в десятой микрокоманде.

410

Реализация вычисления функции /х для значений х, лежащих в диапазоне 0,0-1,0, в предложенном микропрограм- мном процессоре строится на основе итерационного алгоритма. Этот алгоритм сводится к последовательному определению значений разрядов результата, который может быть представлен в виде

Q

V5E i q,2- , pii

5

0

5

0

5

0

5

0

5

где q - значение р-го разряда.

При этом осуществляется подбор q таким образом, чтобы выражение х р

Q (21q.,2) приближалось по своер р, t р

му значению к х, но оставалось мень- пшм X.

Определение очередного значения qp производится по знаку рАности Ур между значением х и соответствующим ему приближением х р. При этом, если Ур О, -то qp устанавливается равным 1, производится установка в 1 (р-2) разряда и установка в О (р-1) разряда результата; если , то q устанавливается равным О и производится установка в 1 (р-2) разряда результата (фиг.4).

При этом исходно подкоренное выражение находится в одном из регистров 32 операционного блока 1 (например, в регистре, обозначенном Рг1), а счетчик 9 обнуляется. Обнуление происходит путем передачи нулевой константы с регистра 15 через сумматор 28, мультиплексор 16 и регистр 12 на счетчик 9. При вьшолнении микропрограммы вычисления корня в циклах вырабатываются сигналы на третьем прямом и инверсном выходах дешифратора 10 операций, с помощью которых в соответствии с номером цикла вычислений (р) очередного разряда и в зависимости от знака разности вьтолняют- ся следующие действия.

Включаются третий и четвертый мультиплексоры. Это осуществляется за счет выдачи дешифратором 10 на третьем прямом выходе сигнала нулевого уровня. Он проходит через элемент И 21 на первый управляющий вход четвертого мультиплексора 18 и непосредственно поступает на второй управ- лякщий вход третьего мультиплексора 17, обеспечивая их включение. При появлении на третьем выходе дешифратора 10 сигнала нужного уровня на тре11151

тьем инверсном выходе вырабатывается сигнал высокого уровня.

Переключается четвертый мультиплексор 18 в режим работы по вторым (р-2) входам, выполняя в циклах установку в 1 Ср-2) разрядов регистра 15 констант. Это осуществляется после появ- лештя сигнала на третьем выходе дешифратора 10 за счет наличия единичных потенциалов на входах элемента И 22 в паузе до появления на входе элемента И-НЕ 23 положительного синхроимпульса с блока управления, по заднему фронту которого будет осуществляться прием следующей микрокоманды на регистры 3

и 4.

При положительной разности производится дополнительное переключение четвертого мультиплексора 18 для работы по первым р-м входам и осуществляется установка в 1 р-го разряда регистра 15 констант. Также при положительной разности (положительный знаковый разряд) производится переключение третьего мультиплексора 17 для работы по вторым (р-1)м входам и установка в О (p-l)-ro разряда регистра 15. Переключение мул1зти- плексора 18 осуществляется в связи с поступлением на его первьй управляющей вход потенциала низкого уровня с элемента И 22. Низкий уровень на входе элемента И 22 обеспечивается наличием совпадения единичных сигналов на входах И-НЕ 23, а именно: положительного сигнала с третьего инверсного выхода дешифратора 10, положительного синхросигнала с выхода блока управления и положительного знакового разряда с выхода сумматора 28, характеризующего положительную- разность.

При отрицательной разности производится пере1а1ючение третьего мультиплексора 17 по первому управляющеьгу входу знаковым разрядом сумматора 28 для работы по первым р-м входам и установка в О р-го разряда регистра 15.

Пример. Вычисление квадратного корня из числа 0.110001000000000

(тт) по описанному алгоритму. оч

Первые четыре микрокоманды (фиг.5) осуществляют выборку из блока 2 микропрограммной памяти нулевой константы и занесение ее через операционный

412

блок 1 и регистр 12 связи с блоками памяти на счетчик 9. В последующих трех микрокомандах производятся выборка из блока 2 микропрограммной памяти

константы 0010000000000000, перепись ее, например, на Рг2 (один из регистров 32 операционного блока 1) и перевод содержимого Рг2 в дополнительный

код. Далее производятся прибавление 1 к счетчику 9 за счет выработки сигнала на пятом выходе дешифратора 10 и переход к выполнению непосредственно циклов вычисления корня.

Таким образом, к началу выполнения первого цикла исходное состояние регистров и счетчика 9 следующее: Рг1 операционного блока - 0.1100010. 00000000; Рг2 операционного блока

l.Prl 0.110 0010 0000 0000

L2 iiiiQ oqqg oooo oqoo

ргТ O.TOO.OOIO 0000 0000 (результат положительный).

I .011.0000 0000 0000. 5.Прибавление 1 к Сч (+1Сч); Сч 0010.

Второй цикл. l.Prl 1.0000 1000000 0000

2 ijL2ii2 20o 0000 oooq Рг1 oToiT o 1 ооооо о оо о

(результат положительный).

Третий цикл. l.Prl 0.110 1000 0000 0000

.1

Рг1 О.ООО ОООО 0000 ОООО (результат положительный).

13

З.РгЗ - Рг2.

.0001100 0000 0000.

Четвертый цикл

0.0011 000 0000 0000. Пятый цикл.

0.001 1000 0000 0000

ргГ

Рг2 0.1 и

Шестой цикл.

0.0011100 0000 0000

.1 iiggii oooo ogog

ргГ i.oooiiTT

(результат отрицательный).

0.001 1110 0000 0000

o.

Рг1 Т.ООО iTll 1000 0000 (результат отрицательный),

Восьмой цикл.

Рг2

25

Рг1

1703414

0.001 nil 0000 0000

OiIJLL 2020 oo oooo

т.000 iTi1 ГТоо 0000

, (результат отрицательный).

10 4. -ИСч; Сч 1001 .

15 о,. gggg

ргТ Т.ооо пТТ

(результат отрицательный).

20 0.111.0000.0011.0000.

. Сдвиг влево Рг1; Рг1

O.OOi nil 1100 0000 Десятый цикл. 0.001

0«.1JUL l.OOO

Prl

1111 1100

oggo ggn iTi

0000

ggg

0000

0

5

0

(результат отрицательный).

Одиннадцатьш цикл.

0.001 1111 1110 0000

JLogg Prl i.oooTiTT iTTi iooo

Pr2 0.111

РгЗ

5

0

0.11 1 РгЗ в О 1 13-го 0000 0000 1100. Рг2.

1 1-го разряда, разряда РгЗ;

Двенадцатый цикл.

0.001 1111 1111 0000

-2oog gggg iigo

Prl 1.000 iTTi nn iioo

Pr2 0.111

5

Четырнадцатый цикл.

j:2 0000 оооо opii Рг1 Т. iPiTTi

(результат отрицательный),

Пятнадцатый цикл. I . Рг1 0.001 1111 Рг2

1 1 10 0.111 0000 0000 0001

11

Pri 1.000 11 (результат отрицательный).

РгЗ -- Рг2.

+1Сч; Сч 0000.

При условии равенства счетчика 9 нулю микропрограмма переходит в ветвь переписи окончательного результата.

0.111 0000 0000 0000 (-) с РгЗ

о

на регистр результата Рг1.

В предлагаемом процессоре достигнуто повьшение быстродействия при выполнении операций над разрядами и оне рации вычисления корня за счет использования выборки из блока памяти микрокоманд констант на регистр констант со специальными схемами установки, совмещения выборки константы С действиями над ней, осуществления ветвления микропрограмм одновременно по группе условий.

Формула изобретения

Микропрограммный процессор, содержащий блок памяти микрокоманд, первый и второй регистры микрокоманд, опера0

5

0

5

0

5

0

5 0

5

ционный блок, генератор тактовых импульсов, первый мультиплексор, дешифратор операций, элемент НЕ, первый элемент ИЛИ, первый элемент И, причем выходы первого и второго полей блока памяти микрокоманд соединены соответственно с информационными входами первого и второго регистров микрокоманд, выход генератора тактовых импульсов соединен с входом синхрониза- 1ЩИ операционного блока,с входом элемента НЕ, с первым входом первого элемента И, с входом синхронизации первого регистра микрокоманд, выход признака полей блока памяти микрокоманд которого соединен с вторым входом первого элемента И и первым входом первого элемента ИЛИ, выход которого соединен с входом синхронизации второго регистра микрокоманд, выходы поля внутренних микроопераций, поля адреса операнда, поля адреса регистра, поля кода операции которого соединены соответственно с входом дешифратора операции, входом адреса операции, входом адреса регистра, входом кода операции операционного блока, отличающийся тем, что, с целью повыше}П1я быстродействия, в него введены регистры констант, адреса и связи, с второго по четвертый мультиплексоры, счетчик, -блок элементов ИЛИ, дешифратор разрядов, второй элемент ИЛИ, второй и третш элементы И, элемент И-НЕ, причем информационный вход мнкропрог1)аммного процессора соединен с первым информационным входом второго мультиплексора, выход которого соединен с информационным входом регистра связи, выход старших разрядов которого соединен с информационным входом счетчика, информационный выход которого соединен с входом дешифратора разрядов и входом второго элемента ИЛИ, выход которого соединен с первым информационным входом первого мультиплексора, выход которого соединен с первым входом блока элементов ИЛИ, выход которого соединен с входом адреса блока памяти микропрограмм, выход воторого поля которого соединен с информационным входом регистра констант, выход которого соединен с первым информационным входом опера- 1Ц1ОННОГО блока, выход которого соединен с вторыми информационными входами первого и второго мультиплексоров, с информационным входом регистра адреса, выход которого является выходом адреса микропрограммного процессора, выход старшего разряда информационного выхода операционного блока соединен с адресньм входом третьего мультиплексора и с первым входом элемента И-НЕ, выход поля адреса перехода первого регистра ми- крокоманд соединен с вторым входом блока элементов ИЛИ, вькод первого элемента И соединен с входом синхронизации регистра констант, выход младших разрядов регистра связи сое- динен с третьим информационным входом первого мультиплексора, выход регистра связи соединен с вторым информационным входом операционного блока и с информационным выходом микропро- граммного процессора, выход поля выбора адреса второго регистра микрокоманд соединен с входом адреса первого мультиплексора, выход дешифратора разрядов соединен с информационным входами третьего и четвер1 ого мультиплексоров, выходы которых соединены соответственно с входами ус Ьанов- ки в О и установки в 1 регистра констант, первый выход дешифратора операций соединен с входом записи регистра адреса, второй выход дешифратора операций соединен с первыми входами второго и третьего элементов И, выходы которых соединены соответственно с входом стробирования и входом адреса четвертого мультиплексора, третий выход дешифратора операций соединен с вторым входом второго элемента И и входом стробирования третьего мультиплексора, с четвертого по шестой выходы дешифратора операций соединены соответственно с входом записи регистра связи, суммирующим входом счетчика, входом записи счетчика, выход генератора тактовых импульсов соединен с вторым входом элемента И-НЕ, выход которого соединен с вторым входом третьего элемента И, выходы поля внешних микроопераций и поля управления вторым мультиплексором второго регистра микрокоманд соединены соответственно с выходом внешних микроопераций микропрограммного процессора и с входом адреса второго мультиплексора, третий инверсный выход дешифратора операций соединен с третьим входом элемента И-НЕ, выход элемента НЕ соединен с вторым входом первого элемента ИЛИ.

фиг. 2

Я-я

i UKpOKwaHda.

taxod (лоеа упракления

Выход мвнента HCg

вяорт tbuai первом регистра ншсратнанв 3

tftnsHmt H/lin

Прием N-и

8ыжо9 глеменаа

н м

микроконан и

( ичкроа/гюнда

()-Я микрокоманде

Прие()-и пикротмандщ

Прием ffitp-u микрокоманды

| Микропроцессор | 1982 |

|

SU1037263A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммный процессор | 1981 |

|

SU1024927A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-10-23—Публикация

1987-06-29—Подача