ел

о

00 00 00

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство фазовой автоподстройки частоты | 1981 |

|

SU1091354A1 |

| ГЕНЕРАТОР ИМПУЛЬСОВ С АВТОПОДСТРОЙКОЙ ЧАСТОТЫ | 2004 |

|

RU2260904C1 |

| Цифровое устройство фазовой синхронизации | 1987 |

|

SU1462504A2 |

| Преобразователь угловых перемещений в код | 1977 |

|

SU693410A1 |

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| Цифровой синтезатор частот с частотной модуляцией | 1985 |

|

SU1293840A1 |

| Цифровой синтезатор частот | 1987 |

|

SU1510080A1 |

| Устройство автоподстройки фазы | 1987 |

|

SU1533002A1 |

| Цифровое устройство фазовой синхронизации | 1985 |

|

SU1327307A2 |

| Устройство для контроля аппарата магнитной записи | 1985 |

|

SU1283848A1 |

Изобретение относится к технике связи. Цель изобретения - повышение быстродействия при заданной точности автоподстройки. Устройство содержит цифровой фазовый детектор (ЦФД) 1, делители 2 и 6 частоты, элементы И 3 и 5, элемент задержки 4, формирователь 7 коротких импульсов, инвертор 8 и опорный генератор 9. В устройстве осуществляется смена позиций на выходе ЦФД 1 с отрицательной на положительную. Обе эти позиции образуют полный такт автоподстройки. В смежные периоды регулирования образуется непрерывная последовательность импульсов опорной частоты с "вычеркнутым" импульсом. За счет данного "вычеркивания" такт автоподстройки удлиняется на число "вычеркнутых" импульсов. Подсчет числа импульсов позволяет судить о величине периода регулирования и, следовательно, о частоте входного сигнала. Устройство по п. 2 формулы отличается выполнением ЦФД 1 в виде JK-триггера, дана его ил. 1 з.п. ф-лы, 3 ил.

Фиг.1

Изибретеиие относится к технике i связи и измерительной технике и М(;жет быть использова}1о в радиоприемных устройствах и системах контроля и из- мерения с целью перевода в код частоты входного сигнала.

Целью изобретения является повьппе- ние быстродействия при заданной точности автоподстройки.

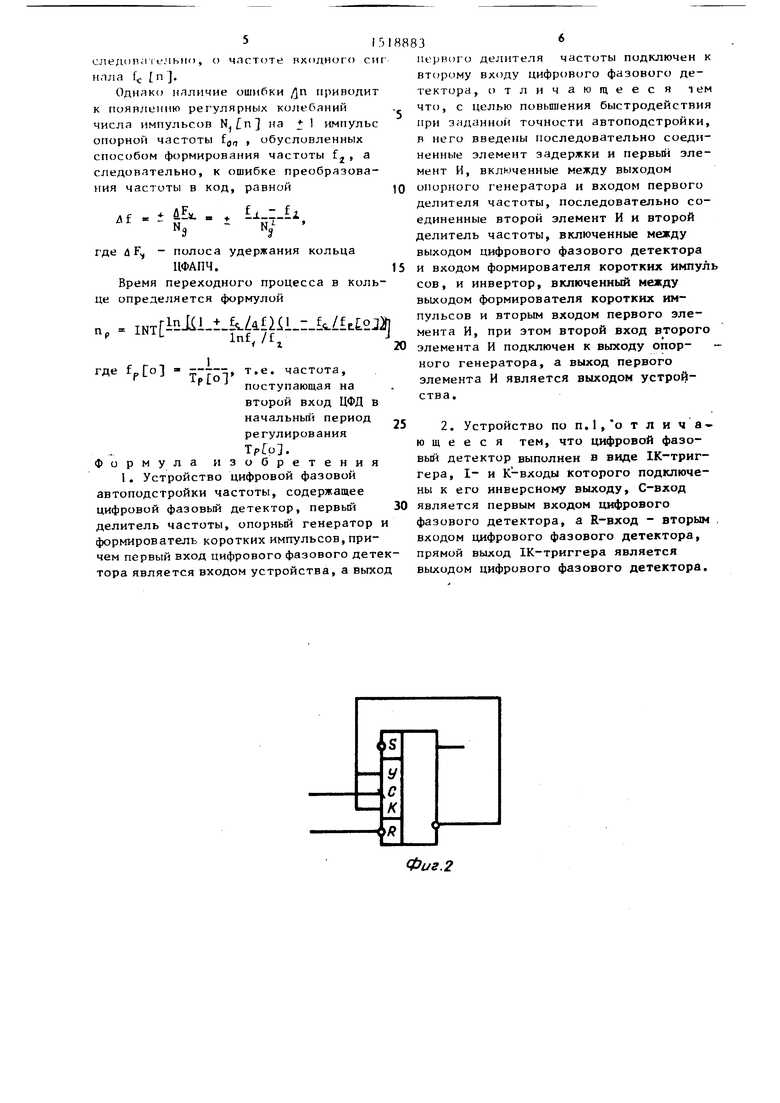

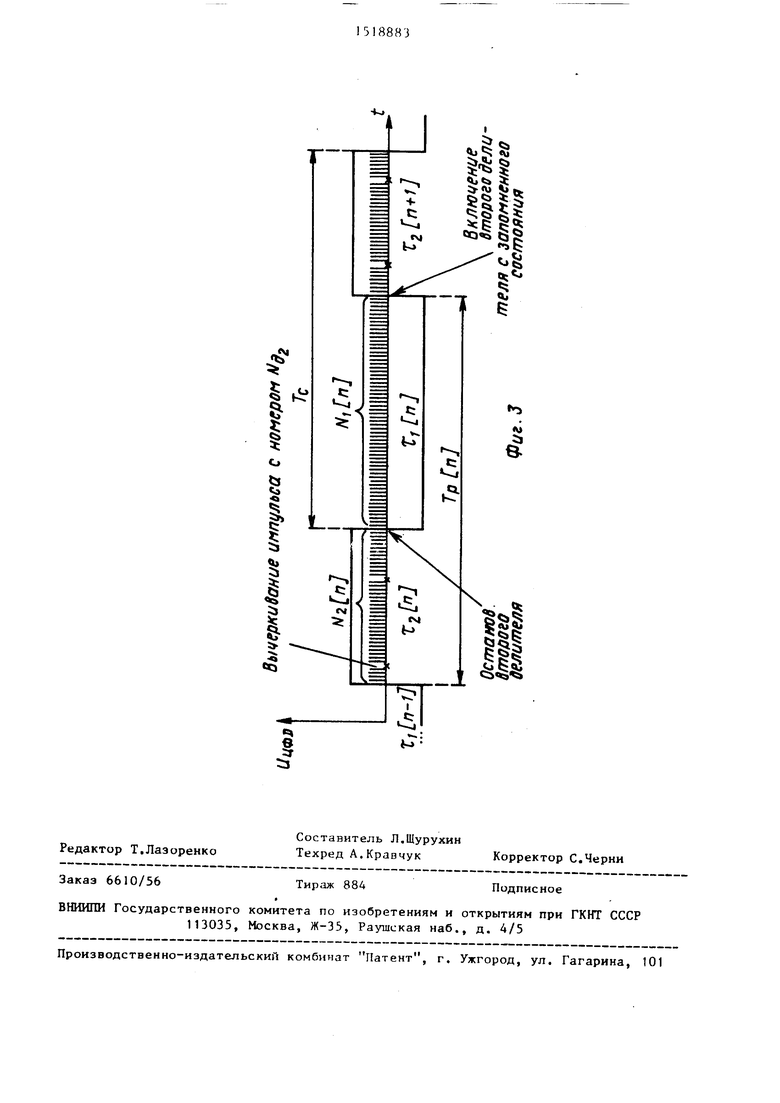

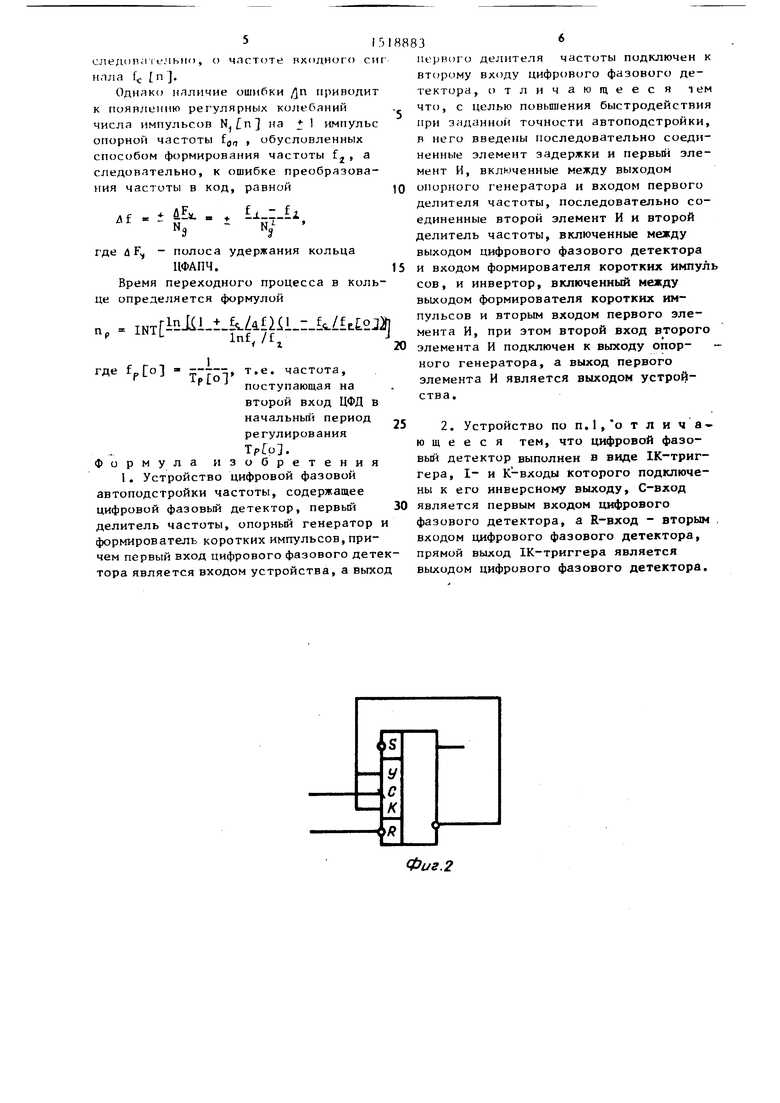

На фиг.1 представлена структурная электрическая схема устройства цифровой фазовой автоподстройки частоты; на фиг.2 - схема цифрового фазового детектора; на фиг.З - диаграмма рабо- ты устройства.

Устройство содержит цифровой фазовый детектор (ЦФД) 1,первьш делитель 2 частоты, первьо элемент ИЗ, элемент А задержки, второй элемент И 5, BTopo делитель 6 частоты, формирователь 7 коротких импульсов, инвертор 8 и опорньй генератор 9. ЦФД выполнен в . виде 1К-триггера.

YcTpoiicTBo работает следуюицш об- разом.

Сигнал с частотой fc , прошедший через усилитель-ограничитель (не показан) , поступает на первый вход ЦФД 1 , после чего последний переходит в нулевое состояние , которое идентифи цируется позицией Г , называемой отрицательной. Нуль на выходе ЦФД 1 закрывает второй элемент И 5, в результате чего импульсы опорной часоты с выхода опорного генератора 9 f, беспрепятственно проходят на первый делитель 2 частоты. После заполнения первого делителя 2 частоты до своего коэффициента деления N9 происходит смена позиции на выходе ЦФД 1 на положительную () элемент И 5 открывается, импульсы опорной частоты f проходят на второй делитель 6 частот1)1. После его заполне ния до своего коэ(М)ициента деления Nn формировате.чем 7 коротких импульсов через инвертор 8 запрещается прохождение этого последнего импульса на первый делитель 2 частоты. Таким образом, формируется вторая частота f , синхронизованная с частотой f оп -Элемент А задержки служит для компенсации задержки цепи, CCJCTO ящей из BTopui o элемента И 5, второго делителя 6 частоты, формирователя 7 коротких импульсов и первого элемента И 3 с тем, чтобы был вычеркнут именно импульс с номером N

Отрицательная позиция ЦФД и п(«1ожительная Т fiij образуют полный такт автоподстройки

Г.

где п - порядковый номер периода

регулирования.

За каждьп1 такт регулирования первый делитель 2 частоты отсчитывает N импульсов частоты f, и N импульсов частоты f2, общее количество которых равно

N. + N.

No

t 1 3

Второй делитель 6 частоты находится в бегущем режиме, а именно запоминает свое состояние на предыдущем такте автоподстройки и продолжает счет импульсов частоты ton на текущем такте. Это позволяет сформировать частоту Г не только синхронизованной с частотой f , но и самосинхронизованной - при стыковке между собой

rvучастков - в смежные периоды регулирования образуется непрерывная последовательность импульсов опорной частоты с вычеркнутым импульсом за номером NOJ .

За счет данного вычеркивания такт автоподстройки удлиняется на число вычеркнутых импульсов, которое Р..ННО

INT

Njt - НДп . N

NyjI

где 1NT - операция взятия целой

части числа; и п - О или 1 в зависимости от

состояния второго делителя 8 частоты на (п-1)-м такте регулирования.

Таким образом, период регулирования Тр на п-й момент времени можно записать

Т,Сп: N,,-i-(Nj-N,n)T +

+ (INT - N 1 - °

, (INT .п)Т,,.

где Т,

N/1 - 1

1

° , Подсчет числа импульсов N, п позволяет однозначно судить о величине периода регулирования и.

следс)п;ггелы1), о част(;те входного синала ff I п .

Однако наличие ошибки приводит к появлению регулярных колебаний числа импульсов на 1 импульс опорной частоты f , обусловленных способом формирования частоты f, а следовательно, к ошибке преобразования частоты в код, равной

Л

uEv.

Na

NO

где л F - полоса удержания кольца

ЦФАПЧ.

Время переходного процесса в кольце определяется формулой

, . INT i2Jii-i-kZ4flii.I k/ftLoJ

f г 1 где - т.е. частота,

поступающая на второй вход ЦФД в начальньй период регулирования ТрГо. Формула изобретения

первого делителя частоты подключен к второму входу цифрового фазового детектора, отличающеес я i ем что, с целью повышения быстродействия нри заданной точности автоподстройки, в него введены последовательно соединенные элемент задержки и первый элемент И, включенные между выходом опорного генератора и входом первого делителя частоты, последовательно соединенные второй элемент И и второй делитель частоты, включенные между выходом цифрового фазового детектора и входом формирователя коротких импуль сов, и инвертор, включенный между выходом формирователя коротких импульсов и вторым входом первого элемента И, при этом второй вход второго элемента И подключен к выходу опорного генератора, а выход первого элемента И является выходом устройства.

является первым входом цифрового

фазового детектора, а R-вход - вторым , входом цифрового фазового детектора,

iS

у с к

Фиг.2

Редактор Т.Лазоренко

Составитель Л.Щурухин Техред А.Кравчук

Заказ 6610/56

Тираж 88А

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-33, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г, Ужгород, ул. Гагарина, 101

Корректор С.Черни

Подписное

| Системы фазовой автоподстройки частоты с элементами дискретизации/ Под ред | |||

| Шахгильдяна В.В | |||

| М.: Связь, 1979, с | |||

| Транспортер для перевозки товарных вагонов по трамвайным путям | 1919 |

|

SU102A1 |

Авторы

Даты

1989-10-30—Публикация

1987-11-06—Подача