113

Изобретение относится к вычислительной технике и может быть использовано в контролируемых устройствах для сложения чисел с различными порядками.

Цель изобретения - повышение эффективности контроля.

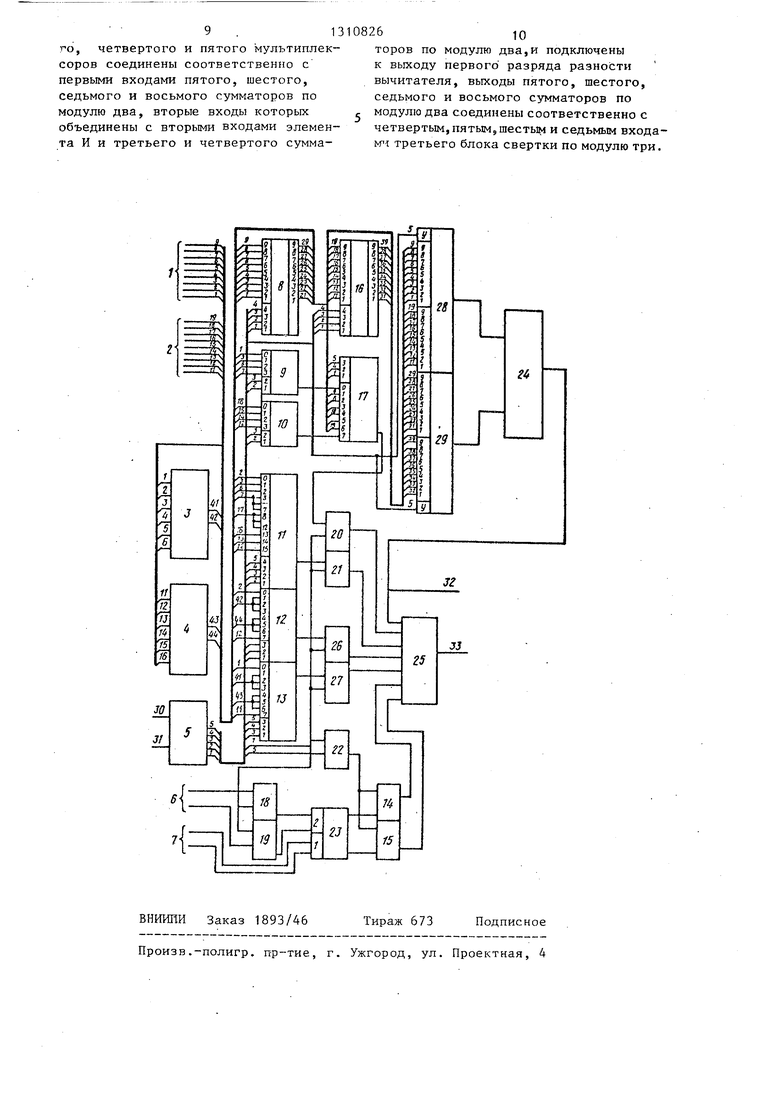

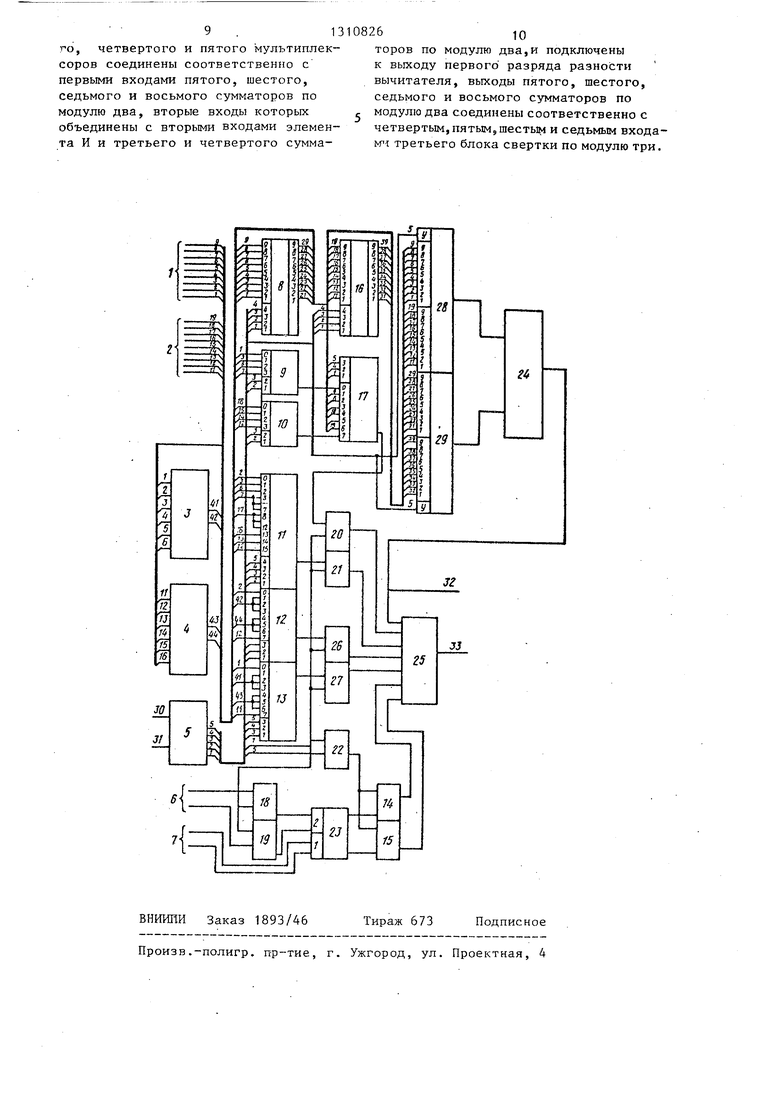

На чертеже представлена схема устройства для сложения операндов с плавающей точкой с контролем.

Устройство для сложения операндов с плавающей точкой с контролем содержит входы 1 и 2 мантисс первого и второго операндов устройства, первый и второй блоки 3 и 4.свертки по модулю три, вычитатель 5, входы 6 и 7 контрольных кодов первого и второго операндов устройства, первый сдвигатель 8, первый - пятый мультиплексоры 9-13, первый и второй сумматоры 14 и 15 по модулю два, второй сдвигатель 16, шестой мультиплексор 17, сумматоры 18-21 по модулю два с третьего по шестой соответственно, элемент И 22,-сумматор 23 по модулю три, позиционный сумматор 24, третий блок 25 свертки по модулю три, седьмой и восьмой сумматоры 26 и 27 по модулю два, первый и второй кбммута- торы 28 и 29, входы 30 и 31 порядков первого и второго операндов.устройства, выход 32 результата устройства и выход 33 ошибки устройства.

Устройство для сложения операндов с плавающей точкой с контролем работает следующим образом.

В начальный момент времени через входы 1 и 2 устройства заносятся мантиссы чисел А и В соответственно. Они представлены в обратном коде и содержат разряды с 1-го по 8-й знаковый, 1-е разряды - младшие. Через входы 6 и 7 устройства заносятся коды остатков по модулю три чисел А и В, являющиеся контрольными кодами этих чисел. Через входы 30 и 31 устройства на входы вычитателя 5 поступают коды порядков чисел В и А. Вычитатель 5 определяет разность порядков в дополнительном коде (вычитается порядок числа А). Эта разность определяет величину сдвига мантисс чисел А и В с целью выравнивания их порядков. Знак разности ЗнР определяет, какая из мантисс чисел А или В должна быть сдвинута. В случае ЗнР 0 дополнительный код разности совпадает с прямым кодом, а меньшим порядком обладает число А,поэтому его ман62

тисса должна быть сдвинута влево. Код разности (без знака) поступает на вход величины сдвига первого сдви- гателя 8, на информационный вход ко- торого подается мантисса числа А. Первый сдвигатель 8 осуществляет сдвиг на величину, определяемую прямым кодом разности порядков (высвобождаемые позиции заполняются значениями знакового разряда).

В случае меньшим порядком обладает число В, мантисса которого для сдвига влево поступает с входа 2 на информационный вход второго сдвигателя 16. Для выравнивания порядков мантиссу числа В необходимо сдвинуть на величину прямого кода разности порядков. В этом случае прямой код отличается от дополнительного

и равен его инверсии, увеличенной на единицу младшего разряда . Поэтому код разности порядков (без знака) поступает с выхода вычитателя 5 на инверсный вход величины сдвига второго сдвигателя 16, ас его выхода снимается мантисса числа В,сдвинутая влево на одну позицию меньше требуемого (высвобождаемые позиции заполняются значениеми знакового разряда) . Мантиссы чисел А и В до и

после сдвига, снимаемые соответственно с входов 1 и 2, с выхода сдвигателя 8 поступают соответственно на первый и второй информационные входы коммутатора 28, на второй информационный вход коммутатора 29, на первый информационный вход которого поступает информация с выхода сдвигателя 16 со сдвигом влево на один разряд и распространением знака. На управляющие входы коммутаторов 28 и 29 поступает значение знака разности с выхода вычитателя 5. Полученные величины суммируются на позиционном сумматоре 24, с выхода которого мантисса результата поступает на выход 32 устройства .

Контроль описанных выше действий выполняется следующим образом.

Контрольный код по модулю три содержит минимально два разряда: пер-, вый или нечетньй (т.е. стоящий на нечетной позиции) и второй или нечет- ный (т.е. стоящий на четной позиции). Нечетный разряд имеет вес 2°или 1, а четный разряд - вес 2 или, что то же самое по модулю три, -1. Аналогичные веса по модулю три имеют и нечет13108264

Функция f3 реализуется в устройст- ла.ве третьим мультиплексором 11, на

Таким образом, остаток от деления информационные входы которого, с ну- двоичного числа на три, т.е. его конт- левого по пятнадцатый, Поступают со- рольный код, может быть определен как ответственно второй, третий, шестой сумма единичных нечетных разрядов, и пять раз седьмой разряды числа А, взятых со знаком плюс, и единичных пять раз седьмой и по одному разу четных разрядов со знаком минус. шестой, третий и второй разряды чис- В такой сумме пара рядом стоящих еди- ла В. На управляющие входы третьего ничных (или имеющих одинаковые значе- р мультиплексора 11 поступают четыре ния) разрядов взаимно компенсирует старших разряда разности порядков: свои значения. Следовательно, конт- ЗнР, 4Р, ЗР и 2Р.

рольный код заполняемой части равен Функция f может быть представ- нулю при сдвиге на четное количест- лена через функции fj- и , являю- во позиций и равен единице.в против- j щиеся ее частными случая, которые

,ном случае. Поскольку при сдвиге чис- реализуются первым и вторым мульти- ла веса его разрядов изменяются, то плексорами 9 и 10, на информацион- определяемые контрольные коды перво- ные входы которых, с нулевого по начально вычисляются относительно третий, поступают соответственно весов числа до сдвига.2о первый, третий, пятьш и седьмой

Четьфехразрядный контрольньш код разряды числа А и восьмой, шестой, отбрасьшаемых разрядов, дополненный четвертый и второй разряды числа В, для вариантов сдвига на нечетное На управляющие входы мультиплек- количество позиций значениями зна- соров 9 и 10 поступают разряды разков чисел (т.е. включающий в себя 25 ности порядков ЗР и 2Р с выхода вычи- контрольный код заполняемой части тателя 5. числа), составлен разрядами-функци- Функция реализуется шестым

ями f ,2 ,f2 весами по модулю мультиплексором 17, на информацион- три -1, 1, -1 и 1 соответственно. ные входы которого, с нулевого по Функция f реализуется в устройст- д седьмой, поступают соответственно

ве мультиплексором 13, на информаци- значения функции t с выхода первого онные входы которого с нулевого по мультиплексора 9, девятый, (знаковый) седьмой поступают соответственно пер- и дважды восьмой разряды числа А, вый разряд числа А, трижды первьй дважды и один раз девятый (знако- разряд S1 кода с выхода первого бло- вый) разряды числа В и значение функ- ка 3 свертки по модулю три, трижды ции { с выхода второго мультиплек- первый разряд Q1 кода с выхода вто- сора 10. На управляющие входы шес- рого блока 4 свертки по модулю три того мультиплексора поступают разря- и первый разряд числа В.ды разности порядков ЗнР, 4Р и 1Р.

S1 и S2 - первый и второй разряды Q Сдвиг числа на четное количест- результата сверткзя по модулю три во позиций сохраняет веса его разря- шести младших разрядов числа А:S2S1 дов по модулю три, сдвиг числа на /А/6,5,4,3,2,1//mod 3, аналогично нечетное количество позиций меняет Q2Q1 /В/ 6,5,4,3,2,1//mod 3. знак весов его разрядов на противопоФункция {, реализуется в устройст-45 ложный, что равносильнр инвертиро- ве четвертым мультиплексором 12, на ванию контрольного кода. Для учета информационные входы которого, с возможного изменения знака .весов нулевого по седьмой, поступают соот- разрядов чисел значения функций f , ветственно второй разряд числа А, 3, 2 ч поступают на первые вхо- трижды второй разряд S2 кода с вько- 50 сумматоров 20-27 по модулю два а первого блока 3 свертки по модулю соответственно. На вторые входы этих

I три, триязды второй разряд Q2 кода сумматоров по модулю два поступает с вькода второго блока 4 свертки по разряд IP с выхода вычитателя 5, что модулю три и второй разряд числа В. обеспечивает при трансляцию

На управляющие входы четвертого 55 ФУНКЦИЙ на выходы сумматоров по мо- и пятого мультиплексоров 12 и 13 пос- ДУЛю два без изменений, а при тупают три старших разряда разности (что соответствует сдвигу числа на порядков: ЗнР, 4Р и ЗР, с выхода вы- нечетное количество позиций) - почитателя 5.лучение инверсий этих функций.

Ш

15

25

Аналогично первый и втброй разряды контрольного кода числа А поступают с входа 6 контрольного кода первого операнда на первые входы третьего и четвертого сумматоров 18 и 19 по модулю два, которые пропускают контрольный код на выходы без изменения или инвертируют его соответственно при нулевом и единичном значениях разряда IP, заведенного на вторые входы сумматоров по модулю два с младшего выхода вычитателя 5.

Полученный код с выходов третьего и четвертого сумматоров 18 и 19 по модулю два поступает на вход сумматора 23 по модулю три. На другой его вход подается контрольный код числа В с входа 7 контрольного кода второго операнда. Сумматор 23 по модулю три формирует контрольный код суммы чисел А и В для случая сдвига числа А (без учета отбрасываемых и заполняющих знаковых разрядов).

На входы элемента И 22 поступают ЗнР и младший IP разряды разности порядков с выхода вычитателя 5. Конъюнкция этих разрядов принимает значение нуля в случае сдвига чисел на четное количество позиций (когда веса по модулю три разрядов чисел и по контрольным кодам не изменяются), а также при сдвиге числа А.

В указанных случаях первый и второй сумматоры 14 и 15 по модулю два (управляемые по вторым входам конъюнкцией разрядов с вькода элемента И 22) транслируют через вторые входы код с выходов сумматора 23 по модулю три на выходы без изменения.

Выход элемента И 22 принимает единичное значение в случае сдвига числа В на нечетное количество по- зиций. В этом случае контрольный код суммы чисел А и В равен инверсии кода на выходе сумматора 23 по модулю три, что обеспечивается прохождением кода через сумматоры 14 и 15 по модулю два.

Контрольный код суммы чисел с выходов первого и второго сумматоров 14 и 15 по модулю два и контрольный код отбрасьтаемьк и заполняющих разрядов с выходов пятого, шестого, седьмого и восьмого сумматоров 20-27

по модулю два поступают на входы.бло- 55 которого является ка 25 свертки по модулю три. На дру- устройства, о т л

имеет четное колич При правильной раб свертка по модулю чисел, заведенных рольных кодов сутлм ваемых и заполняющ ня нулю. Инверсное начает подключение дов контрольных ко ных и наоборот, чт вычитание этих код

Выработка на вы свертки по модулю ного от нулевого, неисправность устр да блока 25 поступ устройства.

30

35

20 Формула из

Устройство для дов с плавающей то содержащее вычитат сумматор, два комм сдвигатель, три бл дулю три к суммат причем входы манти рого, операндов уст соответственно с п информационными вх мутатора, выход к с входом первого ционного сумматор является выходом ва, входы порядко операндов которог ветственно с вход уменьшаемого вычи ка которого соедин входами первого и ров, выход разн соединен с входо га первого сдвига ного кода второго с входом первого тора по модулю три

ман ус с второго блоков св три, выход позици соединен с первым блока свертки по м

40

45

50

шести разрядов рого операндов соответственно

гой вход блока 25 свертки по модулю три подается код суммы чисел А и В с выхода сумматора 24 (этот код

имеет четное количество разрядов). При правильной работе устройства свертка по модулю три кода суммы чисел, заведенных инверсно контрольных кодов сутлмы чисел и оТ брасы- ваемых и заполняющих разрядов рав- ня нулю. Инверсное соединение означает подключение нечетных разрядов контрольных кодов на место четных и наоборот, что обеспечивает вычитание этих кодов.

Выработка на выходе блока 25 свертки по модулю три кода, отличного от нулевого, указывает на неисправность устройства. Код с выхода блока 25 поступает на выход 33 устройства.

20 Формула изобретения

5

5 которого является устройства, о т л

0

5

Устройство для сложения операндов с плавающей точкой с контролем, содержащее вычитатель, позиционный сумматор, два коммутатора, первый сдвигатель, три блока свертки по модулю три к сумматор по модулю три, причем входы мантисс первого и второго, операндов устройства соединены соответственно с первым и вторьм информационными входами первого коммутатора, выход которого соединен с входом первого слагаемого позиционного сумматора, выход которого, является выходом результата устройства, входы порядков первого и второго операндов которого соединены соответственно с входами вычитаемого и уменьшаемого вычитат еля, выход знака которого соединен с управляющими входами первого и второго коммутаторов, выход разности вычитателя соединен с входом величины сдвига первого сдвигателя, вход контрольного кода второго операнда соединен с входом первого слагаемого сумматора по модулю три, входы младших

мантисс первого и вто- устройства соединены с входами первого и второго блоков свертки по модулю три, выход позиционного сумматора соединен с первым входом третьего блока свертки по модулю три, выход

выходом .ошибки ичающееся

0

5

0

шести разрядов рого операндов соответственно

тем,- что, с целью повышения эффек- тичности контроля, оно содержит второй сдвигатель, элемент И, шесть

,

мультиплексоров и восемь сумматоров по модулю два, причем информационные входы первого мультиплексора соединены соответственно с входами четырех младших разрядов мантиссы первого операнда устройства,входы мантисс первого и второго операндов устройства соединены соответственно с информационными входами первого и второго сдвигателей, вход величины сдвига второго сдвигателя соединен с входом величины сдвига первого сдвигателя,выход второго сдвигателя соединен со сдвигом на один разряд в сторону младших разрядов с первым информационным входом второго коммутатора, выход и второй информационный вход которого соединены соответственно с входом второго слагаемого позиционного сумматора и с выходом первого сдвигателя, вьгходы разрядов сумматора по модулю три соединены соответственно с первыми входами первого и второго сумматоров по модулю два, вьгходы которых сое- динены соответственно с вторым и третьим входами третьего блока свертки по модулю три, выход знака вычитате- ля соединен с первым входом элемента И, выход которого соединен с вторыми входами первого и второго сумматоров по модулю два, выходы второго и третьего разрядов разности вычитателя соединены соответственно с первым и вторым управляющими входами пер- Бого, второго и третьего мультиплексоров, третий и четвертый управляющие входы третьего мультиплексора соединены соответственно с выходами четвертого разряда разности и знака вычитателя соответственно, вьгходы третьего и четвертого разрядов разности и знака которого соединены соответственно с управляющими входами четвертого и пятого мультиплексо- ров, управляющие входы шестого мультиплексора соединены соответственно с выходами первого и четвертого раз. рядов разности и знака вычитателя, входы разрядов контрольного кода первого операнда соединены соответственно с первыми входами третьего и четвертого с т маторов по модулю два, выходы которых соединены соответствено с входами разрядов второго слагае мого сумматора по модулю три, информационные входы второго мультиплексора соединены соответственно с входами восьмого, шестого, четвертого

5

,jj л 25 Q.. Q д -

и второго разрядов мантиссы второго операнда устройства, входы второго, третьего и шестого разрядов мантиссы первого операнда устройства соединены соответственно с первым,вторым и третьим информационными входами третьего мультиплексора, вход седьмого разряда мантиссы первого операнда устройства соединен с информационными входами с четвертого по восьмой третьего мультиплексора, информационные входы с девятого по тринадцатый которого соединены с входом седьмого разряда мантиссы второго операнда устройства, вхйды шестого, третьего и .второго разрядов мантиссы второго операнда которого соединены соответственно с информационными входами с четырнадцатого по шестнадцатый третьего мультиплексора, первые информационные входы четвертого и пятого мультиплексоров соединены соответственно с входами второго и первого разрядов мантиссы первого операнда устройства, выходы первого и второго разрядов первого блока свертки по модулю три соединены с вторым, третьим и четвертым информационными входами соответственно пятого и четвертого мультиплексоров, пятый, шегтой и седьмой информационные входы которых соединены соответственно с выходами первого и второго разрядов второго блока свертки по модулю три5 восьмые информационные входы четвертого и пятого мультиплексоров соединены соответственно с входами второго и первого разрядов мантиссы второго операнда устройства, выход первого мультиплексора соединен с первым информационным входом шестого мультиплексора, второй информационный вход которого соединен с входом девятого разряда мантиссы первого операнда устройства, вход восьмого разряда мантиссы первого операнда устройства соединен с третьим и четвертым информационными входами шестого мультиплексора, пятый и шестой информационные входы которого объединены и соединены с входом восьмого разряда мантиссы второго операнда устройства, седьмой и восьмой информационные входы шестого мультиплексора соединены соответственно с входом девятого разряда мантиссы второго операнда устройства и с выходом второго мультиплексора, выходы шестого, третье9 ,13

го, четвертого и пятого мультиплексоров соединены соответственно с первыми входами пятого, шестого, седьмого и восьмого сумматоров по модулю два, вторые входы которых объединены с вторыми входами элемента И и третьего и четвертого сумма1082610

торов по модулю два,и подключены к выходу первого разряда разности вычитателя, выходы пятого, шестого, седьмого и восьмого сумматоров по с модулю два соединены соответственно с четвертым, пятым, шестым и седьмым входа- M -t третьего блока свертки по модулю три.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения-вычитания чисел с плавающей запятой | 1991 |

|

SU1784971A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| УСТРОЙСТВО СОВМЕСТНОГО КОДИРОВАНИЯ ГРАНИЦ ПРИ ИНТЕРВАЛЬНЫХ ВЫЧИСЛЕНИЯХ | 2012 |

|

RU2497180C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ СОВМЕСТНО ХРАНИМЫХ ГРАНИЦ ПРИ ИНТЕРВАЛЬНЫХ ВЫЧИСЛЕНИЯХ | 2012 |

|

RU2497179C1 |

| Устройство для обработки данных | 1987 |

|

SU1513443A1 |

| Устройство для суммирования нормализованных чисел с плавающей запятой | 1987 |

|

SU1418704A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Устройство для быстрого преобразования Фурье | 1988 |

|

SU1524066A1 |

| Устройство для деления | 1990 |

|

SU1742815A1 |

| Арифметическое устройство для вычисления коэффициентов Фурье | 1986 |

|

SU1388893A1 |

Изобретение относится к вычислительной технике и может быть использовано в контролируемых устройствах для сложения чисел с различными порядками. Целью изобретения является повышение эффективности контроля. Поставленная цель достигается тем, что устройство, содержащее блоки свертки по модулю три, вычитатель, сдвигатель, сумматор по модулю три, позиционный сумматор и коммутаторы, содержит мультиплексоры, сумматоры по модулю два, сдвигатель и элемент И с соответствующими связями. 1 ил. 00 1чЭ 05

| Вычислительное устройство | 1979 |

|

SU885994A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Бетонный полый камень | 1925 |

|

SU2366A1 |

| Техническое описание, ч | |||

| З.М., 1983, с | |||

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

Авторы

Даты

1987-05-15—Публикация

1986-01-31—Подача