сл

ГС

о сд

4i

Изобретение относится к телевизионной технике и может быть использовано в измерительных системах, основанных на коррелятщонном приеме сиг- налов.

Целью изобретения является повьше- ние точности вычисления корреляционной функции при обработке сигнала изобретения.

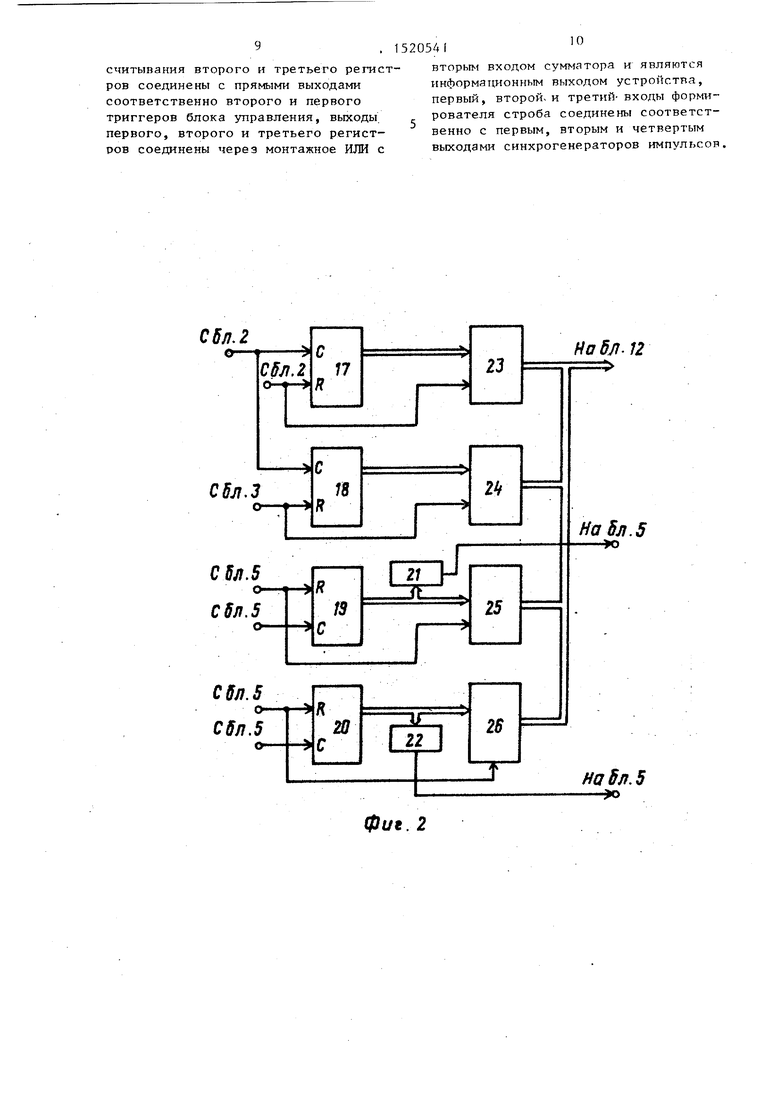

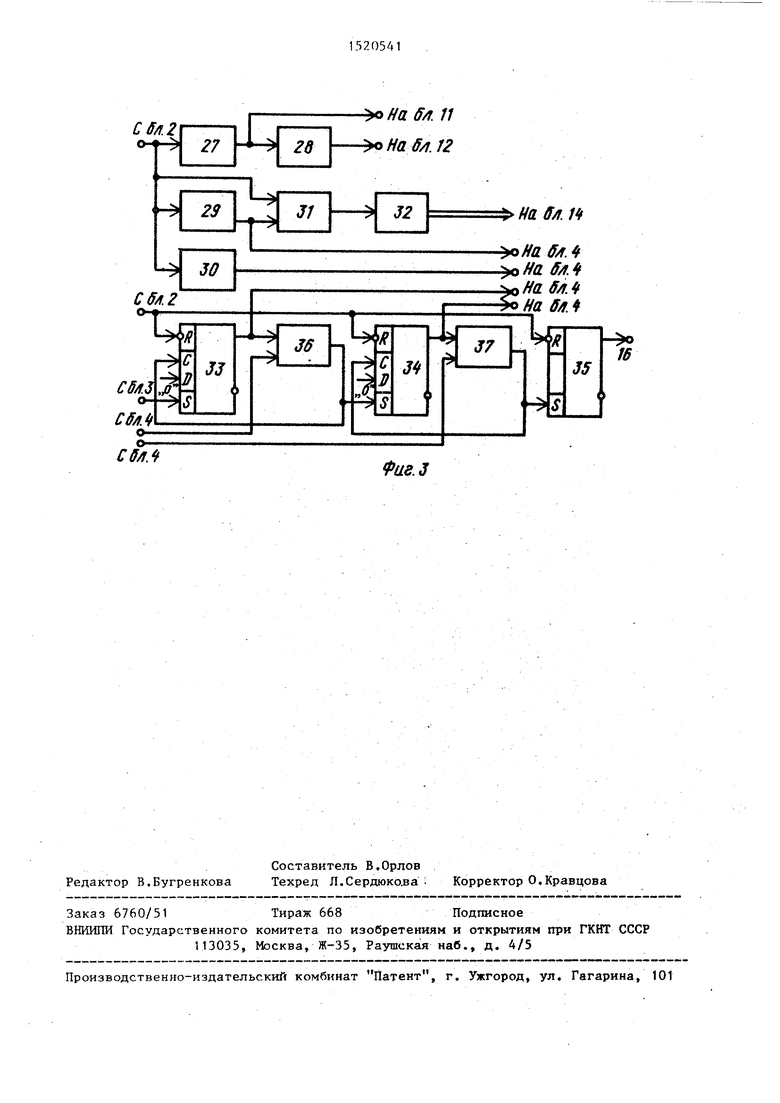

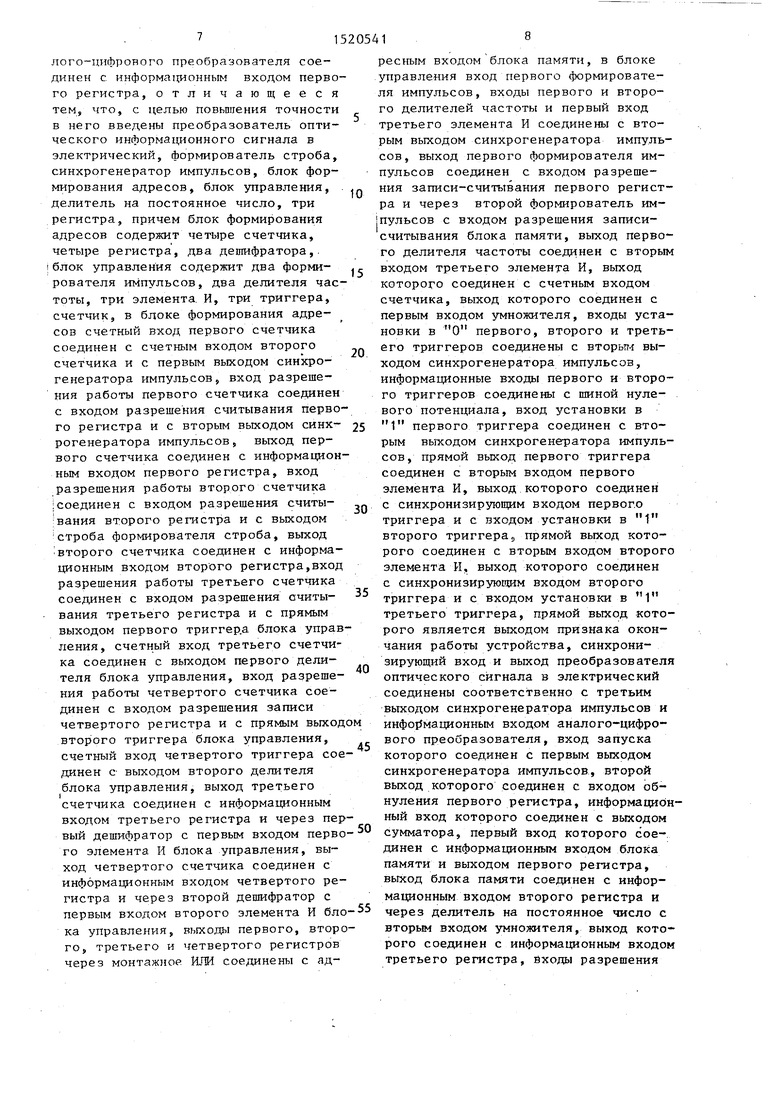

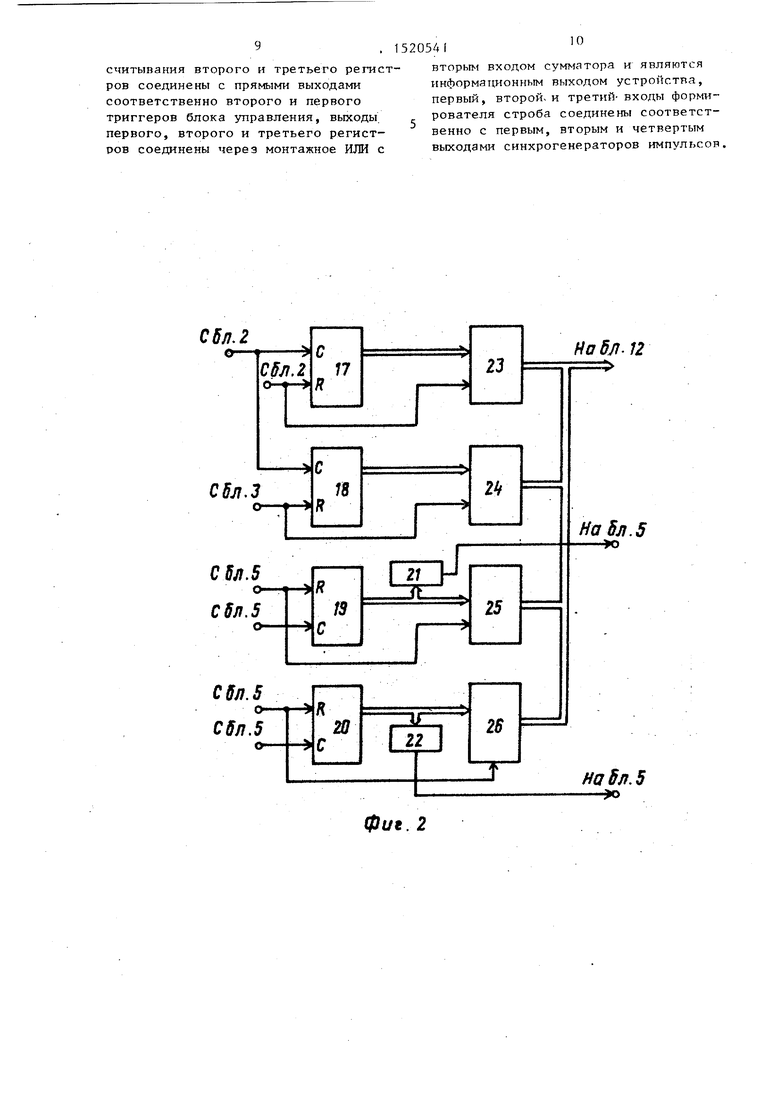

На фиг. 1 изображена структурная схема видеопроцессораi на фиг. 2 - структурная схема блока адресацииi на фиг. 3 - структурная схема блока управления.

Устройство содержит преобразователь 1 оптического информационного сигнала в электрический, синхрогене- ратор 2 импульсов, формирователь 3 строба, блок 4 формирования адресов, .блок 5 управления, аналого-цифровой преобразователь (А1Ш) б, регистры 7-9, сумматор 10, регистр 11, блок 12 памяти, делитель 13 на постоянное число, умножитель 14, информационный выход 15, выход 16 останова. Блок 4 адресов содёртшт счетчики 17-20, дешифраторы 21 и 22 и регистры 23-26.

Блок 5 управления содержит формирователь 27 и 28 импульсов, делители 29 и 30 частоты, элемент И 31, счетчик 32, триггеры 33-35, элементы И 36 и 37.

Синхрогенератор 2 является типовы узлом телевизионной системы, обеспе- чиваюпшм выдачу синхросигналов принятого телевизионного стандарта.

Формирователь 3 строба выполнен по типовой схеме генератора сигнала Окошко.

Умножитель 14 выполнен на основе программируемого постоянного запоминающего устройства (ППЗУ),

Устройство работает следующим образом,.

Наиболее растространенным методом вычисления корреляционной функции на практике при обработке сигнала изображения в телевизионных системах является прямой множительный метод, Корреляционная функция при этом вы числяется по формуле

R(,a) f; Т U,(i,j) -,

,

J - 1),

где lJ,(i,j), 11(1,j) - дискретные

двумерные сигнальные массивы текущего и эталонного изображений размером М X М элементов. На практике размер эталона зачастую можно ограничить меньшим числом К элементов (К М) J

i,j - номер элементов массивов изображений по горизонтали и вертикали. При сквозной нумерации можно использовать одну переменную ij

s, г - параметры смещений эталона относительно изображения по горизонтали и вертикали.

Как видно из формулы, для вычисле- ния корреляционной функции необходимо пронумеровать элементы сигнала, иметь мгновенные значения сигнала и эталона и., (i) и ), осуществить перемножение величин Ui(i) и U2(i) и накопление сумм по всему массиву изображений.

Процессор обеспечивает выполнение всех этих операций по обработке сигнала изображения объекта за один кадр телевизионной развёртки, В промежутке между активными областями телевизионной развертки (время осуществления КСИ) регистр 11 обнулен по вьгходу. Одновременно счетчик 17 открыт для счета тактовых импульсов (ТИ), а выход регистра 23 подключен к адресному выходу блока 4 адресации (выхода регистров 24-26 в третьем состоянии), В. каждом пе риоде ТИ формирователи 27 и 28 вырабатывают сигналы соответственно записи информации в регистр 11 и сигнал записи считывания для блока 12, Поскольку вход обнуления регист{эа 11 является приоритетнь1м по сравнению с входом синхронизации, во время существования КСИ, управление по входу синхронизации отсутствует. Сигналом.Запись/считывание в каждую из i-ячеек блока 12 (по каждому из адресов) будет записано числ.о О. К началу активной части телевизионной развертки ВП оказывается обнуленным.

Во время активной области телевизионной развертки преобразователь 1 преобразует оптический сигнал на своем входе в электрический. Синхронизация работы преобразователя осуществляется синхрогенератором 2. Bи-. деосигнал с выхода телевизионного датчика преобразуется А1Щ 6 в цифровой код, поступающий на информационный вход регистра 7.

Строб, вырабатьгааемый формирователем 3 строба, открывает регистр 7

3 1

для прохождения информации на вход сумматора 10. Однонременно строб разрешает счет тактовых импульсов счетчику 18 и подключает к адресному выходу блока 4 выход регистра 24. Вс элементы разложения в границах строба нумеруются. Так же как и во время КСИ, в каждом из периодов следования тактовых импульсов существуют сигнал синхронизации регистра 11 и записи/ считывания блока 12. Двоичный код с выхода А1Щ 6 (который также работает синхронно с частотой следования элементов разложения) проходит через регистр 7, сумматор 10 (стробом включен в режим Ug UBHX f.e. А+0), записьшается в регистр 11 сигналом с выхода формирователя 27 и в ячейку блока 12 с адресом, сформированным блоком 4 по сигналу с формирователя 28.

К окончании строба размером М х М элементов разложения в ячейках памяти с номерами от i О до i М х М будет записан двоичный код, соответствующий распределению размаха видеосигналов внутри строба.

Сигнал окончания кадровой составляющей строба выхода формирователя 3 строба устанавливает в единичное состояние триггер 33, обнуленный в начале кадра кадровым синхроимпульсом. Этот единичный сигнал открывает для )Счета счетчик 19 и подключает к выходной инне блока 4 регистр 25. Вы- .числение корреляционной функции сигнала, находящегося внутри строба, происходит .следующим образом. Последовательность тактовых импульсов преобразуется делителем 29 частоты в последовательность с периодом . Коэффи1щент С выбирается таким обра Сг

: зом, чтобы во время - Т уложилось К

периодов тактовой частоты, где К - размер (в элементах разложения) эталонного сигнала. Эталонный сигнал, распределение которого задается заранее, исходя из априорных характеристик исследуемого объекта, записы- вается в ячейки умножителя 14. Адрес для обращения в ячейкам ШТЗУ вырабатывает 32 через подсчет в

С

- .1-,.... Адрес

для обращения к ячейкам блока 12 (количество равно числу элементов разложения строба М X М) изменяется по сигналам с выхода делителя 29 часто

каждом полупериоде - - Т,

/

0

05

5 , Q

5

5

5 0

5

0

0

4)6

ты. /|ноичиый 1СОД каждого из М х М элементов, хранящийся в блоке 12, считывается, делится двоичным делителем 13 (включенным с целью устранения флуктуаиионных ошибок и выбора разрядности сомножителя умножителя 14) и умножается последовательно на все элементы эталона. Результат умножения через регистр 9 (подключенный в режиме вычисления корреляционной функ1щи) транслируется на первый вход сумматора 10, работающего в режиме сложения, и складывается с содержимым регистра 11. После умножения на все элементы эталона и суммирования в i-ячейках блока 12 оказывается записанным распределение корреляционной функции сигнала изображения,- находящегося внутри строба и сигнала эталона, хранящегося в ГШЗУ 14. Дешифратор 21 контролирует появление числа i на выходе счетчика 19, т.е. момент окончания вычисления корреляционной функции. При срабатывании дешифратора 21 элемент И 36 формирует сигнал сброса триггера 33 (окончание- вычисления корреляционной функции) и установки в единичное состояние в режиме вывода корреляци- - онной функции. Счётчик 20 открывается для счета импульсов с выхода делителя 30 частоты (коэффициент деления D может быть задан из практических соотношений, например, чтобы успеть вывести весь массив RCf.ij) до окончания активной области телевизионного растра), а к адресному выходу блока 4 подк.точается регистр 26. На выходе триггера 8 присутствует единичный сигнал, С периодом ;Т /D на этот выход поступает инфор-, нация, срабатывает дешифратор 22 и управляющий сигнал через элемент И 37 устанавливает в нулевое состояние триггер 34 (заканчивается режим вьгаода корреляционной функции R(, i).i а также в единичное состояние триггер 35. На его вькоде (выход 16 устройства) появляется сигнал Останов. Цикл работы видеопроцессора в данном кадре заканчивается.

Формула изобретения

Оптическое устройство для вычис- ; ления корреляционной функции, содержащее аналого-цифровой преобразователь, первый регистр, сумматор, блок памяти, умножитель, причем выход а

лого-цифрового преобразователя соединен с информационным входом первого регистра, отличающееся тем, что, с целью повьпиения точности в него введены преобразователь оптического информационного сигнала в электрический, формирователь строба, синхрогенератор импульсов, блок формирования адресов, блок управления, делитель на постоянное число, три регистра, причем блок формирования адресов содержит четыре счетчика, четыре регистра, два дешифратора,, (блок управления содержит два форми- рователя импульсов, два делителя частоты, три элемента. И, три триггера, счетчик, в блоке формирования сов счетный вход первого счетчика соединен с счетным входом второго счетчика и с первым выходом синхро- генератора импульсов, вход разрешения работы первого счетчика соединен с входом разрешения считывания первого регистра и с вторым выходом синх- рогенератора импульсов, выход первого счетчика соединен с информационным входом первого регистра, вход разрешения работы второго счетчика ;соединен с входом разрешения считы- Звания второго регистра и с выходом строба формирователя строба, выход :второго счетчика соединен с информационным входом второго регистра,вход разрешения работы третьего счетчика соединен с входом разрешения очиты- вания третьего регистра и с прямым выходом первого триггер.а блока управления, счетный вход третьего счетчика соединен с выходом первого делителя блока управления, вход разрешения работы четвертого счетчика соединен с входом разрешения записи четвертого регистра и с прямым выход второго триггера блока управления, счетный вход четвертого триггера соединен с выходом второго делителя блока управления, выход третьего счетчика соединен с информационным входом третьего регистра и через первый дешифратор с первым входом перво го элемента И блока управления, выход четвертого счетчика соединен с информационным входом четвертого регистра и через второй дешифратор с первым входом второго элемента И бло ка управления, выходы первого, второго, третьего и четвертого регистров через монтаж 1ое. ИЛИ соединены с ад

0

„ 25 , м ресным входом блока памяти, в блоке управления вход первого формирователя импульсов, входы первого и второго делителей частоты и первый вход третьего элемента И соединены с вторым выходом синхрогенератора импульсов, выход первого формирователя импульсов соединен с входом разрешения записи-считьтвания первого регистра и через второй формирователь им- jпульсов с входом разрешения записи- считывания блока памяти, выход первого делителя частоты соединен с вторым входом третьего элемента И, выход которого соединен с счетным входом счетчика, выход которого соединен с первым входом умножителя, входы установки в О первого, второго и третьего триггеров соединены с вторьтг-i выходом синхрогенератора импульсов, информационные входы первого и второго триггеров соединены с шиной нулевого потенциала, вход установки в 1 первого триггера соединен с вторым выходом синхрогенератора импульсов, прямой вькод первого триггера соединен с вторым входом первого элемента И, выход которого соединен с синхронизирующим входом первого триггера и с входом установки в 1 второго триггера а прямой выход которого соединен с вторым входом второго элемента И, выход которого соединен с синхронизирующим входом второго триггера и с входом установки в

Ч

третьего триггера, прямой выход которого является выходом признака окончания работы устройства, синхронизирующий вход и выход преобразователя оптического сигнала в электрический соединены соответственно с третьим выходом синхрогенератора импульсов и инфо1}мационным входом аналого-цифрового преобразователя, вход запуска которого соединен с первым выходом синхрогенератора импульсов, второй выход которого соединен с входом обнуления первого регистра, информационный вход которого соединен с выходом сумматора, первый вход которого соединен с информационным входом блока памяти и выходом первого регистра, выход блока памяти соединен с информационным входом второго регистра и через делитель на постоянное число с вторым входом умножителя, выход которого соединен с информационным входом третьего регистра. Входы разрешения

считывания второго и третьего регистров соединены с пpямы fи выходами соответственно второго и первого триггеров блока управления, выходы первого, второго и третьего регистров соединены через монтажное ИЛИ с

1520541

вторым входом сумматора и являются информационным выходом устройства, первый, второй, и третий- входы форьш- рователя строба соединены соответственно с первым, вторым и четвертым выходами синхрогенераторов импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения экстремальных значений | 1989 |

|

SU1615747A1 |

| Телевизионный координатор | 1983 |

|

SU1109956A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| Оптикоэлектронный координатор для автоматического вождения мобильных агрегатов | 1986 |

|

SU1378086A1 |

| Устройство для измерения расстояния между центрами двух изображений точечного объекта | 1990 |

|

SU1788597A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1339628A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| СПОСОБ СЛЕЖЕНИЯ ЗА ОБЪЕКТОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2153235C2 |

| Синхрогенератор | 1989 |

|

SU1672586A1 |

| ТЕЛЕВИЗИОННЫЙ КООРДИНАТНЫЙ ДИСКРИМИНАТОР | 1996 |

|

RU2139640C1 |

Изобретение относится к телевизионной технике и может быть использовано для корреляционной обработки сигналов в измерительных системах. Цель изобретения - повышение точности вычисления корреляционной функции при обработке сигнала изображения. Видеопроцессор содержит преобразователь 1 оптического информационного сигнала в электрический, синхрогенератор 2 импульсов, формирователь 3 строба, блок 4 формирования адресов, блок 5 управления, аналого-цифровой преобразователь 6, регистры 7-9, 11, сумматор 10, блок 12 памяти, делитель 13 на постоянное число и умножитель 14, позволяет для сигнала изображения, ограниченного областью строба, в течение одного кадра телевизионного изображения вычислять с требуемой разрядностью взаимную корреляционную функцию сигнала и эталона и осуществлять вывод цифровых значений элементов корреляционной функции. 3 ил.

фиг. 2

CS/1.2

Cff/f.

- Haff/f. 11

Ha ff/i. /«

Наб/гЛ ffa ff/гЛ Haff

35

W

Фи.г.3

| Цифровой коррелятор | 1986 |

|

SU1336031A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-11-07—Публикация

1988-04-08—Подача