Изобретение относится к вычислительной технике и может быть использовано при построении устройств памяти большого объема.

Цель изобретения - повышение информационной емкости устройства.

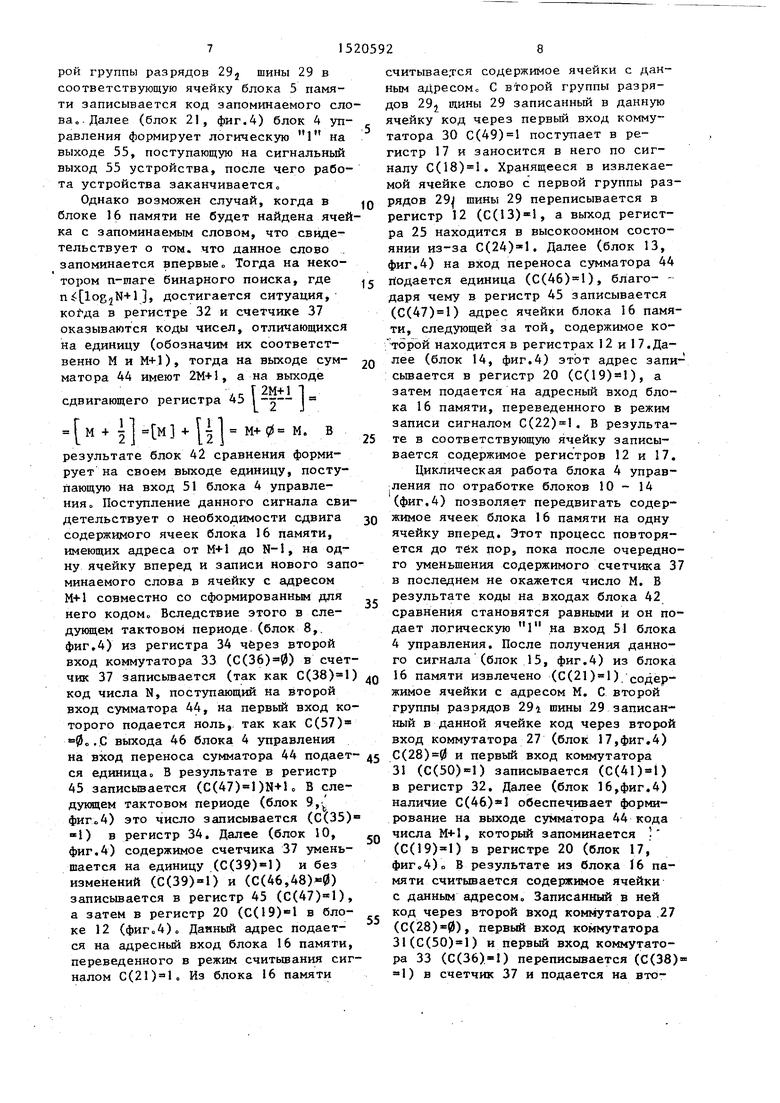

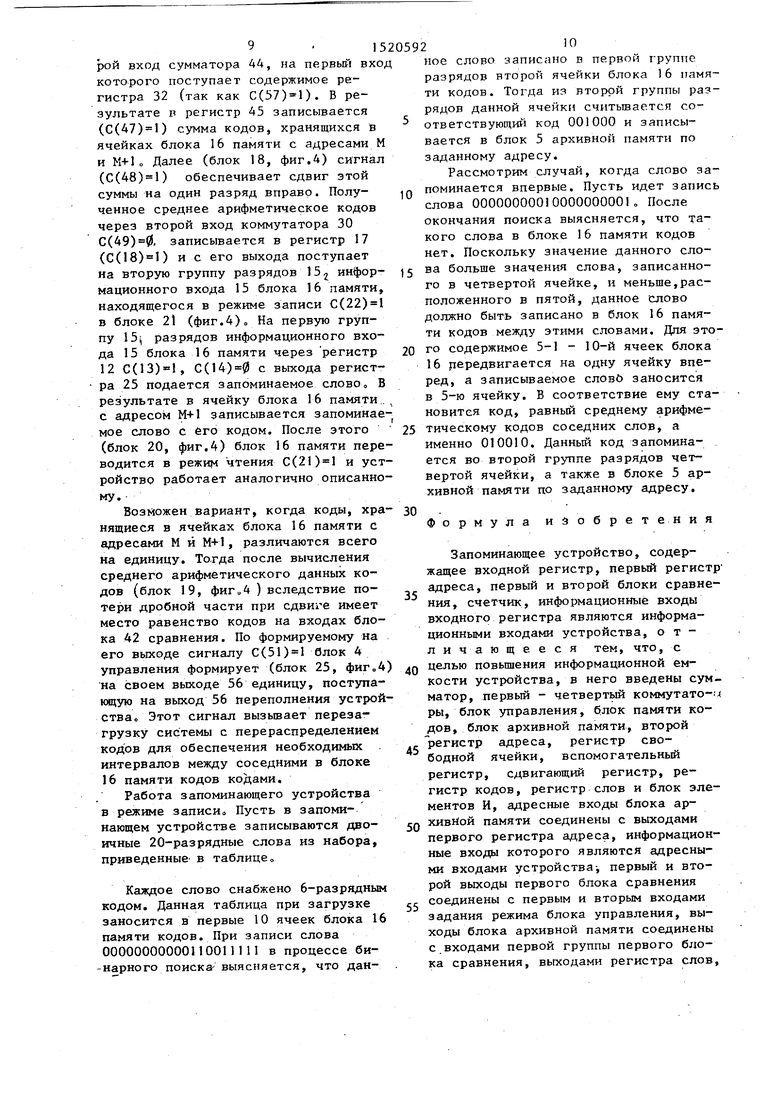

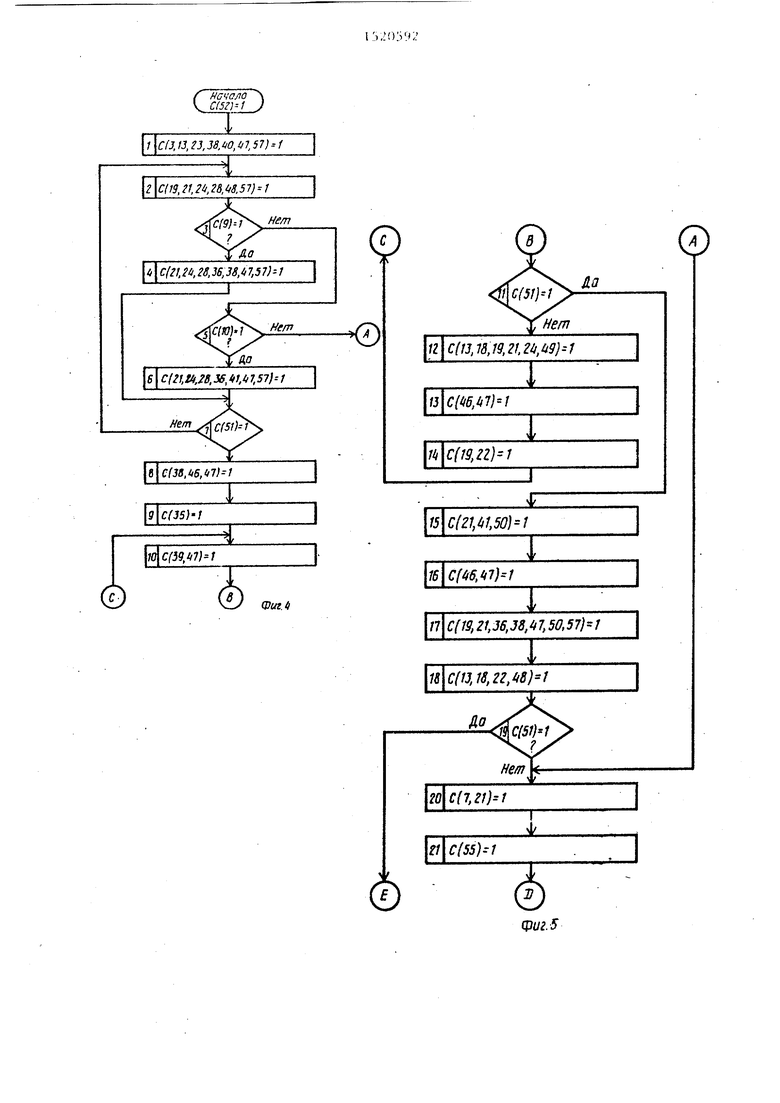

На фиГо приведена структурная схема запоминающего устройства; на фиг.2 - структурная схема одного из вариантов блока управления; на фиг.3- блок-схема алгоритма работы блока управления в режиме считывания; на фиг.4 - 6 - блок-схема алгоритма работы блока, управления в режиме записи.

Запоминающее устройство имеет (фиг.1) первый регистр 1 адреса, адресные входы 2, первый выход 3 блока

4 управления, блок 5 архивной памяти, второй 6 и третий 7 выходы блока управления, первый блок 8 сравнения, первый 9 и второй 10 входы блока управления, информационные выходы 11, регистр 12 слов, четвертый 13 и пя- тьй 14 выходы блока управления, информационные входы 15 блока 16 памяти кодов, регистр 17 кодов, шестой 18 и седьмой 19 выходы блока управления, второй регистр -20 адреса, восьмой 21, девятый 22, десятый 23 и одиннадцатый 24 выходы блока управления, входной регистр 25, информационные входы 26, первый 27 коммутатор, двенадцатый выход 28 блока управления, выход 29 блока памяти кодов, второй 30 и третий 31 коммутасд ю

CD 01

со to

торы, вспомогательный регистр 32, четвертый коммутатор 33, регистр 34 свободной ячейки, тринадцатый 35 и четырнадцаты} 36 выходы блока управления, счетчик 37, пятнадцатый 38, шестнадцатый 39, семнадцатый 40 и восемнадцатый 41 выходы блока управления, второй блок 42 сравнения, блок элементов И 43, сумматор 44, сдвигающий регистр 45, девятнадцатый 46, двадцатый 47, двадцать первый 48, двадцать второй 49 и двадцать третий 50 выходы блока управления, третий вход 51 блока управления, входы записи 52, чтения 53 и установки 54 в исходное состояние, сигнальный вход 55, выход 56 переполнения блока, управления и двадцать четвертый выход 57 блока управления о

Блок управления () имеет вход синхронизации 58 устройства, блок 59 постоянной памяти микропрограмм, регистр 60 микрокоманды,счетчик 61 адреса и блок 62 мультиплексоров о

Работа устройства основана на том что каждому запоминаемому слову ставится в соответствие его код, имеющий меньшую разрядность по сравнению с самим словом. По соответствующему адресу в блоке 5 архивной памяти вместо слова записывается его более короткий код, что позволяет увеличить информационную емкость устройства

Все запоминаемые слова и их коды хранятся в блоке 16 памяти кодов, ячейка которого в первой группе разрядов хранит одно запоминаемое слово, а во второй группе разрядов - соответствующий ему код При загрузке системы слова (и их коды) размещаются в блоке 16 памяти кодов в порядке возрастания, что позволяет вести бинарный поиск. Адрес первой незанятой ячейки блока 16 памяти кодов заносится в регистр 34 свободной ячейки. Если некоторое слово запоминается впервые, то оно заносится в блок 16 памяти кодов и снабжается кодом, равньм среднему арифметическому кодов в соседних ячейках.

Устройство работает следующим образом,

Дпя подготовки устройства к работе на вход 54 блока 4 управления подается импульс, устанавливающий его в начальное состояние После этого на вход 53 (52) блока 4 управления

5

0

5

0

5

0

5

0

поступает сигнал, переводящий его в режим считывания записи информации, а на адресньп вход 2 устройства подается код адреса, по которому информация должна быть считана (записана) о

При работе блока 4 управления в режиме считывания (фиг.З) каждый блок (кроме проверки условия) описывает состояние выходов блока 4 управления в течение одного тактового периода. С(...) - сигнал на соответствующем входе-выходе. На блок-схемах фиГоЗ - 6 показаны сигналы, имеющие значения логической I Не приведенные в блоках сигналы на протяжении соответствующего тактового периода полагаются равными нулю.

В первом тактовом периоде (блок 1, фиГоЗ) .адрес считьшаемой информации записывается в регистр 1 (С(3)1) и подается на адресный вход блока 5 памяти, который переведен в режим счи- тьшания сигналом с выхода 6 блока 4 управления Вследствие этого с информационного выхода блока 5 памяти на первый вход блока 8 сравнения поступает код считьшаемого слова. Выход регистра 12 переведен в высокоомное состояние сигналом С(14)1 Одновременно с этим происходит обнуление регистра 32 (С(40)1). Кроме того, с выхода регистра 34 через второй вход коммутатора 33 (так как С(36)0, в счетчик 37 переписьшается (С(38)) число, являющееся адресом первой свободной ячейки блока 16 памяти, поступающее на второй вход сумматора 44, на первый вход которого подан код числа 0. Код числа N с выхода сумматора 44 подается на информационный вход регистра 45 и записывается в него вследствие 0(47)

В следующем такте (блок 2,фиг.З) в регистре 45 по сигналу С(48)1 данный код сдвигается вправо с потерей младшего разряда и заполнением старшего разряда нулем. Таким образом, на информационный вход регистра 20

поступает код числа

.

где квад

ратные скобки означают целую часть заключенного в них выражения. По сигналу С(19)1 данный код заносится в регистр 20 и подается на адресный ; вход блока 16 памяти, переведенного в режим считывания сигналом С(21)1. Из

блока 16 памяти считывается содержи Nмое ячейки с адресом

записанный в ней код со второй группы 29J разрядов выходной шины 29 через второй вход коммутатора ,27 (так как С(28)0) проходит на второй вход блока 8 сравнения. Если данный код

запоминающего устройства (С(14)0)„ Блок 4 управления формирует логическую 1 на выходе 55-, которая по ступает на сигнальный выход 55 устройства, сигнализируя об отработке заданной операции.

Если устройству задан режим запи

больше кода, поданного на первый вход JQ - информации оно работает следующим образом. По сигналу С(52)1 раб та блока 4 управления организуется в соответствии с блоком-схемой (фиг,4 В первом тактовом периоде (блок

блока 8 сравнения, то на первом выходе последнего формируется единица, подаваемая на вход 9 блока 4 управления. Это влечет за собой то, что

щим образом. По сигналу С(52)1 ра та блока 4 управления организуется соответствии с блоком-схемой (фиг, В первом тактовом периоде (блок

в следующем тактовом периоде (блок 4, ,5 ФиГо4) с информационного входа 26

устройства в регистр 25 заносится (С(23)1) записываемое слово, кото переписывается также в регистр 12 (С(13)1). Одновременно с адресно

фиг.З) из регистра 45 через второй вход коммутатора 31 (С(5)0) и первый вход коммутатора 33 (С(36)1) в счетчик 37 записывается (так как

N 1 г I, В результате на выходе сумматора 44 формируfN 1 ется код который записывается в

регистр 45 (С(47)1).

Если имеет место обратное соот ношение кодов на входах блока 8 сравнения, то сигнал высокого уровня появляется на втором его выходе

устройства в регистр 25 заносится (С(23)1) записываемое слово, котор переписывается также в регистр 12 (С(13)1). Одновременно с адресног

20 входа 2 в регистр 1 заносится адрес по которому данное слово должно быт записано о В то же время аналогичным режиму считьшания образом в регистр 45 записьшается код числа. В

25 следующем тактовом периоде (блок 2, фиг.4) занесенный в регистр 45 код сдвигается вправо на один разряд (С(48)1) и переписывается в регист 20 (С(19)1), в результате чего из

и поступает на вход 10 блока 4 управ- 30 бдока 16 памяти считывается (С(21) ления. В этом случае в следующем так- 1) содержимое ячейки с адресом товом периоде (блок 6, фиГоЗ) код чи- И1 кроме того, выход регистра 25

Г N 1т, v J

ела - с выхода коммутатора 31 записывается в регистр 32 (С(41)). ,

В результате с выхода сумматора 44 на в режим считывания (С(21)1), в ре- информационный вход регистра 45 попереводится в высокоомное состояние (С(24)1), блок 16 памяти переходит

зультате чего- через первый вход коммутатора 27 (так как С(28) 1) на второй вход блока 8 сравнения подает

3N дается код числа - .

После этого устройство работает аналогично описанному. ,В по.следую- щем (блок 2, фиг.З) такте код, занесенный в регистр 45, сдвигается вправо и записывается в регистр 20, что вызывает считывание содержимого ячейки блока 16 памяти, имеющей адрес

II

или

т N ),и т,До Таким образом осуществляется бинарный поиск в блоке 16 памяти ячейки, содержащей во второй группе своих разрядов код, идентичньй считанному из блока 5 памяти В момент ее нахождения на

обоих выходах блока 8 сравнения при- присутствию логических нулей на выхо ,, с .

сутствующее извлеченному из блока 5 памяти коду. После этого (блок 8, фиг.З) с выхода регистра 12 слово проходит на информационный выход 11

дах блока 8 сравнения, Это влечет в следующем тактовом периоде (блок 20, фиг,4) перевод блока 5 памяти в режим записи (С(7) ), В результате с вто-

1520592

запоминающего устройства (С(14)0)„ Блок 4 управления формирует логическую 1 на выходе 55-, которая поступает на сигнальный выход 55 устройства, сигнализируя об отработке заданной операции.

Если устройству задан режим запи - информации оно работает следующим образом. По сигналу С(52)1 работа блока 4 управления организуется в соответствии с блоком-схемой (фиг,4). В первом тактовом периоде (блок 1,

устройства в регистр 25 заносится (С(23)1) записываемое слово, которое переписывается также в регистр 12 (С(13)1). Одновременно с адресного

входа 2 в регистр 1 заносится адрес, по которому данное слово должно быть записано о В то же время аналогичным режиму считьшания образом в регистр 45 записьшается код числа. В

следующем тактовом периоде (блок 2, фиг.4) занесенный в регистр 45 код сдвигается вправо на один разряд (С(48)1) и переписывается в регистр 20 (С(19)1), в результате чего из

переводится в высокоомное состояние (С(24)1), блок 16 памяти переходит

в режим считывания (С(21)1), в ре-

зультате чего- через первый вход коммутатора 27 (так как С(28) 1) на второй вход блока 8 сравнения подается содержимое первой группы разрядов считываемой из блока 16 памяти ячейки. На первый вход блока 8 сравнения с выхода регистра 12 подается записываемое слово информационный выход

блока 5 памяти находится в высокоом- ном состоянии, так как С . Далее (блоки 3-7, фиг„4) осуществляется бинарный поиск в блоке 16 памяти ячейки, содержащей в первой группе своих

разрядов слово, идентичное записы- ваемомуо Работа устройства в данном режиме аналогична работе блоков 3 - 6 режима считывания. Момент нахождения данной ячейки идентифицируется по

.

дах блока 8 сравнения, Это влечет в следующем тактовом периоде (блок 20, фиг,4) перевод блока 5 памяти в режим записи (С(7) ), В результате с вто- .

рой группы разрядов 29j шины 29 в соответствующую ячейку блока 5 памяти записывается код запоминаемого слова,. Далее (блок 21, фиг.4) блок 4 управления формирует логическую 1 на

выходе 35, поступающую на сигнальный выход 55 устройства, после чего работа устройства заканчивается

Однако возможен случай, когда в блоке 16 памяти не будет найдена ячейка с запоминаемым словом, что свидетельствует о том, что данное слово запоминается впервые Тогда на некотором n-mare бинарного поиска, где n logjN+l3, достигается ситуация, в регистре 32 и счетчике 37 оказываются коды чисел, отличающихся на единицу (обозначим их соответственно М и М+1), тогда на выходе сумматора 44 имеют 2М+1, а на выходе

.. Г 2М+1 1 сдвигающего регистра 4j 1 -j-

м + Л М + Ul M-i-0 М. В

результате блок 42 сравнения формирует на своем выходе единицу, поступающую на вход 51 блока 4 управления Поступление данного сигнала сви детельствует о необходимости сдвига содержимого ячеек блока 16 памяти, имеющих адреса от М+1 до N-1, на одну ячейку вперед и записи нового запминаемого слова в ячейку с адресом М+1 совместно со сформированным для него кодом Вследствие этого в сле- дукяцем тактовом периоде (блок 8,, фиг,4) из регистра 34 через второй вход коммутатора 33 (С(36)0) в счетчик 37 записывается (так как С(38)1 код числа N, поступающий на второй вход сумматора 44, на первый вход которого подается ноль, так как С(57)

считывае.тся содержимое ячейки с данным адресом С второй группы разрядов 29j щины 29 записанный в данную ячейку код через первый вход коммутатора 30 С(49)1 поступает в регистр 17 и заносится в него по сигналу C(18)i. Хранящееся в извлекаемой ячейке слово с первой группы разрядов 29l шины 29 переписывается в регистр 12 (С(13)1, а выход регистра 25 находится в высокоомном состоянии из-за С(24)-1. Далее (блок 13, фиг.4) на вход переноса сумматора 44 15 йодается единица (С(46)1), благо- - даря чему в регистр 45 записывается (G(47)l) адрес ячейки блока 16 памяти, следующей за той, содержимое ко- торой находится в регистрах 12 и 1 7.Далее (блок 14, фиг.4) этот адрес записывается в регистр 20 (С(19)-1), а затем подается на адресный вход блока 16 памяти, переведенного в режим записи сигналом С(22)1. В результате в соответствующую ячейку записывается содержимое регистров 12 и 17. Циклическая работа блока 4 управ- :ления по отработке блоков 10 - 14 (фиг.4) позволяет передвигать содержимое ячеек блока 16 памяти на одну ячейку вперед. Этот процесс повторяется до тех пор, пока после очередного уменьшения содержимого счетчика 37 в последнем не окажется число М. В ,- результате коды на входах блока 42 сравнения становятся равными и он подает логическую I на вход 51 блока 4 управления. После получения данного сигнала (блок 15, фиг.4) из блока 16 памяти извлечено (С(21)1) содержимое ячейки с адресом М. С второй группы разрядов 29i шины 29 записанный в данной ячейке код через второй вход коммутатора 27 (блок 17,фиг,4)

в0„.с выхода 46 блока 4 управления

на вход переноса сумматора 44 подает- 5 С(28)0 и первый вход коммутатора

ся единица В результате в регистр 31 (С(50)1) записывается (С(41)«1)

45 записьтается (C(47))N+1 о В следукщем тактовом периоде (блок 9,) это число записывается (0(35)

50

1) в регистр 34. Далее (блок 10, фиг.4) содержимое счетчика 37 уменьшается на единицу (С(39)1) и без изменений (С(39)1) и (С(46,48)«0) записьшается в регистр 45 (С(47)1), а затем в регистр 20 (С(19)1 в бло- код через второй вход коммутатора .27 ке 12 (фиго4) Данный адрес подает- (С(28)), первый вход коммутатора ся на адресньй вход блока 16 памяти, 31(С(50)1) и первый вход коммутато- переведенного в режим считьшания сиг- ра 33 (С(36).-1) переписывается (С(38) налом С(21)1. Из блока 16 памяти 1) в счетчик 37 и подается на втов регистр 32. Далее (блок 16,фиг,4) наличие С(46)1 обеспечивает формирование на выходе сумматора 44 кода числа М+1, который запоминается (С(19)1) в регистре 20 (блок 17, фиг,4)о В результате из блока J6 памяти считывается содержимое ячейки с данным адресом Записанный в ней

5

Q

считывае.тся содержимое ячейки с данным адресом С второй группы разрядов 29j щины 29 записанный в данную ячейку код через первый вход коммутатора 30 С(49)1 поступает в регистр 17 и заносится в него по сигналу C(18)i. Хранящееся в извлекаемой ячейке слово с первой группы разрядов 29l шины 29 переписывается в регистр 12 (С(13)1, а выход регистра 25 находится в высокоомном состоянии из-за С(24)-1. Далее (блок 13, фиг.4) на вход переноса сумматора 44 5 йодается единица (С(46)1), благо- - даря чему в регистр 45 записывается (G(47)l) адрес ячейки блока 16 памяти, следующей за той, содержимое ко- торой находится в регистрах 12 и 1 7.Далее (блок 14, фиг.4) этот адрес записывается в регистр 20 (С(19)-1), а затем подается на адресный вход блока 16 памяти, переведенного в режим записи сигналом С(22)1. В результате в соответствующую ячейку записывается содержимое регистров 12 и 17. Циклическая работа блока 4 управ- :ления по отработке блоков 10 - 14 (фиг.4) позволяет передвигать содержимое ячеек блока 16 памяти на одну ячейку вперед. Этот процесс повторяется до тех пор, пока после очередного уменьшения содержимого счетчика 37 в последнем не окажется число М. В ,- результате коды на входах блока 42 сравнения становятся равными и он подает логическую I на вход 51 блока 4 управления. После получения данного сигнала (блок 15, фиг.4) из блока 16 памяти извлечено (С(21)1) содержимое ячейки с адресом М. С второй группы разрядов 29i шины 29 записанный в данной ячейке код через второй вход коммутатора 27 (блок 17,фиг,4)

0

5

0

0

код через второй вход коммутатора .27 (С(28)), первый вход коммутатора 31(С(50)1) и первый вход коммутато- ра 33 (С(36).-1) переписывается (С(38) 1) в счетчик 37 и подается на втов регистр 32. Далее (блок 16,фиг,4) наличие С(46)1 обеспечивает формирование на выходе сумматора 44 кода числа М+1, который запоминается (С(19)1) в регистре 20 (блок 17, фиг,4)о В результате из блока J6 памяти считывается содержимое ячейки с данным адресом Записанный в ней

44, на первый вход содержимое рерой вход сумматора которого поступает гистра 32 (так как С(57)1). В результате р регистр 45 записывается (С(47)1) сумма кодов, хранящихся в ячейках блока 16 памяти с адресами М и М+1о Далее (блок 18, фиг.4) сигнал (С(48)1) обеспечивает сдвиг этой суммы на один разряд вправо. Полученное среднее арифметическое кодов через второй вход коммутатора 30 С(49)0, записывается в регистр 17 (С(18)1) и с его выхода поступает на вторую группу разрядов 15 информационного входа 15 блока 16 памяти, находящегося в режиме записи С(22)1 в блоке 21 (фиг.4)о На первую группу 15i| разрядов информационного входа 15 блока 16 памяти через регистр 12 0(13), С(14)0 с выхода регист- ра 25 подается запоминаемое слово, В результате в ячейку блока 16 памяти.. с адресом М+1 записывается запоминаемое слово с его кодом. После этого (блок 20, фиг.4) блок 16 памяти переводится в режин чтения С(21)1 и устройство работает аналогично описанному.

Возможен вариант, когда коды, хранящиеся в ячейках блока 16 памяти с адресами М и М+1, различаются всего на единицу. Тогда после вычисления среднего арифметического данных ко дов (блок 19, фиг„4 ) вследствие по тери дробной части при сдвиге имеет место равенство кодов на входах блока 42 сравнения. По формируемому на его выходе сигналу С(51)1 блок 4 управления форь1ирует (блок 25, ) на своем выходе 56 единицу, поступающую на выход 56 переполнения устройства. Этот сигнал вызьшает перезагрузку системы с перераспределением кодов для обеспечения необходимых интервалов между соседними в блоке 16 памяти кодов кодами.

Работа запоминающего устройства в режиме записи Пусть в запоминающем устройстве записываются двоичные 20-разрядные слова из набора, приведенные в таблице

Каждое слово снабжено 6-разрядным кодом. Данная таблица при загрузке заносится в первые 10 ячеек блока 16 памяти кодов. При записи слова 00000000000110011111 в процессе би- нарного поиска выясняется, что дан

нее слово записано в первой группе разрядов второй ячейки блока 16 памяти кодов. Тогда из второй группы разрядов данной ячейки считьшается соответствующий код 001000 и записывается в блок 5 архивной памяти по заданному адресу.

Рассмотрим случай, когда слово запоминается впервые. Пусть идет запись слова 0000000001000000000К После окончания поиска выясняется, что такого слова в блоке 16 памяти кодов нет. Поскольку значение данного слова больше значения слова, записанного в четвертой ячейке, и меньше,расположенного в пятой, данное слово должно быть записано в блок 16 памяти кодов между этими словами. Для этого содержимое 5-1 - 10-й ячеек блока 16 передвигается на одну ячейку вперед, а записываемое слово заносится в 5-ю ячейку. В соответствие ему становится код, равный среднему арифметическому кодов соседних слов, а именно 010010. Данный код запоминается во второй группе разрядов четвертой ячейки, а также в блоке 5 архивной памяти по заданному адресу.

ормула изобретения

5

0

5

Запоминающее устройство, содержащее входной регистр, первый регистр адреса, первый и второй блоки сравнения, счетчик, информационные входы входного регистра являются информационными входами устройства, отличающееся тем, что, с целью повьшения информационной емкости устройства, в него введены сумматор, первый - четвертьй коммутато-м ры, блок управления, блок памяти кодов, блок архивной памяти, второй регистр адреса, регистр свободной ячейки, вспомогательный регистр, сдвигающий регистр, регистр кодов, регистр слов и блок элементов И, адресные входы блока ар- Q хивйой памяти соединены с выходами первого регистра адреса, информационные входы которого являются адресными входами устройства-, первый и второй выходы первого блока сравнения соединены с первым и вторым входами задания режима блока управления, выходы блока архивной памяти соединены с входами первой группы первого блока сравнения, выходами регистра слов.

5

информационными входами первой группы блока памяти кодов и являются информационными выходами устройства, вьпсоды регистра кодов соединены с информационными входами второй группы блока памяти кодов, адресные входы которого соединены с выходами второго регистра адреса, информационные входы которого соединены с выходами сдвигающего регистра, входами первой группы второго блока сравнения, информационными входами первой группы второго и третьего коммутаторов, информационные входы второй группы которого соединены с выходами первого коммутатора и входами второй группы первого блока сравнения, выходы входного регистра соединены с соответствующими информационными входами регистра слов, выходами первой группы блока памяти кодов и информационными входами первой группь первого коммутатора, информационные входы второй группы которого соединены с соответствующими выходами второй группы блока памяти кодов, информационными входами блока архивной памяти и информационными входами второй группы второго коммутатора, выходы которого , . соединены с входами регистра кодов, информационные входы сдвигающег регистра соединены с вькодами сумматора входы первой группы которого соединены с соответствующими выходами счетчика, входы второй группы су 1матора соединены с выходами блока элементов И, первые входы которого соединены с выходами вспомогательного регистра и входами второй группы второго блока сравнения, выходы третьего коммутатора соединены с информационными входами вспомогательного регистра и регистра свободной ячейки и информационными входами первой группы четвертого коммутатора, информационными входами первой группы четвертого коммутатора, информационные входы второй группы которого соединены с выходами регистра свободной ячейки, выходы четвертого коммутатора соединены с информационными

5

0

5

0

5

0

5

0

входами счетчика, выход второго бло- ка сравнения соединен с третьим входом задания режима блока управления, входы записи и чтения которого являются соответствующими входами устройства, вход установки в исходное состояние и вход синхронизации блока управления являются соответствующими входами устройства, первьш выход блока управления соединен с входом синхронизации первого регистра, второй и третий.выходы - соответственно с входами чтения и записи блока архивной памяти, четвертый и пятьй выходы - соответственно с входом синхронизации и задания режима регистра слов, шестой выход - с входом синхронизации регистра кодов, седьмой выход - с входом синхронизации второго регистра адреса, восьмой и девятый выходы - соответственно с входами чтения и записи блока кодов, десятый и одиннадцатый выходы соответственно с входами синхронизации и задания режима входного регистра двенадцатый выход - с входом управления первого ко Ф1утатора, тринадцатьй выход - с входом синхронизации регистра свободной зоны, четырнадцатьй выход - с входом управления четвертого коммутатора, пятнадцатый и шестнадцатьй выходы - соответственно„с входами начальной установки синхронизации счетчика, семнадцатый и восемнадцатый выходы - соответственно с входом установки в начальное состояние и синхронизации вспомогательного регистра, девятнадцатый выход с входом сумматора, двадцатьй и двадцать первый выходы - соответственно с входами синхронизации и сдвига сдвигающего регистра, двадцать второй выход - с входом управления второго коммутатора, двадцать третий выход - с входом управления третьего коммутатора,двадцать четвертый и двадцать пятый выходы являются соответственно первым и вторым выходами контроля работы устройства, двадцать шестой выход блока управления соединен с вторыми вх ода- ми блока элементов И.

Z6

6

39

5,

.47.5

910515153

Фиг.г

®

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для изучения языка | 1990 |

|

SU1785029A1 |

| Ассоциативное оперативное запоминающее устройство | 1987 |

|

SU1462420A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Ассоциативное оперативное запоминающее устройство | 1989 |

|

SU1714682A1 |

| Электронный словарь для изучения иностранного языка | 1989 |

|

SU1649568A1 |

| Ассоциативное оперативное запоминающее устройство | 1988 |

|

SU1667155A1 |

| Электронный словарь для изучения иностранного языка | 1988 |

|

SU1532965A1 |

| Электронный словарь для изучения иностранного языка | 1988 |

|

SU1702394A1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

| Ассоциативное запоминающее устройство | 1982 |

|

SU1043750A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении устройств памяти большого объема. Цель изобретения - повышение информационной емкости устройства. Запоминающее устройство содержит два регистра адреса, адресные входы устройства, блок архива его памяти, два блока сравнения, информационные выходы устройства, регистр слов, блок памяти кодов, регистр кодов, входной регистр, информационные входы устройства, четыре коммутатора, вспомогательный регистр, регистр свободной ячейки, счетчик, блок элементов И, сумматор, сдвигающий регистр, входы записи, чтения, установки в исходное состояние и сигнальный выход переполнения, вход синхронизации устройства. 1 табл., 4 ил.

( конец Фиг.В

| Авторское свидетельство СССР № 1179429, кл, G 11 С 11/00, 1985 | |||

| Запоминающее устройство | 1984 |

|

SU1177856A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-11-07—Публикация

1987-11-10—Подача