00

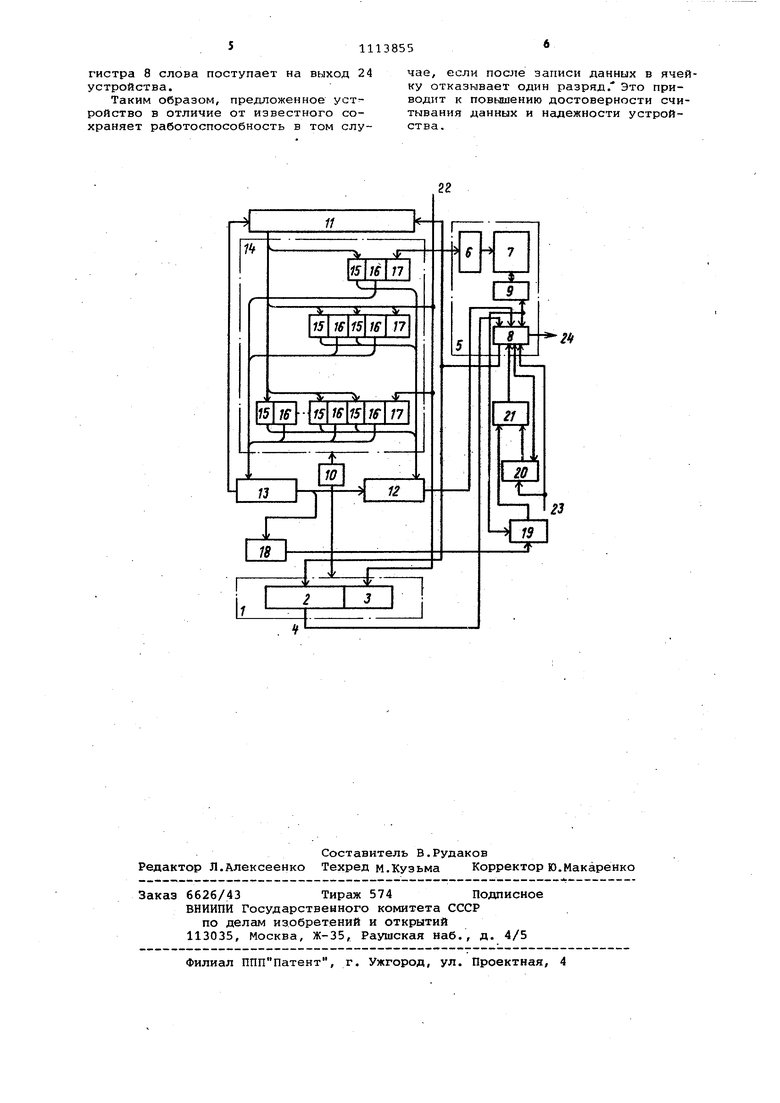

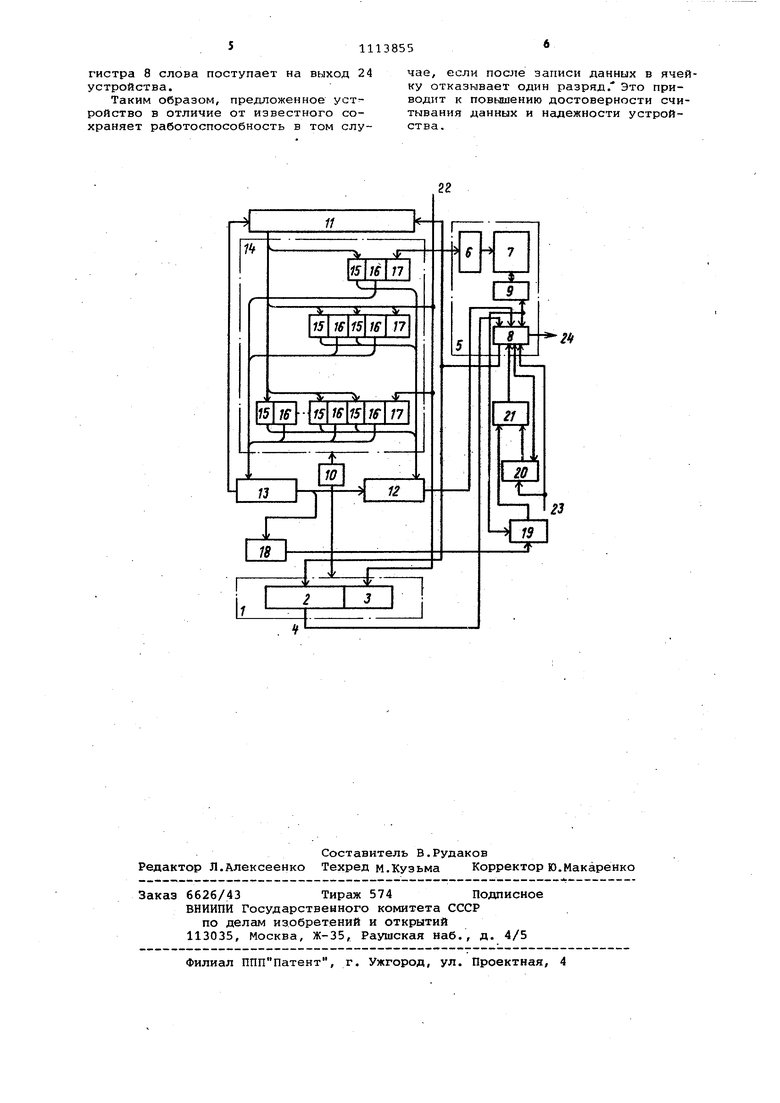

00 сд ел Изобретение относится к вычислитзльной технике. По основному авт. св. № 744738 известно устройство, содержащее адресный блок памяти, соединенный с первым ассоциативным блоком памяти, второй ассоциативный блок памяти, один из входоц которого соединен с первым входом адресного блока памяти, блок управления, выходы которого подключены к управляющим входам ассоциативных блоков памяти, коммутаторы и дешифратор, причем входаа первого коммутатора подключены с ответственно к первому выходу дешифратора и к выходу адресного блока памяти, а выход - к другим входам второго ассоциативного блока памяти выходы которого соединены с входом дешифратора и одним из входов второ го кот пиутатОра, другой вход которого подключен к второму выходу дешифратора, а выход - к второму входу адресного блока памяти СП. В этом устройстве в паузах между внешними обращениями производится контроль исправности ячеек адресног блока памяти. При обнаружении неисп равности какой-либо ячейки определя ется кратность ошибки. В зависимост Ьт кратности ошибки адрес неисправности ячейки фиксируется либо в пер вом ассоциативном блоке памяти, либ во втором. Таким образом, происходит запись разрядов кодовой комбина ции, соответствующих отказавшим разрядам ячейки. При считывании кодовой комбинации оказавшие ячейки п меняются данными одного из ассоциативных накопителей. Однако если воз никает отказ разряда ячейки адресно го накопителя после записи кодовой комбинации, то рабЬтоспособноеть та кого устройства нарушается. Недостатком известного устройств является также низкая достоверность считываемых данных,что снижает его надежность. Цель изобретения - повышение надежности устройства. Поставленная цель достигается те что в оперативное запоминающее устройство с автономным контролем введ ны блок контроля, группа элементов группа элементов ИЛИ и регистр, при чем первые вход и выход блока контроля соединены соответственно с одним из входов адресного блока памяти, второй вход блока контроля соединен с одним из выходов адресного блока памяти, второй выход - с пер.выми входами элементов И группы, вы ходы которых подключены к другим входам адресного блока памяти, вторы входы элементов И группы соединены с инверсными выходами регистра, одн из входов которого подключены к дру гим выходам адресного блока памяти, а другие входы регистра - к выходам элементов ИЛИ группы, входы которых подключены к выходам дешифраторов. На чертеже изображена структурная схема предложенного устройства. Устройство содержит первый ассоциативный блок 1 памяти, который состоит из функциональной части 2 для запоминания слова и аргументной части 3 для запоминания адреса отказавшей ячейки адресного блока памяти. Блок 1 имеет выход 4,. устройство также содержит адресный блок 5 памяти, состоящий из адресного блока б, накопителя 7, регистра 8 слова и усилителей 9 записи-считывания, блок 10 управления, первый Ни второй 12 коммутаторы, дешифраторы 13, второй ассоциативный блок 14 памяти. Блок 14 содержит функциональную часть 15 для размещения содержимого отказавших разрядов и аргументную часть 17 для запоминания адресов отказавших ячеек адресного блока 5 памяти. Устройство содержит также группу элементов ИЛИ 18, регистр 19, блок 20 контроля и группу элементов И 21. Устройство имеет адресный вход 22 информационный вход 23, на который подается записываемое слово, и выход 24, с которого снимается считываемое слово. Блок 10 управления выполнен с использованием сумматора по модулю два и представляет, например, блок контроля 20, подключенный; к входу блока 5. Входы блока контроля подключены к информационным входам 23 устройства и входам блока 5. Вторые входы - выходы блока 20 контроля подключены к входам-выходам блока 5. Входы блока 5 подключены к выходам первого ассоциативного блока памяти, входы которого подключены к выходам блока 5 и входам первого коммутатора 11, вторые входы блока 1 памяти подключены к одним выходам блока 10 управления. Вторые выходы блока 10 подключены к одним из входов блока 14. Третьи входы блока 1 подключены к входам блока 14 и входу 22, на который подается код адреса. Устройство работает следующим образом. , В паузах между внешними обращениями блок 10 управления производит контроль исправности ячеек памяти блока 5. При обнаружении неисправности в какой-либо ячейке блок 10 управления оп еделяет кратность ошибки. Если кратность ошибки меньше или равна т,.где m определяется из неравенства mCl+logjn) 4 п (п - количество разрядов слова, записываемого в адресный блок), то блок 10 управления дополнительно определяет номе ра отказавших разрядов ячейки блока 5. При этом адрес неисправной ячейки фиксируется в аргументной части 17, а номера отказавгиих разрядов в признаковой части 16 ассоциативно го блока 14. Если кратность ошибки больше т, то адрес неисправной ячейки записывается в аргументную часть 3 ассоци тивного блока 1. При обращении к оперативному запоминающему устройству по адресу, установленному на входе 22, происхо дит одновременное обращение как к блоку 5, так и к ассоциативным блонам 1 и 14. Записываемое слово поступает на вход блока 20, где формируется конт рольный разряд, который затем заносится в регистр 8. Записываемое ело во также с входа 23 поступает в регистр 8 и через усилители 9 записисчитывания записывается в накопитель 7 .Если при ассоциативном поиске в блоке 1 обнаружен адрес, по котором производится обращение, то данные с регистра 8 записываются в функциональную часть 2 блока 1.. Если этот адрес обнаружен при ассоциативном п иске Б блоке 14, то содержимое признаковой части 16 соответствующей ячейки блока 14 поступает на дешифраторы 13, выходные си-гналы которы поступают на один из входов коммута тора 11. Одновременно на другой вхо поступает записываемое слово. Разря ды слова, соответствующие отказавши разрядам ячейки блока 5, через коммутатор 11 записываются в функционал ную часть 15 блока 14. ПРИ выполнении операции чтения со держимое накопителя 7 в прямом коде поступает на регистр 8 и регистр 19 Одновременно происходит ассоциативный поиск адреса в блоках 1 и 14. Если в блоках 1 и 14 такого адреса нет, то считанная информация поступает на блок 20. При отсутствии оши бок даннце из регистра 8 поступают на выход 24. Если блок 20 выдал сигнал ошибки, то содержимое регистра 3 слова в обратном коде через усилители 9 записи-считывания заносится в ту ячейку накопителя 7, в которой произошел отказ. Затем происходит считывание в обратном коде содержимого ячейки в регистр 19, где производится поразрядное сложение по модулю два прямого и обратного кодов, считанных из ячейки адресного накопителя. Разряд регистра 19, соответствующий отказавшему разряду ячейки, устанавливается в нулевое состояние, поскольку на него поступает последовательно (прямой или обраный код 1 либо два нуля, либо две единицы. В остс1льных разрядах регистра 19 кол 1. С инвсрсчого . выхода разряда регистра 19, соответствующего отказавшему разряду ячейки, единичный сигнал по разрешающему уровню с блока 20 поступает через соответствующий элемент И 21 группы на вход регистра 8 и-инвертирует искаженный разряд. Исправленный код из регистра 8 слова постул пает на выходе 24 устройства. Если при ассоциативном поиске адрес находился в блоке 1, то содержимое ячейки блока 1, связанной с этим адресом, вьщается на регистр 8, данные регистра проверяются по модулю , два.и выдаются на выходе 24. Если при ассоциативном поиске адрес обращения обнаружен в блоке 14, то содержимое признаковой части 16 соответствующей ячейки блока 14 поступает на дешифраторы 13, выходные сигналы которых подаются на вход коммутатора 12 и-элементы ИЛИ 18. Разряды слова, соответствующие отказавшим разрядам ячейки блока 5, через коммутатор 12 из функциональной части 15 блока 14 записываются в регистр 8. Номера отказавших разрядов признаковой части 16 расшифровываются на дешифраторах 13 и через элементы ИЛИ 18 в регистр 19 поступает код, содержащий 1 в разрядах, которые отказали до э-аписи данных. Слово, записанное в регистре 8, проверяется в блоке 20 и при отсутствии ошибок выдается на выход 24 устройства. При обнаружении ошибки блок 20 выдает сигнал, по которому слово из регистра 8 записывается в обратном коде в ту ячейку, в которой обнаружен отказ. Затем происходит считывание содержимого данной ячейки в обратном коде на регистр 19. Кодовая комбинация, поступившая с накопителя 7, складывается поразрядно по модулю два со словом, которое содержится в регистре 19 /поразрядная сумма по модулю два слова считанного из ячейки в прямом коде, и слова, содержащего 1 в разрядах, соответствующих отказавшим ячейкам. В одном из разрядов регистра 19, соответ.ствующем отказавшему после записи данных .разряду ячейки, будет код О. Действительно, на регистре 19 произведено последовательно сложение по модулю два трех кодов: прямого и обратного, считанных из ячейки, и слова, содержащего 1 в трех разрядах, которые отказали до записи данных в память. Единичный сигнал с инверсного выхода соответствующего разряда регистра 19 по разрешающему уровню с блока 20 поступает через соответствукяций элемент И 21 на вход регистра 8 и инвертирует искаженный разряд. Исправленный код из регистра 8 слова поступает на выход 24 устройства.

Таким образом, предложенное устройство в отличие от известного сохраняет работоспособность в том случае, если после записи данных в ячейку отказывает один разряд. Это приводит к повышению достоверности считывания данных и надежности устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1981 |

|

SU1010659A2 |

| Оперативное запоминающее устройство с автономным контролем | 1978 |

|

SU744738A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| Оперативное запоминающее устройство с автономным контролем | 1979 |

|

SU947912A2 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1161994A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU936033A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU970479A1 |

| Запоминающее устройство с самоконтролем | 1977 |

|

SU720516A1 |

| Оперативное запоминающее устройство | 1976 |

|

SU733019A1 |

ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АВТОНОМНЫМ КОНТРОЛЕМ ПО авт. св. № 744738, отличающееся тем, что, с целью повышения надежности устройства, в него введены блок контроля, группа элементов И, группа элементов ИЛИ и регистр, причем первые вход и выход блока контроля соединены соответственно с одними из входов адресного блока памяти, второй вход блока конт« роля соединен с одним из выходов адресного блока памяти, второй выход - с первыми входами элементов И группы, выходы которых подключены к другим входам адресного блока памяти, вторые входы элементов И группы соединены с инверсными выходами регистра, одни из входов которого подключены к другим выходам адресного блока памяти, а другие входы регистра - к выходам элементов ИЛИ группы, входы которых подключены к I выходам дешифраторов. (Л

}--

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Оперативное запоминающее устройство с автономным контролем | 1978 |

|

SU744738A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-09-15—Публикация

1983-06-17—Подача