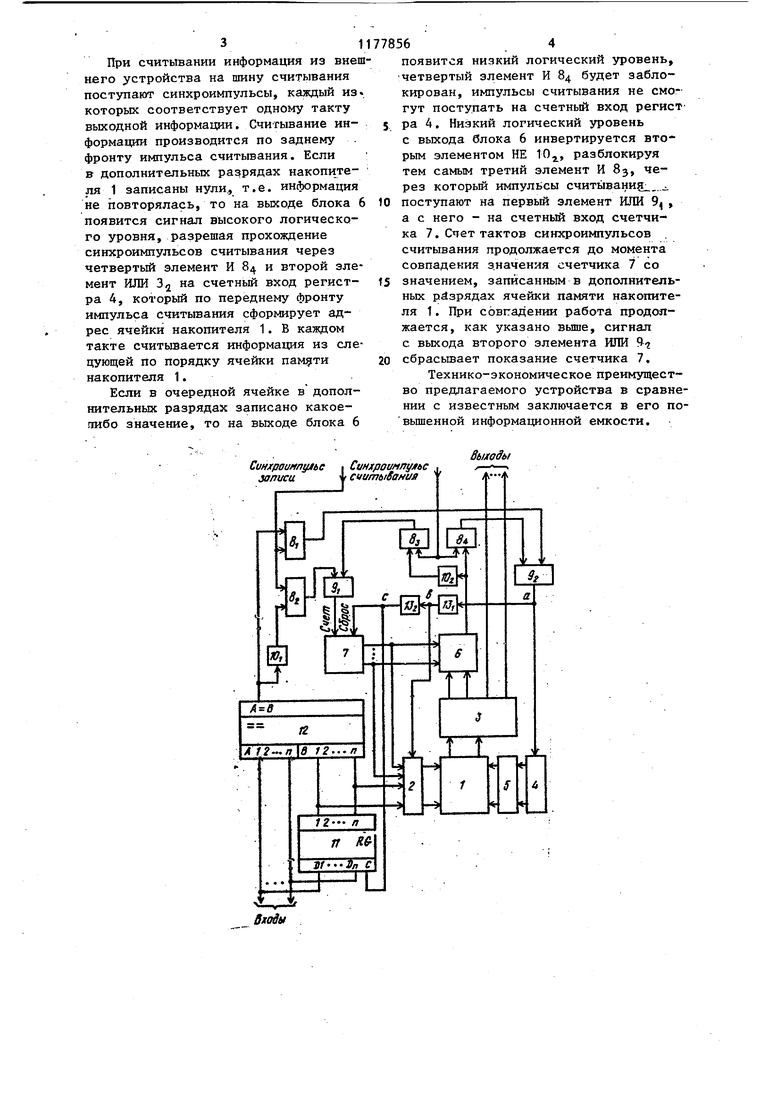

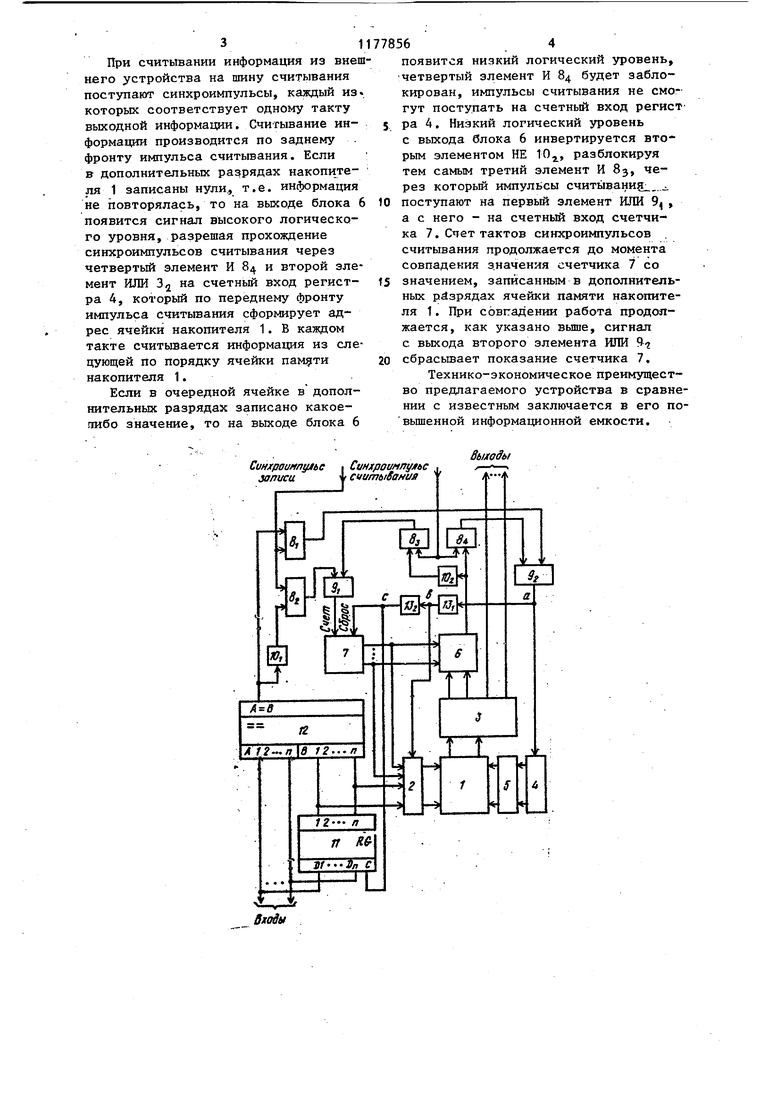

Изобретение относится к вычисли-, тельной технике и может быть использовано при построении буферных запоминающих устройств в системах передачи и приема данных, в частности, при обработке информации от абоненто в порядке ее поступления. Цель изобретения - повьшение информационной емкости устройства. На чертеже изображена структурная схема запоминающего устройства. Устройство содержит накопитель 1, блок 2 записи, блок 3 считывания, регистр 4 адреса, дешифратор 5, первый блок 6 сравнения, счетчик 7, элементы И с первого по четвертый, первый 9j и второй 9 эле-, менты ИЛИ, первый 10f и второй lOrj элементы задержки, регистр 11 числа, второй блок 12 сравнения, первый 13, и второй 132 элементы задержки. Устройство работает следующим образом. Входная информация параллельным кодом поступает одновременно на информационные входы регистра 11 и на входы блока 12 сравнения. Блок 12 сравнивает информацию, записанную в регистр 11 в предьщущем такте запи си, с той информацией, которая появляется на входах устройства к приходу последующего синхроимпульса записи. В случае, если к последнему такт записи информация на входах устройст ва изменяется хотя бы в одном разряде своей кодовой комбинации, то высо кий логический уровень с выхода блока 12 разрешает прохождение синхроимпульса записи через первый элемент И 8, второй элемент ИЛИ 92 на счетный вход регистра 4, который фор мирует новый адрес для записи слова входной информации. Кроме того, синхроимпульс записи с выхода второго элемента ИЛИ 9-j через первый элемент 13( задержки поступает на синхр вход блока 2 записи, при этом, информ ция с выходов регистра 11 переписывается в основные, а показания счетч ка 7 - в дополнительные разряды ячей ки накопителя 1. Через элементы 13 и 132 задержки синхроимпульс записи поступает на вход Сброс счетчика 7 тем самым .обнуляя его, и на синхровход регистра 11, при этом информация, присутствующая в этот момент на входах устройства, записывается в регистр 11. Дальнейшая запись новьк кодовых комбинаций происходит аналогично. Если же, начиная с какого-то момента времени, входная информация остается неизменной в течение не- . скольких тактов записи, то, появившись на входах устройства впервые, с приходом очередного синхроимпульса записи она запишется в регистр 11, после чего блок 12 сигналом низкого логического уровня со своего выхода, заблокировав первьй элемент И Bj, запретит прохождение последующих синхроимпульсов записи на счетиыйвход регистра 4 и другие блоки устройства . НизКий логический уровень на выходе блока 12 инвертируется первым элементом НЕ 10;| . Высокий логический уровень с его выхода разблокирует второй элемент И 8,, благодаря чему синхроимпульсы записи через первы.й элемент ИЛИ 9, поступят на счетный вход счетчика 7, который считает количество тактов повторяющейся информации. Как только входная информация, изменится, то к приходу нового синхроимпульса записи блок 12 сигналом высокого логического уровня со своего выхода разрешит прохождение синхроимпульса записи через пер- вый элемент ИВ, на блоки устройства, одновременно с этим запретив прохож- дение синхроимпульса записи на счетный вход счетчика 7, поскольку второй элемент И 82 будет заблокирован сигналом низкого логического уровня с выхода первого элемента НЕ 10. С выхода первого элемента И В j сишхроимпульс записи через элемент ИЛИ 9 поступит на счетный вход регистра 4, где сформируется адрес для записи повторяющейся кодовой комбинации. Кроме того, через некоторое время, определяемое первым элементом 13.| задержки, этот же синхроимпульс поступит на блок 2, при этом информация с выхода регистра 11 переписывается в основные, а показания счетчика 7 - в дополнительные разряды ячейки памяти накопителя 1. Еще более задержанный вторым элементом 13 задержки синхроимпульс записи поступит на вход Сброс счетчика 7, тем самым обнуляя его, и на синхровход записи в регистр 11. При этом в регистр записывается новая информация. Списывание информации из устройства производится следующим образом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1986 |

|

SU1397968A1 |

| Запоминающее устройство | 1984 |

|

SU1257700A2 |

| Последовательное буферное запоминающее устройство | 1986 |

|

SU1332383A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1644145A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1524050A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1137481A2 |

| Логический анализатор | 1984 |

|

SU1259267A1 |

| Запоминающее устройство системы 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1977 |

|

SU693438A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее последовательно соединенные блок записи, накопитель и блок считьгоания, первый блок сравнения, счетчик, элементы И с первого по четвертый, первый и второй элементы ИЛИ, первый и второй элементы НЕ, дешифратор и регистр адреса, выходы которого соединены с выходами дешифратора, выходы которого подключенык входам накопителя, выход первого элемента НЕ соединен с первым входом второго элемента И, второй вход которого и первый вход первого элемента И являются входом записи устройст, ва, выходы, второго и третьего элементов И соединены с входами первого элемента ИЛИ, выход которого подключен к счетному входу счетчика, выходы которого соединены с одними из информационных входов блока записи и с одними из входов первого блока сравнения, другие входы которого соединены с выходами блока считывания, выход первого блока сравнения соединен с входом второго элемента НЕ и с одним из входов четвертого элемента И, выход второго элемента НЕ соединен с одним из входов третьего элемента И, другие входы третьего и четвертого элементов И являются входом считывания устройства, выходы первого и четвертого элементов И соединены с входами второго элемента ИЛИ, выход которого соединен с входом регистра адреса, отличающееся тем, что, с целью повышения информационной с емкости устройства, в него введены регистр числа, второй блок сравнения (Л и два элемента задержки, причем инфорс мационные входы регистра-числа и одни из входов второго блока сравнения соединены и являются входами устройств ва, выходы регистра числа соединены с другими информационными входами блока записи и другими входами второго ч блока сравнения, выход которого сое- дине:н с входом первого элемента НЕ 00 и вторым входом первого элемента И, Сл выход второго элемента ИЛИ через перО вый элемент задержки соединен с входом синхронизации блока записи и рходом второго элемента задержки, выход которого подключен к установочному входу счетчика и входу синхронизации регистра числа.

| Устройство для гашения колебаний грузовой подвески крана | 1984 |

|

SU1268652A1 |

| Устройство для усиления микрофонного тока с применением самоиндукции | 1920 |

|

SU42A1 |

| Приспособление для контроля движения | 1921 |

|

SU1968A1 |

| Способ уплотнения бетонной смеси | 1973 |

|

SU483255A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-09-07—Публикация

1984-01-13—Подача