1

вейерного управленрш, выход поля логических условий которого соединен с зшравляющим входом мультиплексора логических условий j-no блока конвейерного управления, выход которого соединен с первым входом элемента ИЛИ j-ro блока конвейерного управления, выход которого соединен с К-м входом первой группы информационных входов коммутатора адреса j-ro блока конвейерного управления (где К - разрядность адреса микрокоманд), выход поля модифицируемого разряда адреса блока памяти микрокоманд j-ro блока конвейерного з равления соединен с вторым входом элемента ИЛИ j-ro блока конвейерного управления, с первого по (К-1)-и выходы поля немодифицируемых разрядов адреса блока памяти микрокоманд j-ro блока конвейерного управления соединены с первого по (К-1)-й вход первой группы информационных входов коммутатора адреса j-ro блока конвейерного управления и с информационными входами регистра кода команды j-ro блока конвейерного управления, выход поля микроопераций блока памяти микрокоманд,j-ro блока конвейерного управления соединен с информационньм входом регистра микроопераций j-ro блока конвейерного управления, выходы признака конца команды и микроопераций которого соединены соответственно с управляющими входами коммутатора адреса j-ro блока конвейерного управления и с выходом микроопераций j-ro блока конвейерного управления, выход поля признака разрешения записи блока памяти микрокоманд j-ro блока конвейерного управления соединен с входом разрешения записи регистра кода команды j-ro блока конвейерного управления, вькод которого соединен с выходом кода команды j-ro блока конвейерного управления, вход кода команды j-ro блока конвейерного управления соединен с второй группой информационных входов коммутатора адреса j-ro блока конвейерного управления, выход поля адреса команды блока памяти микрокоманд соединен с входом кода команды первого блока конвейерного управления группы, второй выход генератора тактовых им0

пульсов блока синхро1гизации соединен с первым прямым входом второго элемента И и первыми входами элемента И второй группы, Bbixojt элемента И второй группы которых соединен с входом синхронизации регистра кода команды j-ro блока конвейерного управления группы и с входом синхрониг зации регистра микроопераций j-ro блока конвейерного управления группы, выход признака конца работы которого соединен с входом установки в ноль j-ro триггера группы, выход признака кода работы первого блока конвейерного управления соединен с инверсным входом второго элемента И, выход кода команды i-ro блока конвейерного управления (, N-1) соединен с входом кода команды (i+O-ro блока конвейерного управления, вход луска устройства соединен с входом установки в единицу первого триггера группы, выход j-ro триггера ГРЗТП1ПЫ соединен.с вторыми входами j-ro элемента И первой и второй групп, выход признака кода команды i-ro блока конвейерного управления соединен с i-ми входами элементов И-НЕ первой группы, первым входом i-ro элемента И-НЕ второй группы и i-м одновибратором группы, выход которого соединен с входом установки в единицу (i+1)-ro триггера группы, выход признака конца команды N-гр блока конвейерного управления группы соединен с N-M входом каждого элемента И-НЕ первой группы А первым входом N-ro элемента второй группы, выход j-ro элемента И-НЕ первой группы соединен с вторым входом j-ro элемента И-НЕ второй группы, выход которого соединен с третьими входами J-X элементов И первой и второй групп, выход признака конца работы N-ro блока конвейерного управления группы соединен с входом установки в ноль триггера запуски блока синхронизации, выход первого элемента И соединен с вторым прямым входом второго элемента И, вькод которого соединен с входом синхронизации регистра адреса, выход признака конца команды блока памяти микрокоманд соединен с управлянщими входами коммутатора адреса..

Изобретение относится к вычислительной технике и может npiiMeHHTbCH в устройствах обработки данных с конвейерным выполнением микропрограмм.

Цель изобретения - п овышение быст- родействия микропрограммного устройства управления.

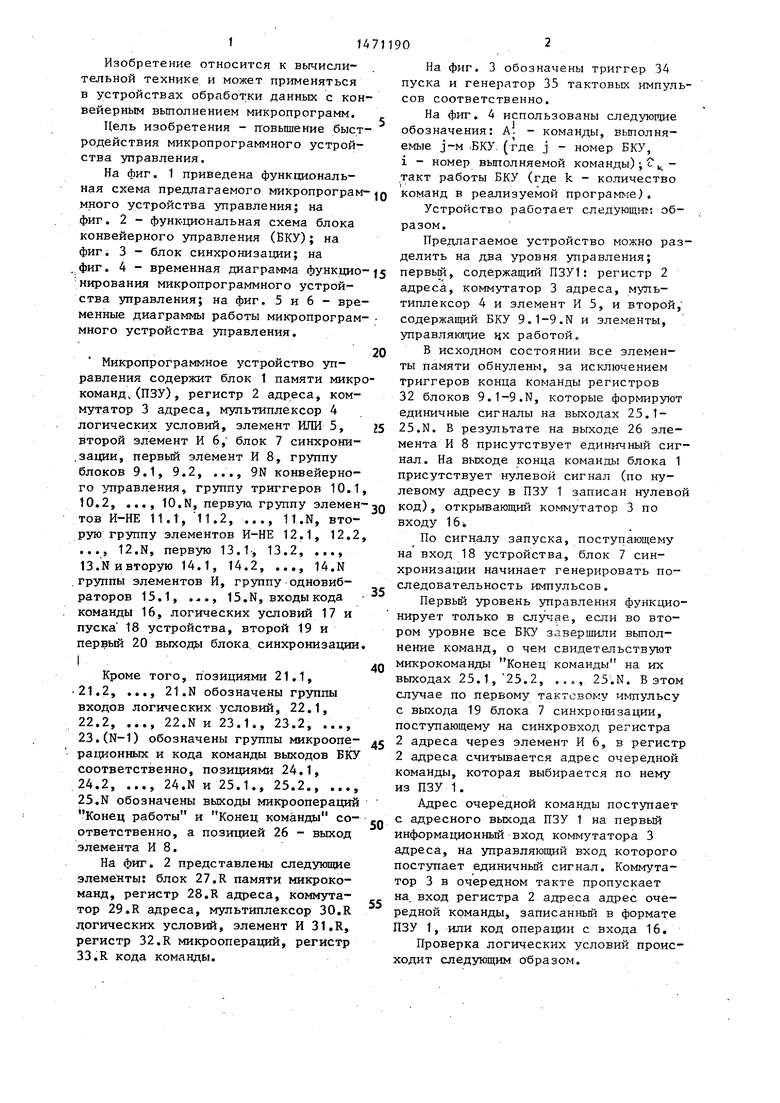

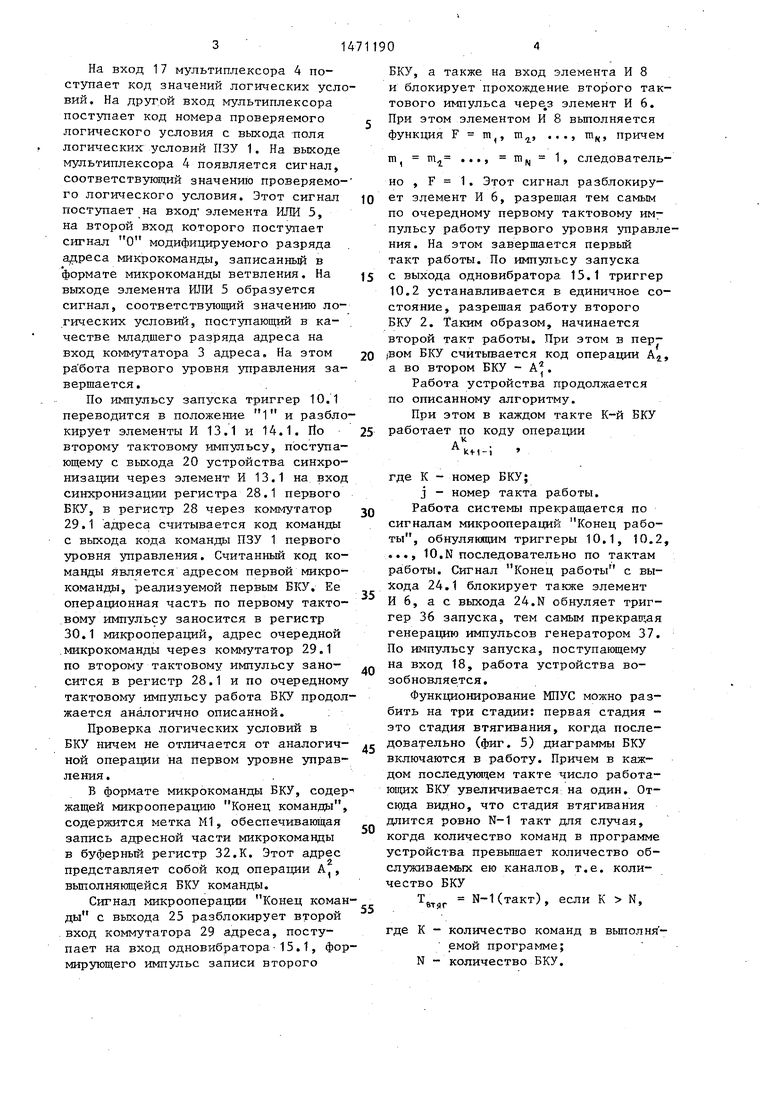

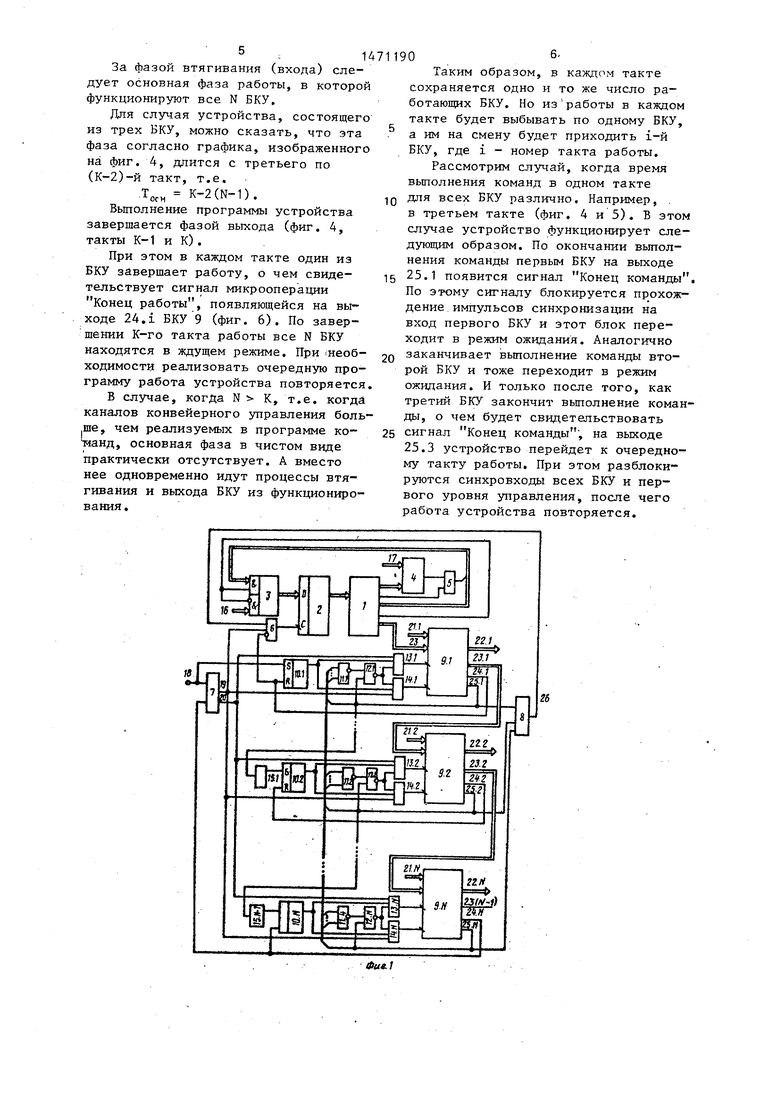

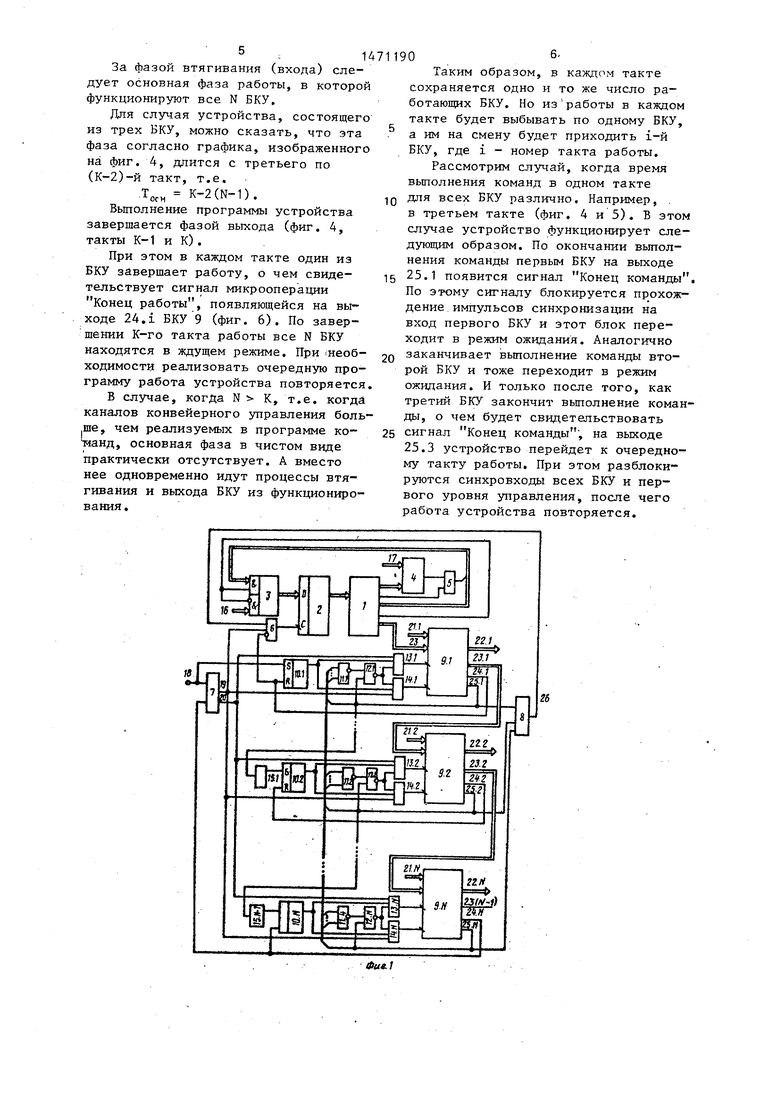

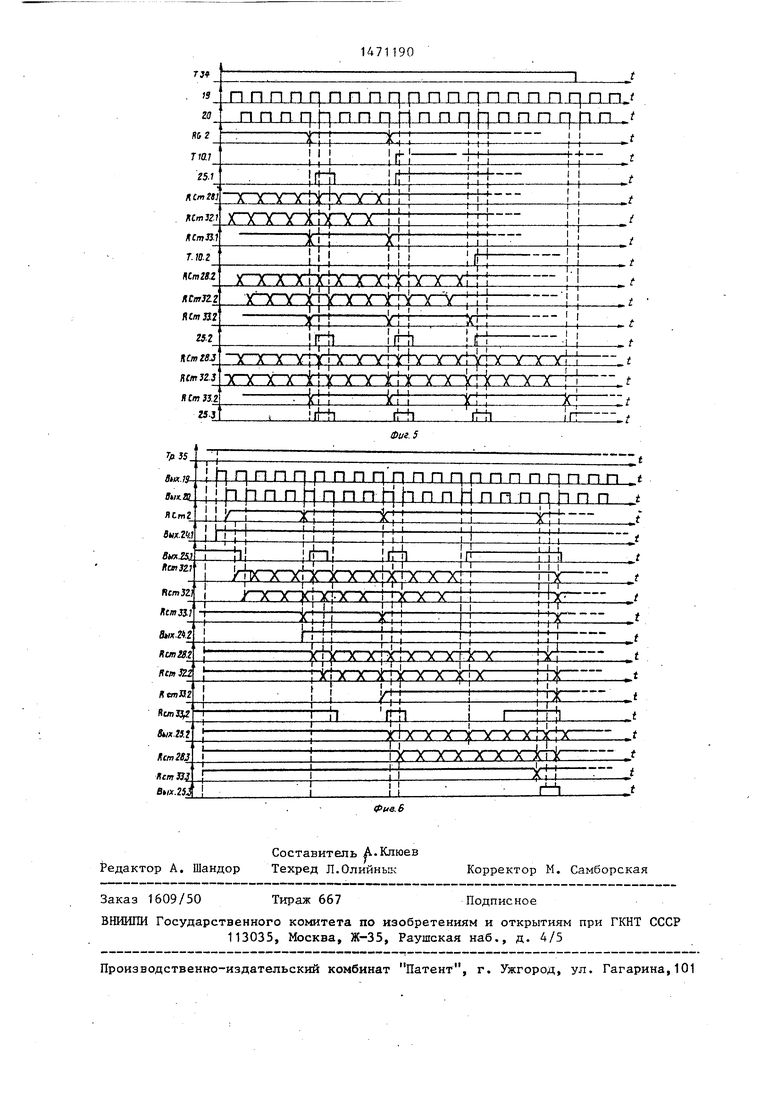

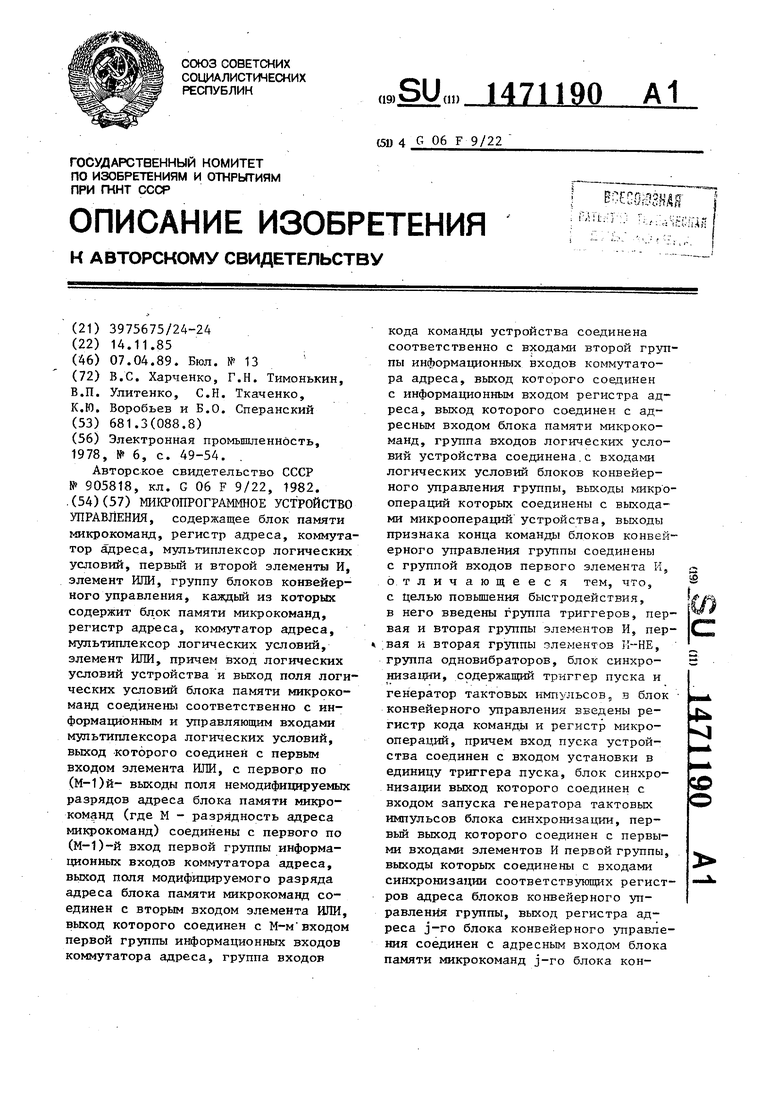

На фиг. 1 приведена функциональная схема предлагаемого микропрограм-JQ много устройства управления; на фиг. 2 - функциональная схема блока конвейерного управления (БКУ); на фиг. 3 - блок синхронизации; на фиг. 4 - временная диаграмма функцио-|5 нирования микропрограммного устройства управления; на фиг. 5 и 6 - временные диаграммы работы микропрограм- много устройства управления.

Микропрограммное устройство управления содержит блок 1 памяти микрокоманд , (ПЗУ) , регистр 2 адреса, коммутатор 3 адреса, мультиплексор 4 логических условий, элемент ИЛИ 5, 25 второй элемент И 6, блок 7 синхрони- зации, первый элемент И 8, группу блоков 9.1, 9.2, ..., 9N конвейерного управления, группу триггеров 10.1, 10.2, ..., 10.N, первую, группу элемен- о тов И-НЕ 11.1, 11.2, ..., 11.N, вторую группу элементов И-НЕ 12.1, 12.2, ..., 12.N, первзто 13.1-, 13.2, ..., 13.Мивторую 14.1, 14.2, ..., 14.N группы элементов И, группу одновиб- раторов 15.1, .., 15. N, входы кода команды 16, логических условий 17 и уска 18 устройства, второй 19 и ервый 20 выходы блока синхронизации.

40

Кроме того, позициями 21.1,

21.2, ..., 21.N обозначены группы входов логических условий, 22.1, 22.2, ..., 22.N и 23.1., 23.2, ..., 23.(К-1) обозначены группы микроопе- дг ахщонных и кода команды выходов БКУ соответственно, позициями 24.1,

24.2, ..., 24.N и 25.1., 25.2,

25.N обозначены выходы микроопераций Конец работы и Конец команды соответственно, а позицией 26 - выход элемента И 8.

На фиг. 2 представлены следующие элементы: блок 27.R памяти микрокоанд, регистр 28.R адреса, коммутаор 29.R адреса, мультиплексор 30.R огических условий, элемент И 31.R, егистр 32.R микроопераций, регистр 3.R кода команды.

50

Q 5

5о

0

г

0

На фиг. 3 обозначены триггер 34 пуска и генератор 35 тактовых импульсов соответственно.

На фиг. 4 использованы следующие обозначения: А. - команды, выполняемые J-M .БКУ. (где j - номер БКУ, i - номер выполняемой команды); Г - такт работы БКУ (где k - количество команд в реализуемой программе).

Устройство работает следующиг образом.

Предлагаемое устройство можно разделить на два уровня управления; первьш, содержащий ПЗУ1: регистр 2 адреса, коммутатор 3 адреса, мультиплексор 4 и элемент И 5, и второй, содержащий БКУ 9.1-9.N и элементы, управляю1цие ч работой.

В исходном состоянии все элементы памяти обнулены, за исключением триггеров конца команды регистров 32 блоков 9.1-9.N, которые формируют единичные сигналы на выходах 25.1- 25.N. Б результате на выходе 26 элемента И 8 присутствует единичный сигнал. На выходе конца команды блока 1 присутствует нулевой сигнал (по нулевому адресу в ПЗУ 1 записан нулевой код), открывающий коммутатор 3 по входу 16 -.

По сигналу запуска, поступающему на вход 18 устройства, блок 7 син- хронизаи ии начинает генерировать последовательность импульсов.

Первый уровень управления функционирует только в случае, если во втором уровне все БКУ завершили выполнение команд, о чем свидетельствуют микрокоманды Конец команды на их выходах 25.1, 25.2, ..., 25.N. В этом случае по первому тактовому импульсу с выхода 19 блока 7 синхронизации, поступающему на синхровход регистра 2 адреса через элемент И 6, в регистр 2 адреса считьшается адрес очередной команды, которая выбирается по нему из ПЗУ 1.

Адрес очередной команды поступает с адресного выхода ПЗУ 1 на первый информационный вход коммутатора 3 адреса, на управляющий вход которого поступает единичный сигнал. Коммутатор 3 в очередном такте пропускает на. вход регистра 2 адреса адрес очередной команды, записанный в формате ПЗУ 1, или код операции с входа 16.

Проверка логических условий происходит следующим образом.

На вход 17 мультиплексора 4 по- стуттает код значений логических условий. На другой вход мультиплексора поступает код номера проверяемого логического условия с выхода поля логически5С условий ПЗУ 1. На выходе мультиплексора 4 появляется сигнал, соответствзтощий значению проверяемого логического условия. Этот сигнал поступает на вход- элемента ИЛИ 5, на второй вход которого поступает сигнал О модифицируемого разряда a,zipeca микрокоманды, записанный в формате микрокоманды ветвления. На выходе элемента ИЛИ 5 образуется сигнал, соответствующий значению логических условий, постзшающий в качестве младшего разряда адреса на вход коммутатора 3 адреса. На этом ра бота первого уровня з равления завершается.

По импульсу запуска триггер 10, 1 переводится в положение 1 и разблокирует элементы И13,1и14,1,Йо второму тактовому импульсу, поступающему с выхода 20 устройства синхронизации через элемент И 13,1 на вход синхронизации регистра 28,1 первого БКУ, в регистр 28 через коммутатор 29,1 адреса считывается код команды с выхода кода команды ПЗУ 1 первого уровня управления. Считанный код команды является адресом первой микрокоманды, реализуемой первым БКУ, Ее операционная часть по первому тактовому импульсу заносится в регистр 30.1 микроопераций, адрес очередной .микрокоманды через коммутатор 29,1 по второму тактовому импульсу заносится в регистр 28,1 и по очередному тактовому импульсу работа ВКУ продолжается аналогично описанной. :

Проверка логических условий в БКУ ничем не отличается от аналогичной операции на первом уровне управления,

В формате микрокоманды БКУ, содер жащей микрооперацию Конец команды, содержится метка Ml, обеспечивающая запись адресной части микрокоманды в буферный регистр 32,К, Этот адрес представляет собой код операции А,, вьшолняющейся БКУ команды.

Сигнал микрооперации Конец команды с выхода 25 разблокирует второй вход коммутатора 29 адреса, поступает на вход одновибратора15.1, формирующего импульс записи второго

0

5

0

5

0

5

0

5

0

БКУ, а также на вход элемента И 8 и блокирует прохождение второго тактового импульса элемент И 6. При этом элементом И 8 выполняется функция F т, т, ,.

m

m,,

- т.. 1,

m|y, причем следовательг

1

но , F 1, Этот сигнал разблокирует элемент И 6, разрешая тем самым по очередному первому тактовому импульсу работу первого уровня управле ния. На этом завершается первый такт работы. По импульсу запуска с выхода одновибратора 15,1 триггер 10.2 устанавливается в единичное состояние, разрешая работу второго БКУ 2. Таким образом, начинается второй такт работы. При этом в пер- jBOM БКУ считывается код операции Aj а во втором БКУ А,

Работа устройства продолжается по описанному алгоритму.

При этом в каждом такте К-й БКУ

работает по коду операции д к

Kt1-i

где К - номер БКУ;

j - номер такта работы,

Работа системы прекращается по сигналам микроопераций Конец работы, обнуляющим триггеры 10,1, 10.2, ..., 10,N последовательно по тактам работы. Сигнал Конец работы с выхода 24,1 блокирует также элемент И 6, а с выхода 24.N обнуляет триггер 36 запуска, тем самым прекращая генерацию импульсов генератором 37, По импульсу запуска, поступающет гу на вход 18, работа устройства возобновляется ,

Функционирование МПУС можно разбить на три стадии: первая стадия - это стадия втягивания, когда последовательно (фиг, 5) диаграммы БКУ включаются в работу. Причем в каждом последую1чем такте число работающих БКУ увеличивается на один. Отсюда видно, что стадия втягивания длится ровно N-1 такт для случая, когда количество команд в программе устройства превышает количество обслуживаемых ею каналов, т,е, количество БКУ

55

втяг

Ы-1(такт), если К N,

где К - количество команд в выполня -

емой программе; N - количество БКУ.

:iS

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное управляющее устройство | 1987 |

|

SU1527634A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1256026A1 |

| Конвейерная система для программного управления | 1989 |

|

SU1665340A1 |

| Устройство для микропрограммного управления и контроля | 1987 |

|

SU1497621A1 |

| Устройство для управления,контроля и диагностирования | 1985 |

|

SU1297063A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1310817A1 |

| Распределенная система для программного управления с мажоритированием | 1990 |

|

SU1727112A1 |

| Программируемый управляющий модуль | 1989 |

|

SU1649507A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

Использование: в электронной промышленности, в частности в вычислительных машинах. Сущность изобретения: в устройство введены группа триггеров, первая и вторая группы элементов И, первая и вторая группы элементов И-НЕ, группа одновибраторов, блок синхронизации, содержащий григгер пуска и генератор тактовых импульсов, в блок конвейерного управления введены регистр кода команды и регистр микроопераций.

Фи«.Л

| Электронная промьшшеннбсть, 1978, № 6, с | |||

| Способ смешанной растительной и животной проклейки бумаги | 1922 |

|

SU49A1 |

| Микропрограммное устройство управления | 1979 |

|

SU905818A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1989-04-07—Публикация

1985-11-14—Подача