ел ел о ел ел

00

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сжатия информации | 1987 |

|

SU1529043A1 |

| Устройство для сжатия информации | 1981 |

|

SU972544A1 |

| Устройство для управления процессом смешения жидких продуктов | 1985 |

|

SU1272314A1 |

| Устройство для ввода и вывода информации | 1982 |

|

SU1048466A1 |

| Устройство временной автоматической регулировки усиления | 1989 |

|

SU1704116A1 |

| Устройство для временного сжатия входного сигнала | 1982 |

|

SU1100632A1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| Устройство для отображения графической информации | 1984 |

|

SU1223283A1 |

| Измеритель переходных характеристик | 1986 |

|

SU1388833A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ В АДАПТИВНЫХ ТЕЛЕМЕТРИЧЕСКИХ СИСТЕМАХ | 1995 |

|

RU2103745C1 |

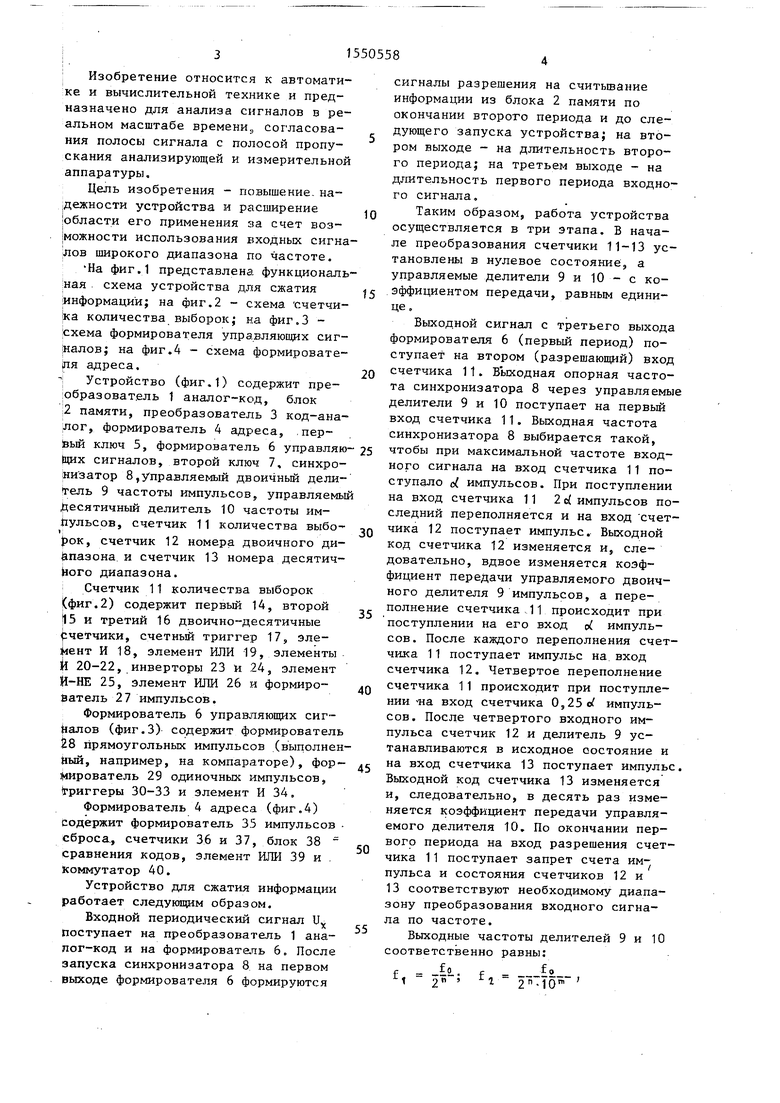

Изобретение относится к автоматике и вычислительной технике и предназначено для анализа сигналов в реальном масштабе времени, согласования полосы сигнала с полосой пропускания анализирующей и измерительной аппаратур. Цель изобретения - повышение надежности устройства и расширение области его применения за счет возможности использования входных сигналов широкого диапазона по частоте. Устройство содержит преобразователь 1 аналог - код, преобразователь 3 код - аналог, блок 2 памяти, формирователь 4 адреса, формирователь 6 управляющего сигнала, ключи 5, 7, синхронизатор 8, управляемый двоичный делитель 9 частоты сигнала, управляемый десятичный делитель 10 частоты сигнала, счетчик 11 количества выборок, счетчик 12 номера двоичного диапазона, счетчик 13 номера десятичного диапазона. 3 з.п. ф-лы, 4 ил.

ФигЛ

Изобретение относится к автоматике и вычислительной технике и предназначено для анализа сигналов в реальном масштабе времени, согласования полосы сигнала с полосой пропускания анализирующей и измерительной аппаратуры.

Цель изобретения - повышение надежности устройства и расширение области его применения за счет возможности использования входных сигналов широкого диапазона по частоте.

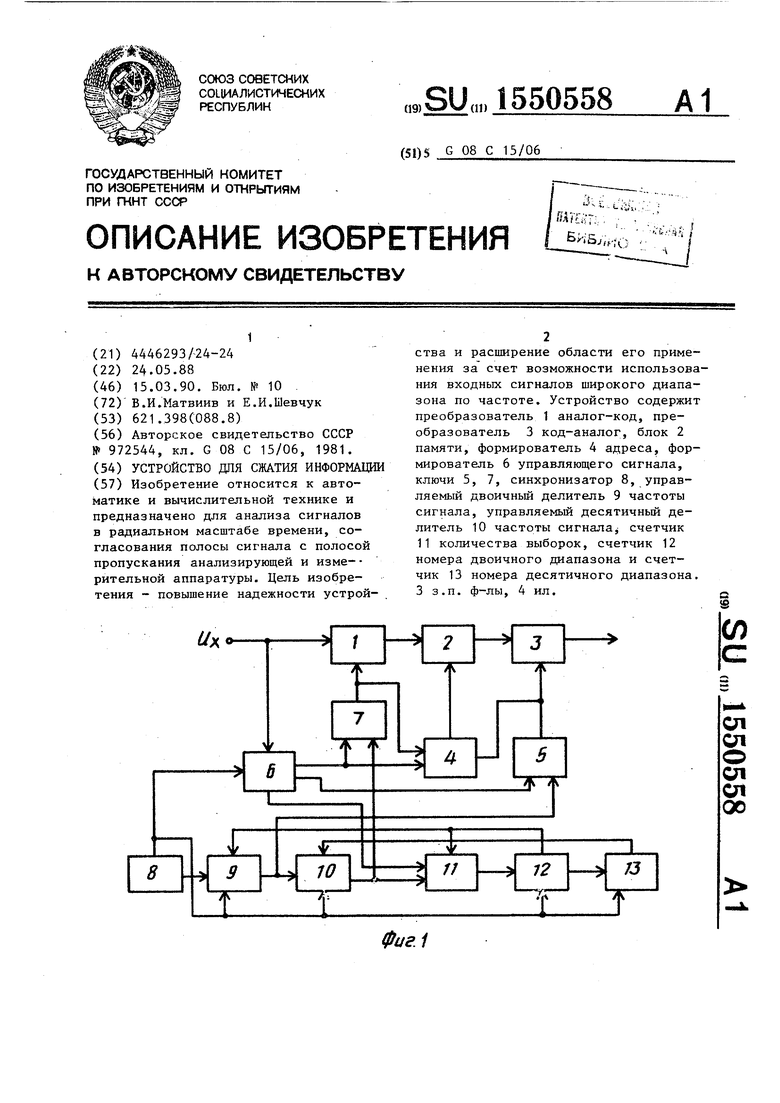

На фиг.1 представлена функциональная схема устройства для сжатия информации; на фиг.2 - схема счетчика количества выборок; на фиг.З - схема формирователя управляющих сигналов; на фиг.4 - схема формирователя адреса.

Устройство (фиг.1) содержит преобразователь 1 аналог-код, блок 2 памяти, преобразователь 3 код-аналог, формирователь 4 адреса, первый ключ 5, формирователь 6 управляющих сигналов, второй ключ 7, синхронизатор 8,управляемый двоичный делитель 9 частоты импульсов, управляемы Десятичный делитель 10 частоты импульсов, счетчик 11 количества выборок, счетчик 12 номера двоичного диапазона и счетчик 13 номера десятич- horo диапазона.

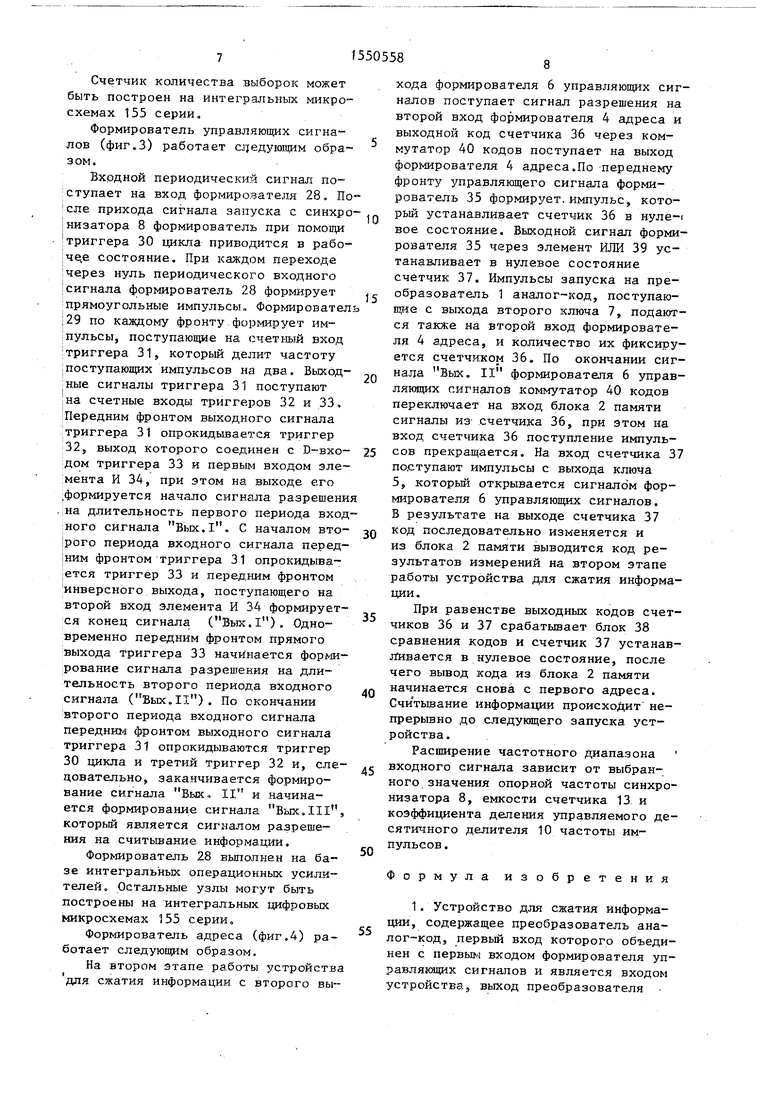

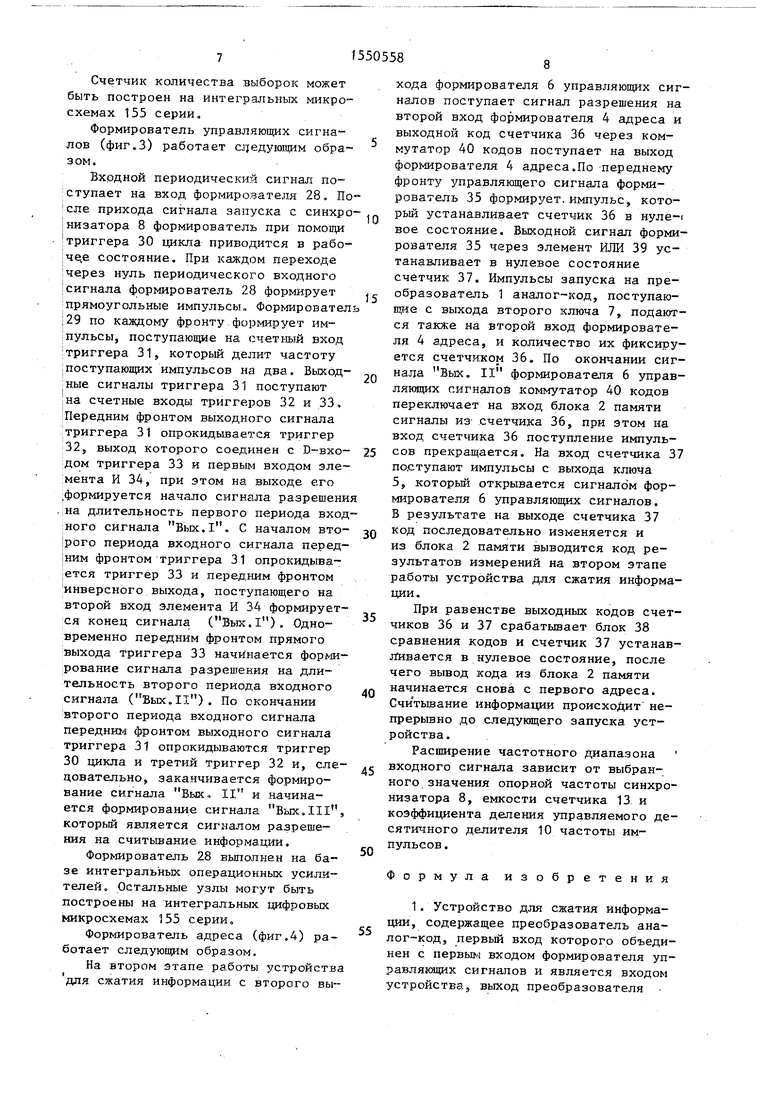

Счетчик 11 количества выборок (фиг.2) содержит первый 14, второй 15 и третий 16 двоично-десятичные счетчики, счетньй триггер 17, эле- йент И 18, элемент ИЛИ 19, элементы И 20-22, инверторы 23 и 24, элемент Й-НЕ 25, элемент ИЛИ 26 и формирователь 27 импульсов.

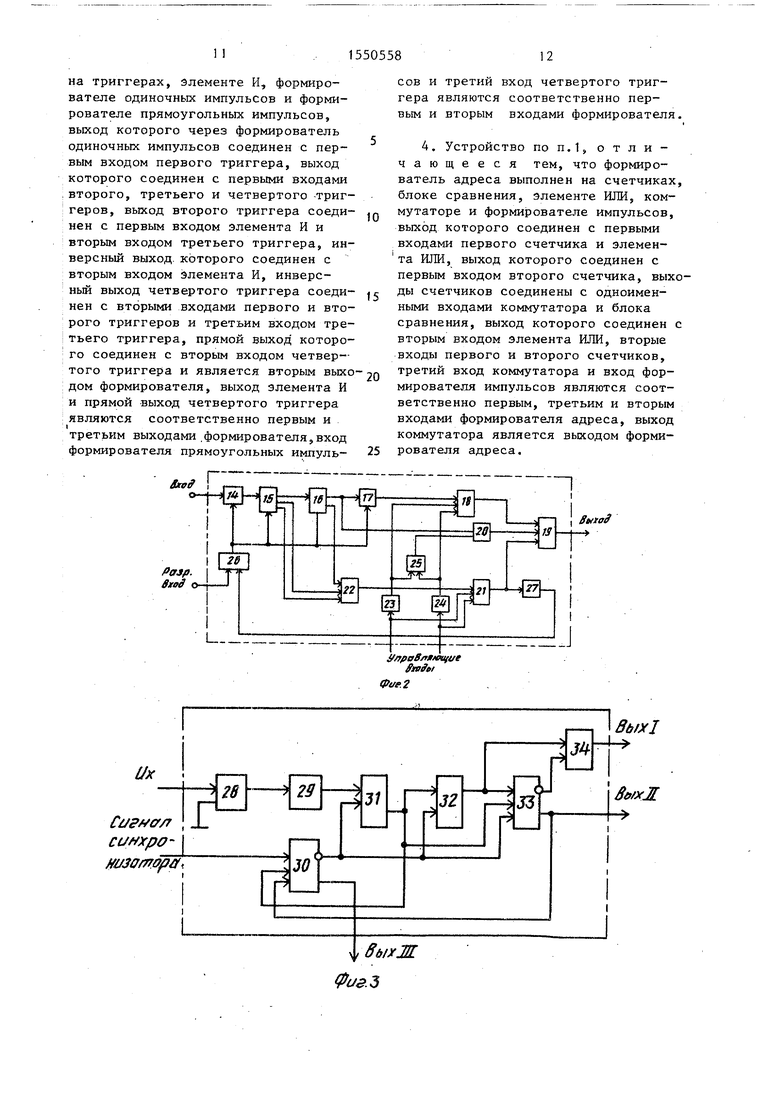

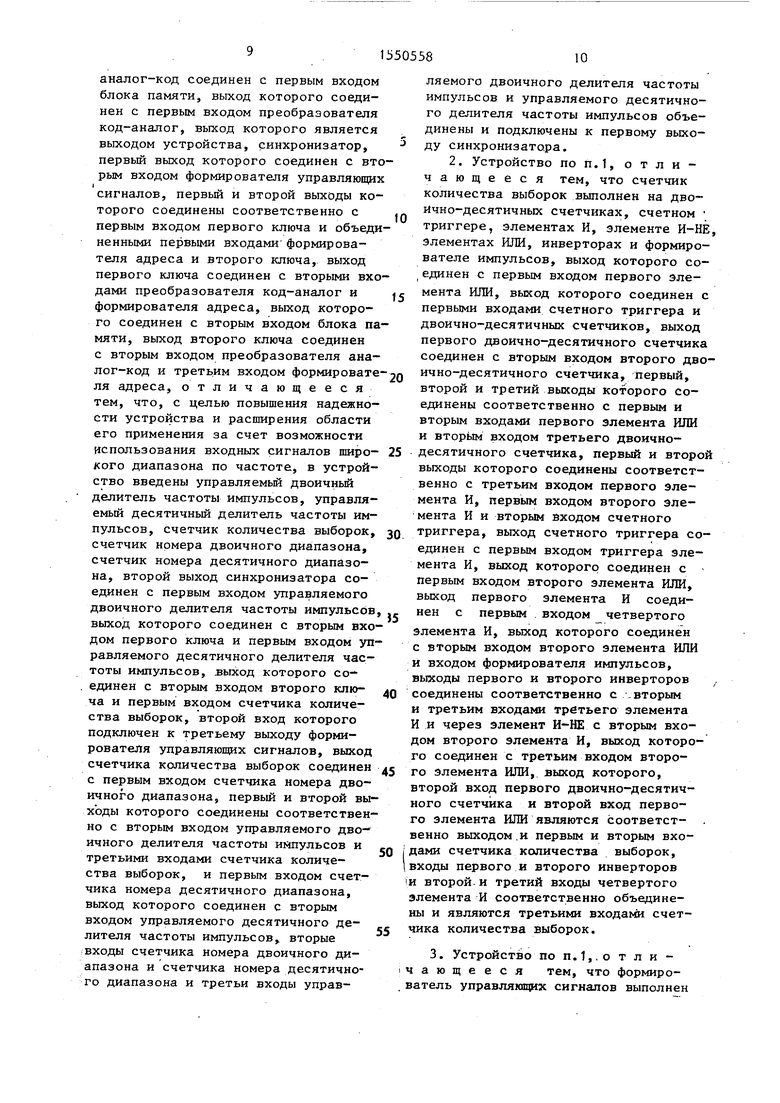

Формирователь 6 управляющих сиг- йалов (фиг.З) содержит формирователь 28 прямоугольных импульсов (выполненный, например, на компараторе), фор- ирователь 29 одиночных импульсов, триггеры 30-33 и элемент И 34.

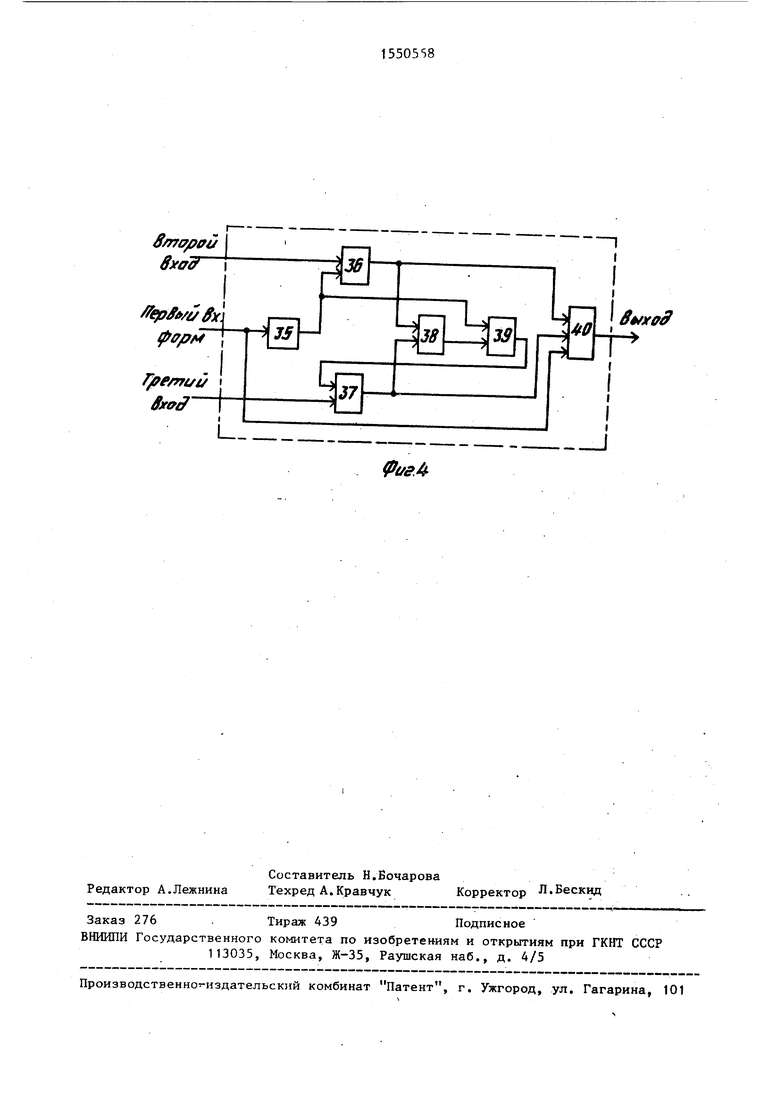

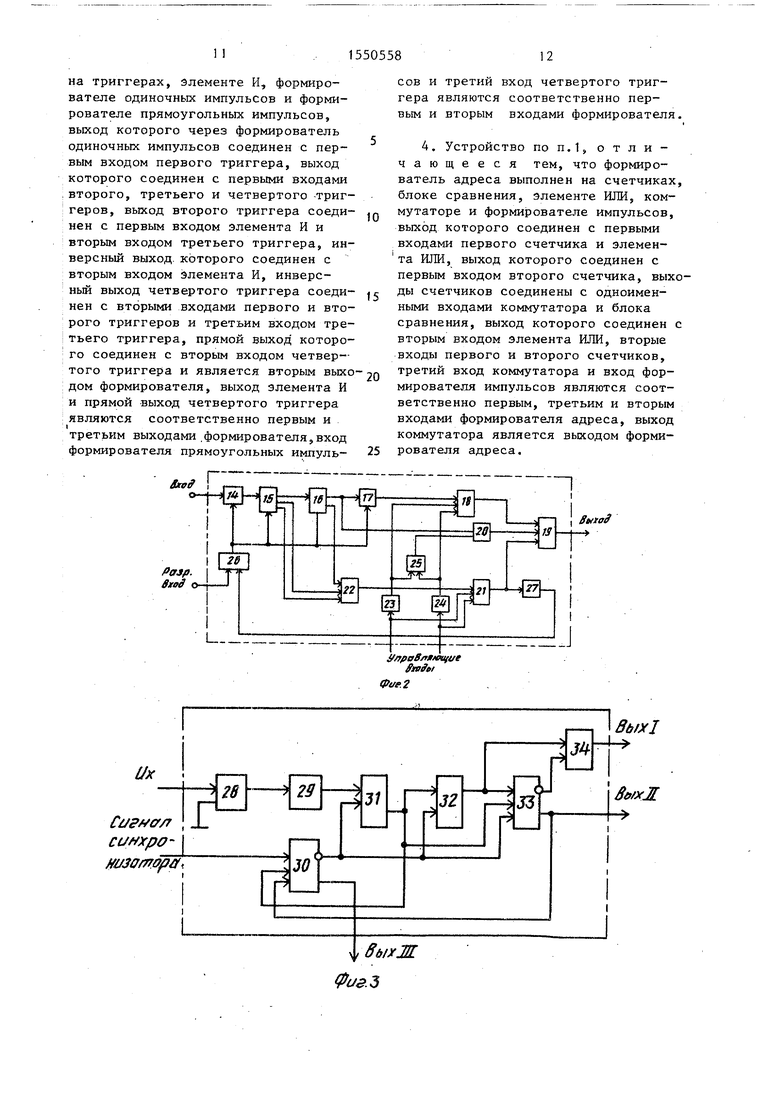

Формирователь 4 адреса (фиг.4) содержит формирователь 35 импульсов сброса, счетчики 36 и 37, блок 38 сравнения кодов, элемент ИЛИ 39 и коммутатор 40.

Устройство для сжатия информации работает следующим образом.

Входной периодический сигнал Ux Поступает на преобразователь 1 аналог-код и на формирователь 6 После запуска синхронизатора 8 на первом Выходе формирователя 6 формируются

0

5

0

5

0

5

0

5

0

5

сигналы разрешения на считывание информации из блока 2 памяти по окончании второго периода и до следующего запуска устройства; на втором выходе - на длительность второго периода; на третьем выходе - на длительность первого периода входного сигнала.

Таким образом, работа устройства осуществляется в три этапа. Б начале преобразования счетчики 11-13 установлены в нулевое состояние, а управляемые делители 9 и 10 - с коэффициентом передачи, равным единице.

Выходной сигнал с третьего выхода формирователя 6 (первый период) поступает на втором (разрешающий) вход счетчика 11. Выходная опорная частота синхронизатора 8 через управляемые делители 9 и 10 поступает на первый вход счетчика 11. Выходная частота синхронизатора 8 выбирается такой, чтобы при максимальной частоте входного сигнала на вход счетчика 11 поступало d импульсов. При поступлении на вход счетчика 11 2 « импульсов последний переполняется и на вход счетчика 12 поступает импульс. Выходной код счетчика 12 изменяется и, следовательно, вдвое изменяется коэффициент передачи управляемого двоичного делителя 9 импульсов, а переполнение счетчика 11 происходит при поступлении на его вход е импульсов. После каждого переполнения счетчика 11 поступает импульс на вход счетчика 12. Четвертое переполнение счетчика 11 происходит при поступлении на вход счетчика 0,25о импульсов. После четвертого входного импульса счетчик 12 и делитель 9 устанавливаются в исходное состояние и на вход счетчика 13 поступает импульс. Выходной код счетчика 13 изменяется и, следовательно, в десять раз изменяется коэффициент передачи управляемого делителя 10. По окончании первого периода на вход разрешения счетчика 11 поступает запрет счета импульса и состояния счетчиков 12 и 13 соответствуют необходимому диапазону преобразования входного сигнала по частоте.

Выходные частоты делителей 9 и 10 соответственно равны: fo

г - --- f - J-1 - on L 1

где fc - опорная частота синхрони-

низатора 8;

п - состояние счетчика 12; m - состояние счетчика 13.

Таким образом, в течение первого периода входного сигнала осуществляется выбор частоты fг для запуска преобразователя 1 аналог-код и f1 для вывода кода из блока 2 памяти

На втором этапе работы устройства (второй период входного .сигнала) на формирователь 4 адреса и на ключ 7 поступает сигнал разрешения с выхода формирователя 6. С выбранной частотой f, осуществляются запуск преобразователя 1 аналог-код и запись полученных результатов измерений входного сигнала в блок 2 памяти.

По окончании второго периода входного сигнала блок 2 памяти оказывается заполненным от до 2с( выборочными значениями, второй ключ 7 заперт, а первый ключ 5 открывается сигналом разрешения с первого выхода формирователя 6. Начинается третий этап работы устройства - считывание информации из блока 2 памяти и ее преобразование в аналоговую форму в преобразователе 3 код-аналог. Частота Ј, поступает на тактирование формирователя 4 и преобразователя 3 код-аналог с выхода ключа 5. Количество выборок N за период входного сигнала U у находится в диапазоне о( N

у находится i 2 L и равно

N

fa

TVfL 2 10 m

Tn - период входного сигнала.

,где

1 Считывание информации происходит непрерывно до следующего запуска устройства. Начало третьего этапа работы означает конец преобразования временного (спектрального) масштаба входного периодического сигнала.

Масштаб преобразования по частоте равен:

К,

10Г

При поступлении четвертого импульса на вход счетчика 12 номера двоичСчетчик количества выборок (фиг.2) ного диапазона выходной код его равен

нулевому коду. Таким образом процесс работы счетчика количества выборок

работает следующим образом.

В исходном состоянии двоично-десятичные счетчики 14-16 и счетный

повторяется,

0

5

0

5

0

5

0

5

0

триггер 17 находятся в нулевом состоянии. После прихода на разрешающий вход счетчика количества выборок разрешающего сигнала на счетный вход двоично-десятичного счетчика 14 поступает максимальная частота, а на управляющие входы - нулевой код. Выходная частота синхронизатора 8 выбирается такой, чтобы за минимальный период входного сигнала на счетчик поступило е/ импульсов. При использовании трех двоично-десятичных счетчиков о 1000. В начальный момент разрешающий сигнал поступает на второй и третий входы элемента И 18. После прихода на вход счетчика 2 rf им-, пульсов счетный триггер 17 опрокидывается и его выходной импульс через элементы И 18 и ИЛИ 19 поступает на выход, т.е. на вход счетчика 12 номера двоичного диапазона, в результате на его выходе код изменяется и поступает на управляющий вход счетчика 11 количества выборок. Элемент И 18 закрывается, а элемент И 20 открывается. После прихода на вход счетчика 11 количества выборок с/ импульсов на выходе двоично-десятичного счетчика 16 формируется импульс, который через элемент И 20 и элемент ИЛИ 19 поступает на выход.

После прихода на вход счетчика 12 номера двоичного диапазона трех импульсов его выходной код закрывает элемент И 20 и открывает элемент И 21.

После прихода на вход двоично-десятичного счетчика 14 количества импульсов, равного 0,25Ы, на выходе элемента И 22 формируется импульс, который через элемент И 21 и элемент ИЛИ 19 поступает на выход счетчика 11 количества выборок, а следовательно, на вход счетчика 12 номера двоичного диапазона.

При этом формирователь 27 импульсов формирует импульс, который через элемент ИЛИ 26 устанавливает двоично- десятичные счетчики 14-16 и счетный триггер 17 в исходное состояние.

повторяется,

Счетчик количества выборок может быть построен на интегральных микросхемах 155 серии.

Формирователь управляющих сигналов (фиг.З) работает следующим образом.

Входной периодический сигнал поступает на вход формирователя 28. По еле прихода сигнала запуска с синхронизатора 8 формирователь при помощи триггера 30 цикла приводится в рабо- че,е состояние. При каждом переходе через нуль периодического входного сигнала формирователь 28 формирует прямоугольные импульсы™ Формировател 29 по каждому фронту формирует импульсы, поступающие на счетный вход триггера 31, который делит частоту поступающих импульсов на два. Выходные сигналы триггера 31 поступают на счетные входы триггеров 32 и 33, Передним фронтом выходного сигнала триггера 31 опрокидывается триггер 32, выход которого соединен с D-вхо- дом триггера 33 и первым входом элемента И 34, при этом на выходе его .формируется начало сигнала разрешени на длительность первого периода входного сигнала Вых.1. С началом второго периода входного сигнала передним фронтом триггера 31 опрокидывается триггер 33 и передним фронтом инверсного выхода, поступающего на второй вход элемента И 34 формируется конец сигнала (Вых.1). Одновременно передним фронтом прямого выхода триггера 33 начинается формирование сигнала разрешения на длительность второго периода входного сигнала (Вых.II). По скончании второго периода входного сигнала передним фронтом выходного сигнала триггера 31 опрокидываются триггер 30 цикла и третий триггер 32 и, следовательно, заканчивается формирование сигнала Вых. II и начинается формирование сигнала Вых.III, который является сигналом разрешения на считывание информации.

Формирователь 28 выполнен на базе интегральных операционных усилителей. Остальные узлы могут быть построены на интегральных цифровых микросхемах 155 серии.

Формирователь адреса (фиг.4) работает следующим образом.

На втором этапе работы устройства для сжатия информации с второго вы-

5

0

5

0

5

0

5

0

5

хода формирователя 6 управляющих сигналов поступает сигнал разрешения на второй вход формирователя 4 адреса и выходной код счетчика 36 через коммутатор 40 кодов поступает на выход формирователя 4 адреса.По переднему фронту управляющего сигнала формирователь 35 формирует, импульс, который устанавливает счетчик 36 в нуле-i вое состояние. Выходной сигнал формирователя 35 через элемент ИЛИ 39 устанавливает в нулевое состояние счетчик 37. Импульсы запуска на преобразователь 1 аналог-код, поступающие с выхода второго ключа 7, подаются также на второй вход формирователя 4 адреса, и количество их фиксируется счетчиком 36. По окончании сигнала Вых. II формирователя 6 управляющих сигналов коммутатор 40 кодов переключает на вход блока 2 памяти сигналы из счетчика 36, при этом на вход счетчика 36 поступление импульсов прекращается. На вход счетчика 37 поступают импульсы с выхода ключа 5, который открывается сигналом формирователя 6 управляющих сигналов. В результате на выходе счетчика 37 код последовательно изменяется и из блока 2 памяти выводится код результатов измерений на втором этапе работы устройства для сжатия информации.

При равенстве выходных кодов счетчиков 36 и 37 срабатывает блок 38 сравнения кодов и счетчик 37 устанавливается в нулевое состояние, после чего вывод хода из блока 2 памяти начинается снова с первого адреса. Считывание информации происходит непрерывно до следующего запуска устройства.

Расширение частотного диапазона входного сигнала зависит от выбранного значения опорной частоты синхронизатора 8, емкости счетчика 13 и коэффициента деления управляемого десятичного делителя 10 частоты импульсов.

Формула изобретения

аналог-код соединен с первым входом блока памяти, выход которого соединен с первым входом преобразователя код-аналог, выход которого является выходом устройства, синхронизатор, первый выход которого соединен с вторым входом формирователя управляющих сигналов, первый и второй выходы которого соединены соответственно с первым входом первого ключа и объединенными первыми входами формирователя адреса и второго ключа, выход первого ключа соединен с вторыми входами преобразователя код-аналог и формирователя адреса, выход которого соединен с вторым входом блока памяти, выход второго ключа соединен с вторым входом преобразователя аналог-код и третьим входом формировате ля адреса, отличающееся тем, что, с целью повышения надежности устройства и расширения области его применения за счет возможности использования входных сигналов широ- кого диапазона по частоте, в устройство введены управляемьй двоичньй делитель частоты импульсов, управляемый десятичный делитель частоты импульсов, счетчик количества выборок, счетчик номера двоичного диапазона, счетчик номера десятичного диапазона, второй выход синхронизатора соединен с первым входом управляемого двоичного делителя частоты импульсов, выход которого соединен с вторым входом первого ключа и первым входом управляемого десятичного делителя частоты импульсов, выход которого соединен С ВТОРЫМ ВХОДОМ ВТОРОГО КЛЮ-

ча и первым входом счетчика количества выборок, второй вход которого подключен к третьему выходу формирователя управляющих сигналов, выход счетчика количества выборок соединен с первым входом счетчика номера двоичного диапазона, первый и второй выходы которого соединены соответственно с вторым входом управляемого двоичного делителя частоты импульсов и третьими входами счетчика количества выборок, и первым входом счетчика номера десятичного диапазона, выход которого соединен с вторым входом управляемого десятичного делителя частоты импульсов, вторые входы счетчика номера двоичного диапазона и счетчика номера десятичного диапазона и третьи входы управ

5

J ,д д25 30 4Q

лс

}5

50

5

ляемого двоичного делителя частоты импульсов и управляемого десятичного делителя частоты импульсов объединены и подключены к первому выходу синхронизатора.

на триггерах, элементе И, формирователе одиночных импульсов и формирователе прямоугольных импульсов, выход которого через формирователь одиночных импульсов соединен с первым входом первого триггера, выход которого соединен с первыми входами второго, третьего и четвертого триггеров, выход второго триггера соединен с первым входом элемента И и вторым входом третьего триггера, инверсный выход которого соединен с вторым входом элемента И, инверсный выход четвертого триггера соединен с вторыми входами первого и второго триггеров и третьим входом третьего триггера, прямой выход которого соединен с вторым входом четвертого триггера и является вторым выхо дом формирователя, выход элемента И и прямой выход четвертого триггера являются соответственно первым и третьим выходами формирователя,вход формирователя прямоугольных импуль

Ux

Сиг#0/7 J синхро-1

#ШО/7Т0р#

0

Q

5

5

сов и третий вход четвертого триггера являются соответственно первым и вторым входами формирователя.

ЗноаЗ

S/apaS/nnouft/e ffmfoi

Фае 2

I Вых

I

feX4

| Устройство для сжатия информации | 1981 |

|

SU972544A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1990-03-15—Публикация

1988-05-24—Подача