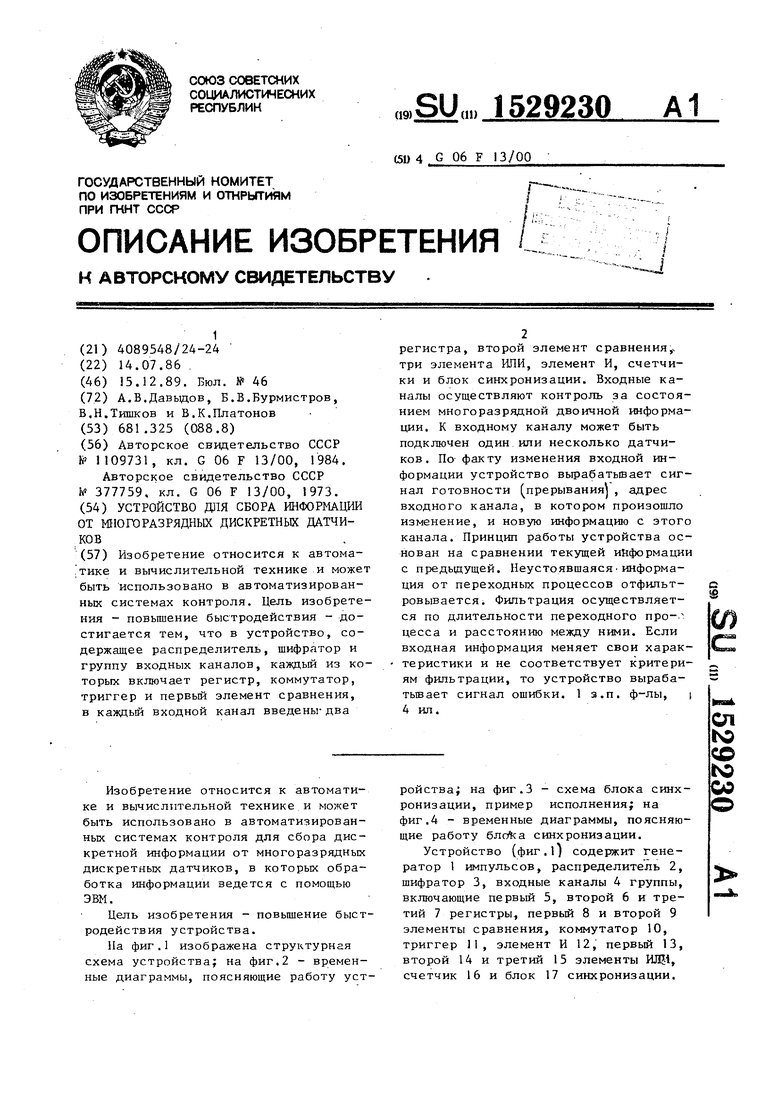

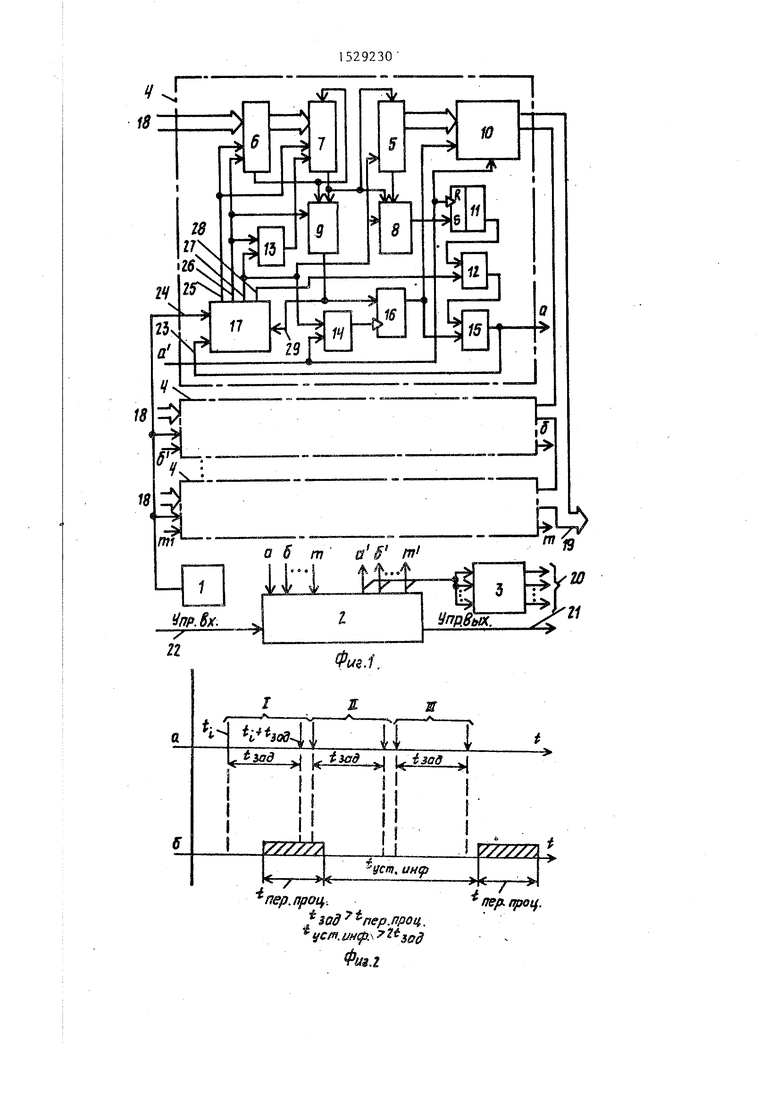

. На фиг.1 также обозначены входы и выходы 18-22 устройства и внешние связи 23-29 блока 17 синхронизации.

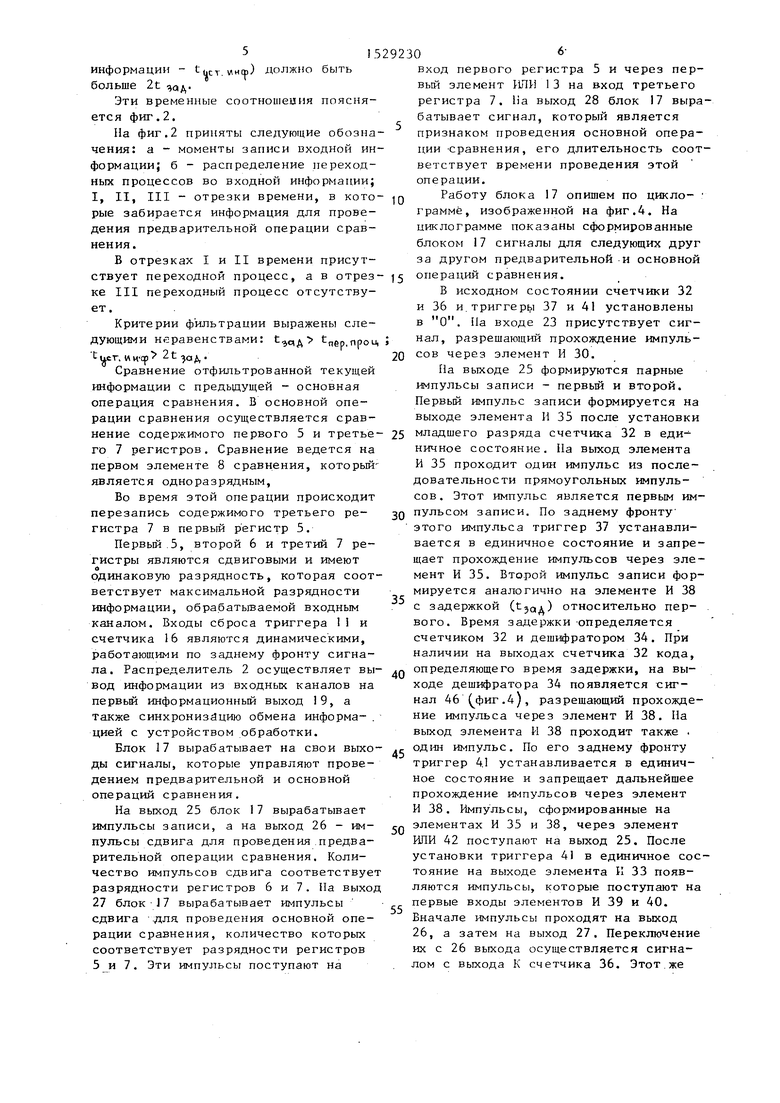

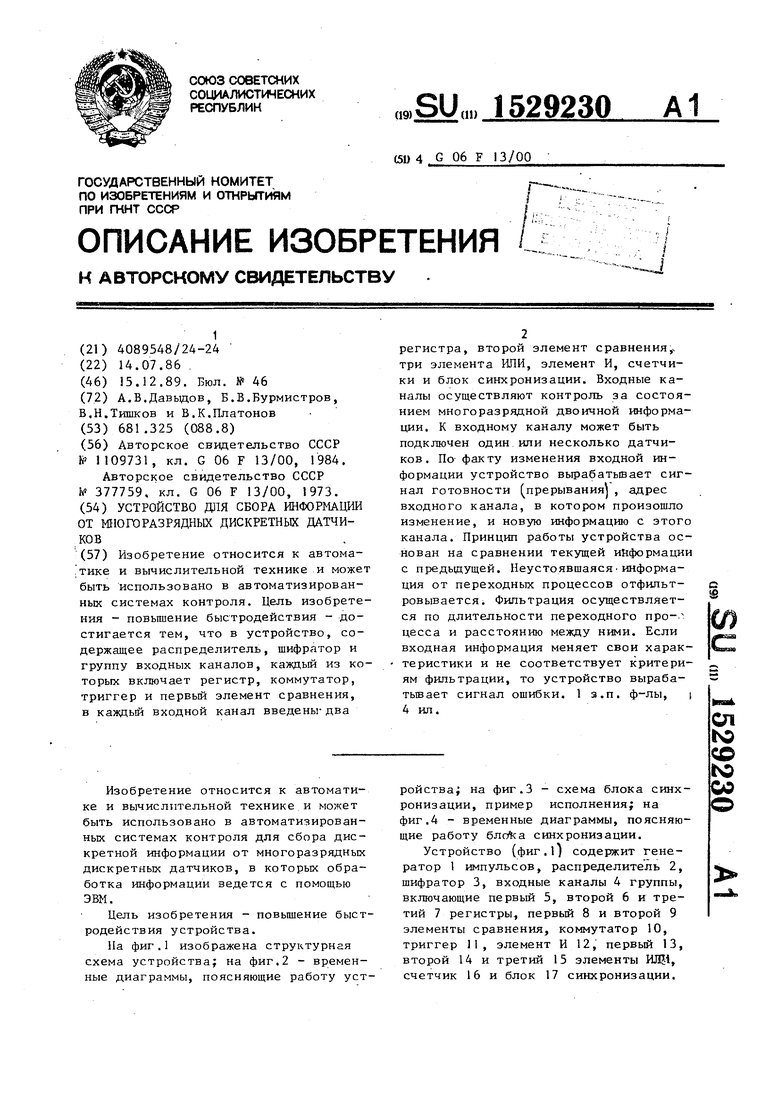

Блок 17 синхронизации (фиг.З) об- :разуют элемент И 30, элемент ГШИ 31, I счетчик 32, элемент И 33, дешифратор 134, элемент И 35, счетчик 36, триггер | 37, три элемента И 38-40, триггер 41 и элемент ИЛИ 42, На фиг.З также обозначены линии 43-49 внутренних связей блсгка.

Ус тройство осуществляет контроль за состоянием многоразрядной дво1ет ной ,информации, поступающей на информационные входы 18 входных каналов 4. При изменении этой информации хотя бы в одном разряде устройство .выраба- тьшает на своих выходах 21, 20 и 19

второй 6 и третий 7 регистры в момен ты времени tj и + ад, где tj - текущий, момент времени; ,д - время задержки относительно текущего момен та времени.

В третий регистр. записывается информация на момент времени t;, а во второй регистр 6 - на момент времени t; + tj(,. . Эта запись производится двумя импульсами записи, следующими с рштервалом времени, равным ЗаД из первые управляющие входы второго 6 и третьего 7 регистров; с Первый импульс записи записывает

входную информацию на момент времени t{ во второй регистр 6, а второй импульс записи переписывает информацию записанную на момент времени t|, из

10

сигнал готовности, адрес входного ка- пп второго регистра 6 в третий регистр нала 4, в котором произошло измене- ние.,- и- информацию с этого канала.

Устройство обработки, получив сигнал готовности, производит считьшание информации с выходов 19 и 20 и вьща- 25 ет сигнал ответа на вход 22, разре- щающий устройству вьщачу следующей информации. На время вывода информации входной канал, с которого этот вывод осуществляется, прекращает еле- жение за состоянием входной информации. При возникновении изменения одновременно в нескольких входных каналах устройство последовательно вы7 и записьшает во второй регистр 6 информацию на момент времени t- + Информация на выходах регис ров 6 и 7 изменяется по заднему фрон ту импульса записи. Сравнение содер жимого регистров 6 и 7 производится на втором элементе 9 сравнения; во время этой операции происходит пере запись содержимого второго регистра 6 в третий регистр 7. Элемент 9 срав нения одноразрядньй, и сравнение ве дется пбследовательным способом. Ес ли информация, записанная в указанн моменты, одинаковая, то она допуска

второй 6 и третий 7 регистры в моменты времени tj и + ад, где tj - текущий, момент времени; ,д - время задержки относительно текущего момента времени.

В третий регистр. записывается информация на момент времени t;, а во второй регистр 6 - на момент времени t; + tj(,. . Эта запись производится двумя импульсами записи, следующими с рштервалом времени, равным ЗаД из первые управляющие входы второго 6 и третьего 7 регистров; Первый импульс записи записывает

входную информацию на момент времени t{ во второй регистр 6, а второй импульс записи переписывает информацию, записанную на момент времени t|, из

второго регистра 6 в третий регистр

7 и записьшает во второй регистр 6 информацию на момент времени t- + Информация на выходах регистров 6 и 7 изменяется по заднему фронту импульса записи. Сравнение содержимого регистров 6 и 7 производится на втором элементе 9 сравнения; во время этой операции происходит перезапись содержимого второго регистра 6 в третий регистр 7. Элемент 9 сравнения одноразрядньй, и сравнение ведется пбследовательным способом. Если информация, записанная в указанные моменты, одинаковая, то она допускает

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации от двухпозиционных датчиков | 1985 |

|

SU1280640A1 |

| Устройство для фиксации неустойчивых сбоев | 1985 |

|

SU1265777A1 |

| Устройство для ввода информации от двухпозиционных датчиков | 1984 |

|

SU1156053A1 |

| Устройство для вычисления логических функций | 1983 |

|

SU1233160A1 |

| Устройство для формирования управляющей информации при обработке данных сейсмических колебаний | 1981 |

|

SU1000766A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для управления шаговым двигателем | 1989 |

|

SU1646036A2 |

| Устройство для контроля программ | 1987 |

|

SU1439601A1 |

| Устройство для сопряжения абонентов с каналами связи | 1984 |

|

SU1233158A1 |

| Кольцевая система для обмена информацией | 1988 |

|

SU1550522A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в автоматизированных системах контроля. Цель изобретения - повышение быстродействия - достигается тем, что в устройство, содержащее распределитель, шифратор и группу входных каналов, каждый из которых включает регистр, коммутатор, триггер и первый элемент сравнения, в каждый входной канал введены два регистра, второй элемент сравнения, три элемента ИЛИ, элемент И, счетчики и блок синхронизации. Входные каналы осуществляют контроль за состоянием многоразрядной двоичной информации. К входному каналу может быть подключен один или несколько датчиков. По факту изменения входной информации устройство вырабатывает сигнал готовности (прерывания), адрес входного канала, в котором произошло изменение, и новую информацию с этого канала. Принцип работы устройства основан на сравнении текущей информации с предыдущей. Неустоявшаяся информация от переходных процессов отфильтровывается. Фильтрация осуществляется по длительности переходного процесса и расстоянию между ними. Если входная информация меняет свои характеристики и не соответствует критериям фильтрации, то устройство вырабатывает сигнал ошибки. 1 з.п. ф-лы, 4 ил.

i водит информацию с этих каналов, при- ся для сравнения с предьщущей инфорчем тот канал, с когопого вывод закончен , продо жает дальнейщее слежение за состоянием входной информации Принцип работы устройства основав на сравнении текущей информации с предыдущей. Предыдущая информация хранится в первом регистре 5. Вря или часть входной информации любого канала может являться параллельным

мациеи, хранящейся в первом регистре 5. Если информация разная, то операция предварительного сравнения повторяется.

40

Допускается трехкратное повторение операции предварительного сравнения. Если в третьей операции предварительного сравнения будет несравнение ин- кодом, в котором осуществляется синх- д формации, то устройство вырабатывает ронное переключение разрядов. В этом сигнал готовности на выход 21 сигнал случае имеет мес то переходной про- ощибки, который считьгоается через десс, который вызван разбросом време- первьй информационньй выход 19, при

ни переключения отдельных разрядов.

В период переходного процесса ин- .формация будет неустоявшейся и для устройства обработки будет лишней, Чтобы отфильтровать эту лишнюю информацию, в устройстве осуществляется операция предварительного сравнения текущей информации,

В каждой операции предварительног сравнения производится сравнение входной информации, записанной во

мациеи, хранящейся в первом регистре 5. Если информация разная, то операция предварительного сравнения повторяется.

этом на выходе 20 присутствует адрес входного канала, в котором возникла ситуация трехкратного несравнения, а на выходе 19 - информация с входного кайала, соответствующая предьщущей. нтервал задержки в операции предварительного сравнения выбирается больше длительности переходного процесса (лер.прои, ) при этом во входной информации минимальное время между переходными процессами (время устоявщейся

информации - t,cT viHO)) должно быть больше 2t :1ад.

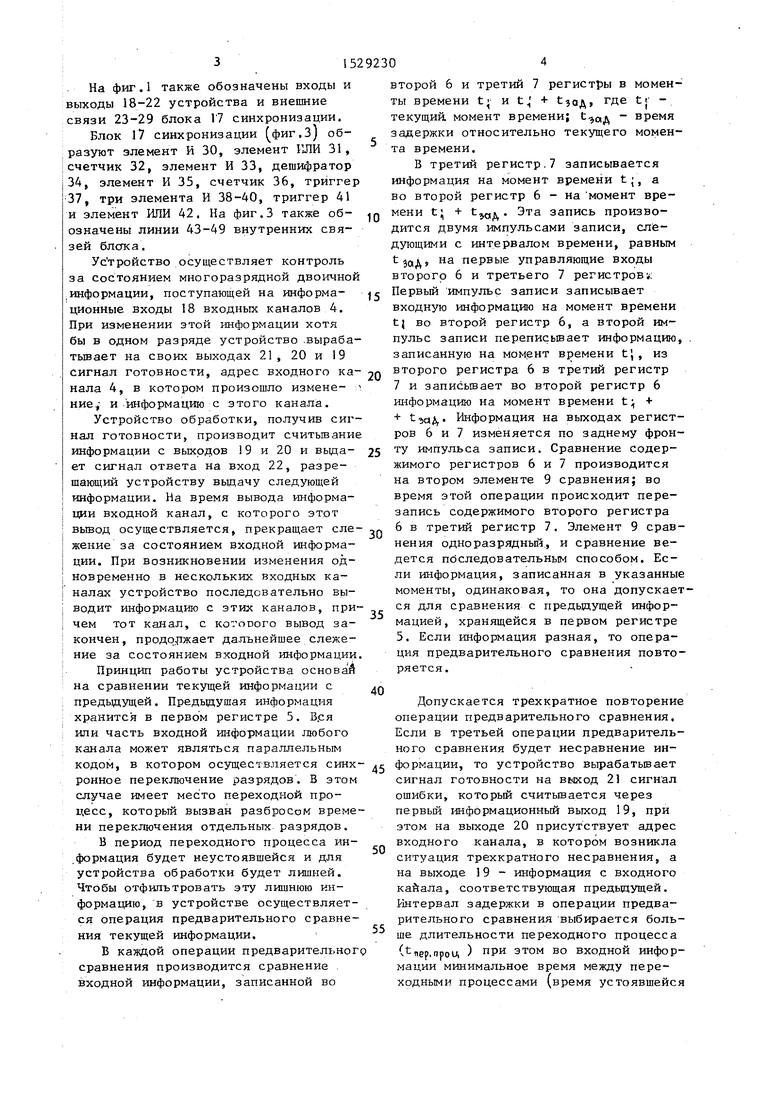

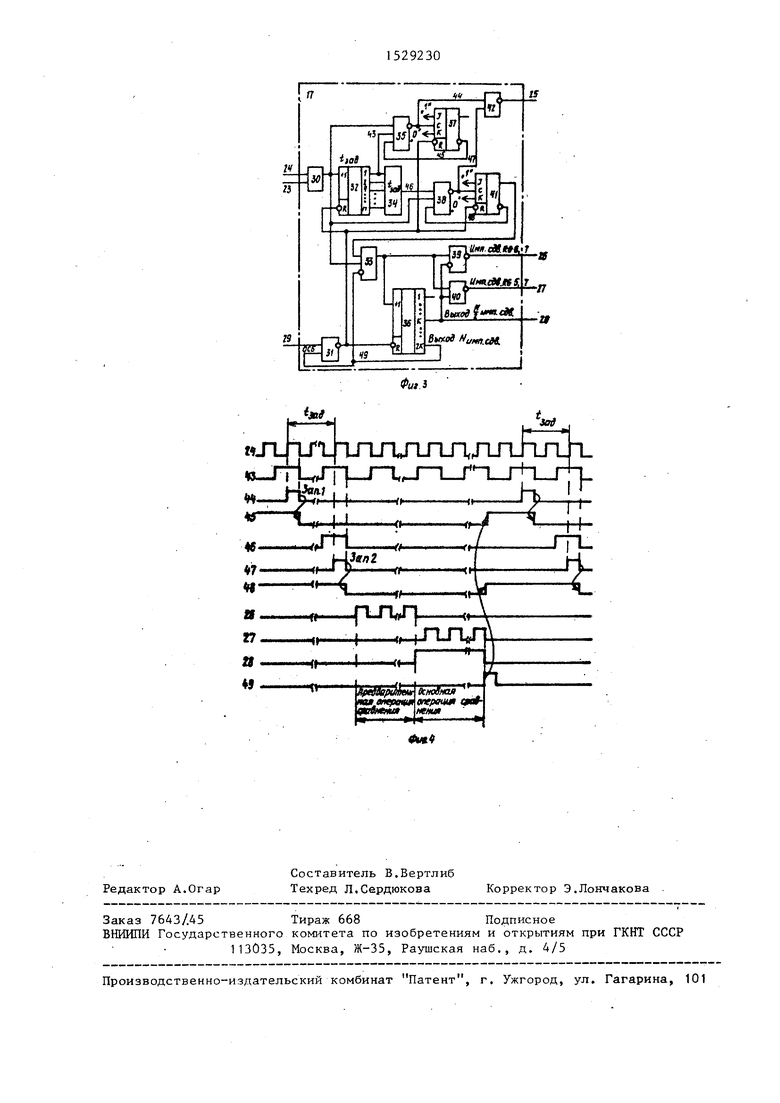

Эти временные соотношения поясняется фиг. 2.

На фиг.2 приняты следующие обозначения: а - моменты записи входной информации; б - распределение переходных процессов во входной информации; I, II, III - отрезки времени, в которые забирается информация для проведения предварительной операции сравнения.

В отрезках I и II времени присутствует переходной процесс, а в отрезке III переходный процесс отсутствует.

Критерии ф ильтрации выражены следующими неравенствами: t,c,A пер.проц

tucr. ии-ср -ЗоД

Сравнение отфильтрованной текущей

информации с предыдущей - основная операция сравнения. В основной операции сравнения осуществляется сравнение содержимого первого 5 и третьего 7 регистров. Сравнение ведется на первом элементе 8 сравнения, который является одноразрядным,

Во время этой операции происходит перезапись содержимого третьего регистра 7 в первый регистр 5.

Первьм.З, второй 6 и третий 7 регистры являются сдвиговыми и имеют одинаковую разрядность, которая соответствует максимальной разрядности информации, обрабатьгоаемой входным каналом. Входы сброса триггера 1 1 и счетчика 16 являются динамическими, работающими по заднему фронту сигнала. Распределитель 2 осуществляет вывод информации из входных каналов на первьй информационньй выход 19, а также синхронизацию обмена информа- . цией с устройством обработки.

Блок 17 вырабатывает на свои выходы сигналы, которые управляют проведением предварительной и основной операций сравнения.

На выход 25 блок 17 вырабатывает импульсы записи, а на выход 26 - импульсы сдвига для проведения предварительной операции сравнения. Количество импульсов сдвига соответствует разрядности регистров 6 и 7. Па выход 27 блок J7 вырабатывает импульсы сдвига ДЛЯ проведения основной операции сравнения, количество которых соответствует разрядности регистров 5 и 7. Эти импульсы поступают на

0

5

0

5

0

5

0

5

0

5

вход первого регистра 5 и через первый элемент ИЛИ 13 на вход третьего регистра 7. На выход 28 блок 17 вырабатывает сигнал, который является признаком проведения основной операции -сравнения, его длительность соответствует времени проведения этой операции.

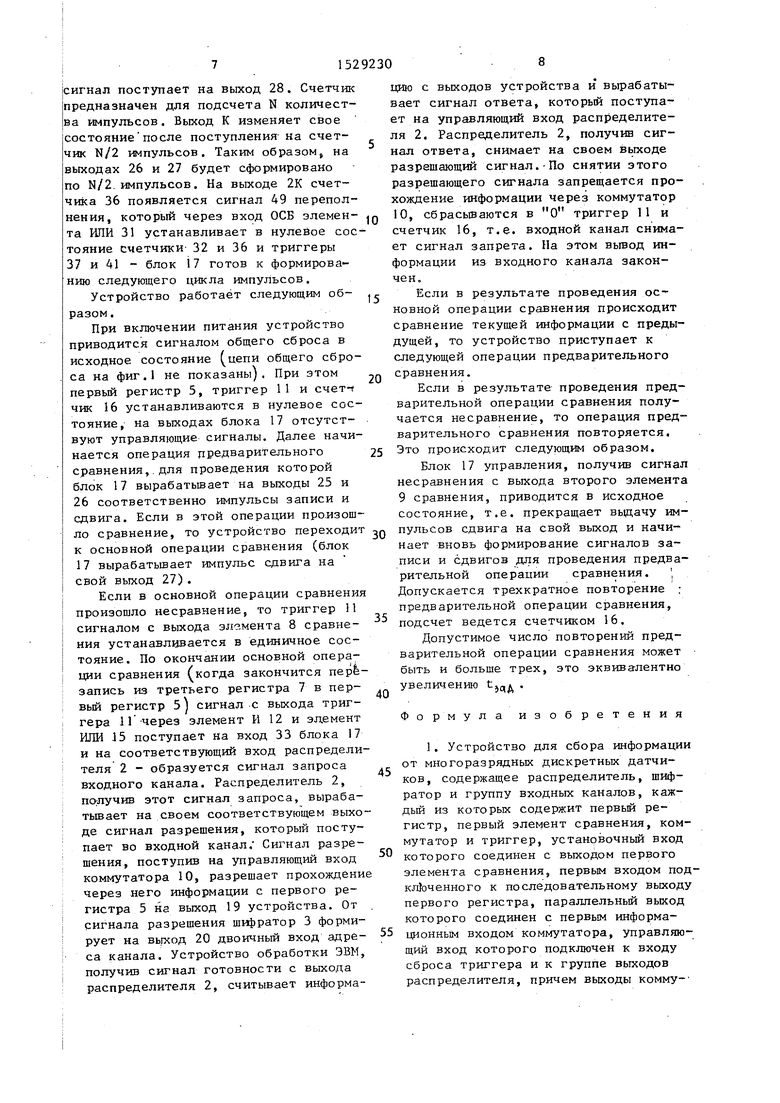

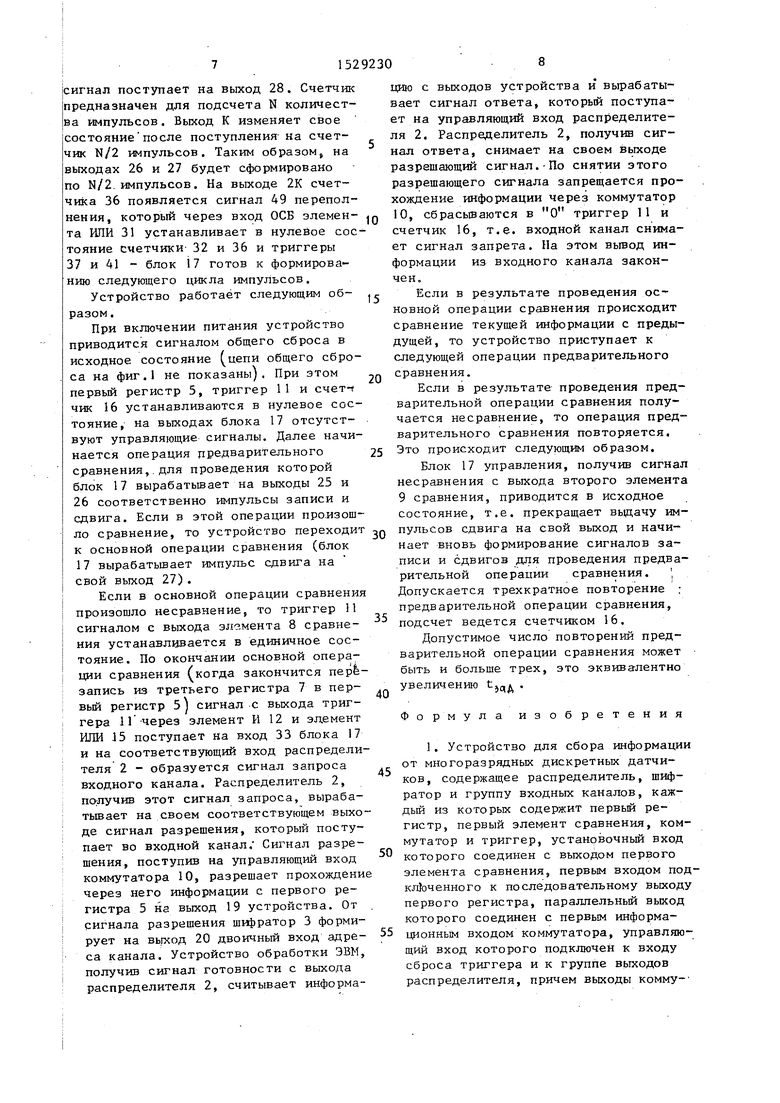

Работу блока 17 опишем по цикло- грамме, изображенной на фиг.4. На циклограмме показаны сформированные блоком 17 сигналы для следующих друг за другом предварительной и основной операций сравнения.

В исходном состоянии счетчики 32 и 36 и.триггеры 37 и 41 установлены в О. Па входе 23 присутствует сигнал, разрешающий прохождение импульсов через элемент И 30.

Па выходе 25 формируются парные импульсы записи - первый и второй. Первый импульс записи формируется на выходе элемента И 35 после установки младшего разряда счетчика 32 в еди ничное состояние. На выход элемента И 35 проходит один импульс из последовательности прямоугольных импульсов. Этот импульс является первым импульсом записи. По заднему фронту этого импульса триггер 37 устанавливается в единичное состояние и запрещает прохождение импульсов через элемент И 35. Второй импульс записи формируется аналогично на элементе И 38 с задержкой () относительно первого. Время задержки -определяется счетчиком 32 и дешифратором 34. При наличии на выходах счетчика 32 кода, определяющего время задержки, на выходе дешифратора 34 появляется сигнал 46 (фиг.4), разрешающий прохождение импульса через элемент И 38. На выход элемента И 38 проходит также . один импульс. По его заднему фронту триггер 4.1 устанавливается в единичное состояние и запрещает дальнейшее прохождение импульсов через элемент И 38. Импульсы, сформированные на элементах И 35 и 38, через элемент ИЛИ 42 поступают на выход 25. После установки триггера 41 в единичное состояние на выходе элемента И 33 появляются импульсы, которые поступают на первые входы элементов И 39 и 40. Вначале импульсы проходят на выход 26, а затем на выход 27. Переключение их с 26 выхода осуществляется сигналом с выхода К счетчика 36. Этот.же

|сигнал поступает на выход 28. Счетчик предназначен для подсчета N количест- |ва импульсов. Вькод К изменяет свое состояние после поступления на счетчик N/2 импульсов. Таким образом, на выходах 26 и 27 будет сформировано по N/2, импульсов. На выходе 2К счетчика 36 появляется сигнал 49 переполнения, который через вход ОСБ элемента ИЛИ 31 устанавливает в нулевое сос тояние счетчики 32 и 36 и триггеры 37 и 41 - блок 17 готов к формированию следующего цикла импуЛьсов.

Устройство работает следующим образом.

При включении питания устройство приводится сигналом общего сброса в исходное состояние (цепи общего сброса на фиг.I не показаны). При этом первый регистр 5, триггер 11 и счет-г чик 16 устанавливаются в нулевое состояние, на выходах блока 17 отсутствуют управляющие сигналы. Далее начинается операция предварительного сравнения,. для проведения которой блок 17 вырабатьшает на выходы 25 и 26 соответственно импульсы записи и сдвига. Если в этой операции про.изош- ло сравнение, то устройство переходит к основной операции сравнения (блок 17 вырабатывает импульс сдвига на свой выход 27).

Если в основной операции сравнения произошло несравнение, то триггер 11 сигналом с выхода элемента 8 сравнения устанавливается в единичное состояние. По окончании основной операции сравнения когда закончится перезапись из третьего регистра 7 в первый регистр З сигнал с выхода триггера 11 -через элемент И 12 и эл.емент ИЛИ 15 поступает на вход 33 блока 17 и на соответствующий вход распределителя 2 - образуется сигнал запроса входного канала. Распределитель 2, по:лучив этот сигнал запроса, выраба- тьгоает на своем соответствующем выходе сигнал разрешения, который поступает во входной канал. Сигнал разрешения, поступив на управляющий вход коммутатора 10, разрешает прохождени через него информации с первого регистра 5 на выход 19 устройства. От сигнала разрешения ши|)ратор 3 формирует на вьгкод 20 двоичный вход адреса канала. Устройство обработки ЭВМ, получив сигнал готовности с выхода распределителя 2, считывает информа

5

0

5

0

5

0

5

0

55

дню с выходов устройства и вырабатывает сигнал ответа, который поступает на управляющий вход распределителя 2. Распределитель 2, получив сигнал ответа, снимает на своем вьгходе разрешающий сигнал.-По снятии этого разрешающего сигнала запрещается прохождение информации через коммутатор 10, сбрасываются в О триггер Пи счетчик 16, т.е. входной канал снимает сигнал запрета. Па этом вывод информации из входного канала закончен.

Если в результате проведения основной операции сравнения происходит сравнение текущей информации с предыдущей, то устройство приступает к следующей операции предварительного сравнения.

Если в результате проведения предварительной операции сравнения получается несравнение, то операция предварительного сравнения повторяется. Это происходит следующим образом.

Блок 17 управления, получив сигнал несравнения с выхода второго элемента 9 сравнения, приводится в исходное состояние, т.е. прекращает вьиачу импульсов сдвига на свой выход и начинает вновь формирование сигналов записи и сдвигов для проведения предварительной операции сравнения. Допускается трехкратное повторение ; предварительной операции сравнения, подсчет ведется счетчиком 16.

Допустимое число повторений предварительной операции сравнения может быть и больше трех, это эквивалентно увеличению д .

Ф о р м ула изобретения

таторов входных каналов группы обра- зуют выход устройства для подключения к информационному входу ЭВМ, выход шифратора является вьгходом устройства для подключения к адресному входу ЭВМ, группа входов шифратора соединена с выходов распределителя, синхровход и выход которого являются соответственно входом и вы ходом устройства для подключения к синхронизирующему выходу и входу готовности ЭВМ, отличающее- с я тем, что, с целью повьпяения быстродействия устройства, в него введен генератор импульсов, а в каж- дьй входной канал - два регистра,второй элемент сравнения, элемент И, три. элемента ШИ, счетчик и блок синх рониза ции, причем в каждом входном канале информационный вход второго регистра является входом устройства для подключения к выходу многоразрядного дискретного датчика, а выходы параллельного и последовательного ко- дов соответственно соединены с информационными входами параллельного и последовательного кодов третьего регистра, выход последовательного кода которого подключен к информационному входу последовательного кода первого регистра, второму информационному входу первого элемента сравнения и первому информационному входу второго элемента сравнения, вторым информационным входом подключенного к выходу последовательного кода второго регистра, синхронизирующий вход первого регистра, соединен с синхронизирующим входом первого элемента сравнения, первыми входами первого и второго элементов ИЛИ и первым выходом блока синхронизации, вторым выходом подключенного к первому входу элемента И, второй вход и выход которого соединены соответственно с выходом триггера и первым входом третьего элемента ИЛИ, вторым входом соединенного с вторым информационным входом коммутатора и выходом счетчика, вход сброса которого подключен к выходу второго элемента ИЛИ, а счетный вход - к входу останова блока синхронизации и выходу второго элемента сравнения, синхровходом соединенного с вторым входом первого элемента ИГШ, входом сдвига второго регистра и третьим выходом блока синхронизации, четвертьй выход которого соединен с входами

записи второго и третьего регистров, а тактовый вход - с вых одом генератора импульсов, выходы первого и тре- тьего элементов ИЛИ соединены соответственно с входом сдвига третьего реги стра и входом пуска блока синхронизации, группа выходов и группа входов распределителя подключены соответственно к вторым входам вторых элементов, ИЛИ и выходам третьих элементов ИЛИ входных каналов группы.

5

0

5 5

0

5

0

5

0

о т

л и чающеес я тем, что блок синхронизации содержит два счетчика, шесть элементов И, два элемента ИЛИ, два триггера и-дешифратор, причем первьй и второй входы первого элемента И являются соответственно тактовым и пусковым входами блока, а выход соединен с первыми входами второго - четвертого элементов И и счетным входом первого счетчика, входы сброса первого и второго счетчиков и первого и второго триггеров подключены к инверсному выходу первого элемента : Ш1Р1, первый и второй входы которого подключены соответственно к входу останова блока и выходу старшего разряда второго счетчика, счетные входы первого и второго триггеров соединены соответственно с инверсными выходами третьего и четвертого элементов И и первым и вторым входами второго элемента ИЛИ, инверсный выход которого является четвертым выходом блока, группа выходов первого счетчика подключена через дешифратор к второму входу четвертого элемента И, третьим входом соединенного с инверсным выходом второго триггера, прямой выход которого подключен к второму входу второго элемента И, выходом соединенного со счетным входом второго счеТ- чика, прямому входу пятого и первому входу шестого элементов И, инверсные выходы которых являются соответственно третьим и первым выходами блока, выход соответствующего разряда второго счетчика соединен с инверсным входом пятого и вторым входом шестого элементов И и является вторым выходом блока, выход старшего разряда второго счетчика соединен с инверсным входом второго элемента И, второй и третий входы третьего элемента И соединены , соответственно с выходом первого разряда первого счетчика и инверсным выходом первого триггера.

У пр. 6к.

х

21

Фи§.1.

.

W 21

j ijrrmjiJijaAJu

-«.

Г у

umotMS

w

Выход .

В Ииня.сМ.

гг.

fLJV}

| Устройство для сбора информации от дискретных датчиков | 1983 |

|

SU1109731A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| УСТРОЙСТВО для СБОРА ИНФОРМАЦИИ от ДИСКРЕТНЫХ ДАТЧИков | 0 |

|

SU377759A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-12-15—Публикация

1986-07-14—Подача