«1

Изобретение относится к вычислительной технике и автоматике и может быть дюпользовано дпя управления технологическими процессами, алгоритмы которых описьшаются логическими функциями, а также для моделирования цифровых устройств с целью их проверки и диагностики.

Цель изобретения - повышение быстродействия вычисления логических функ ций.

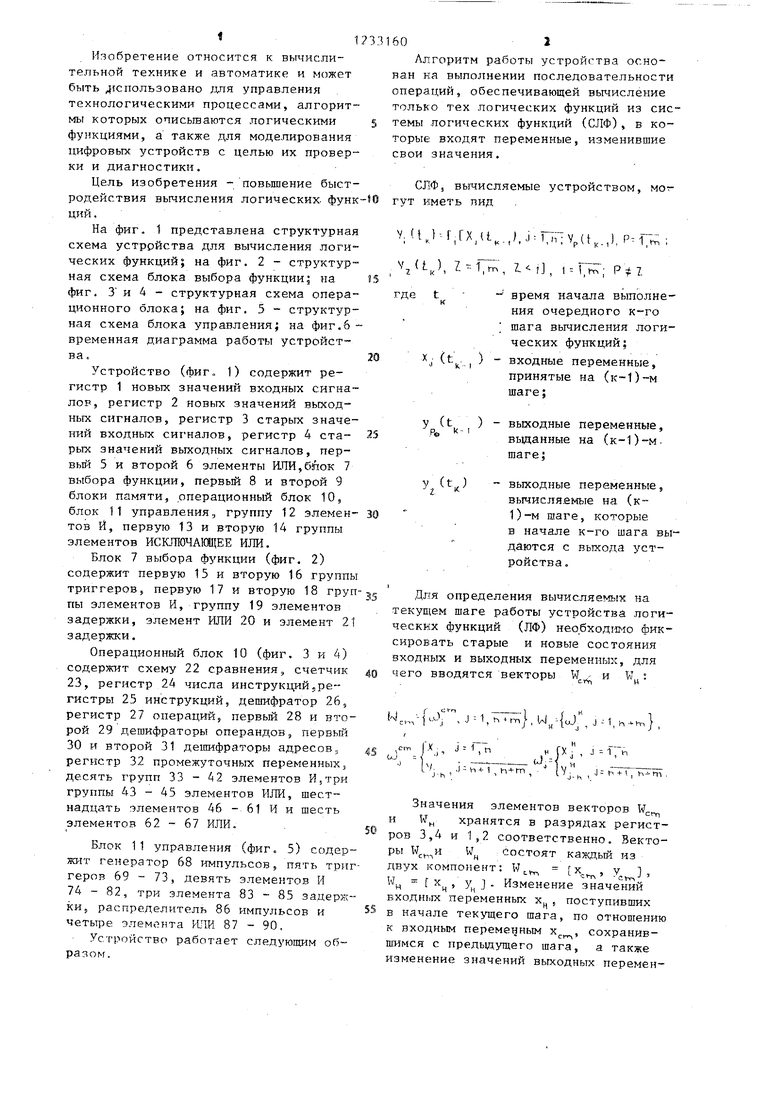

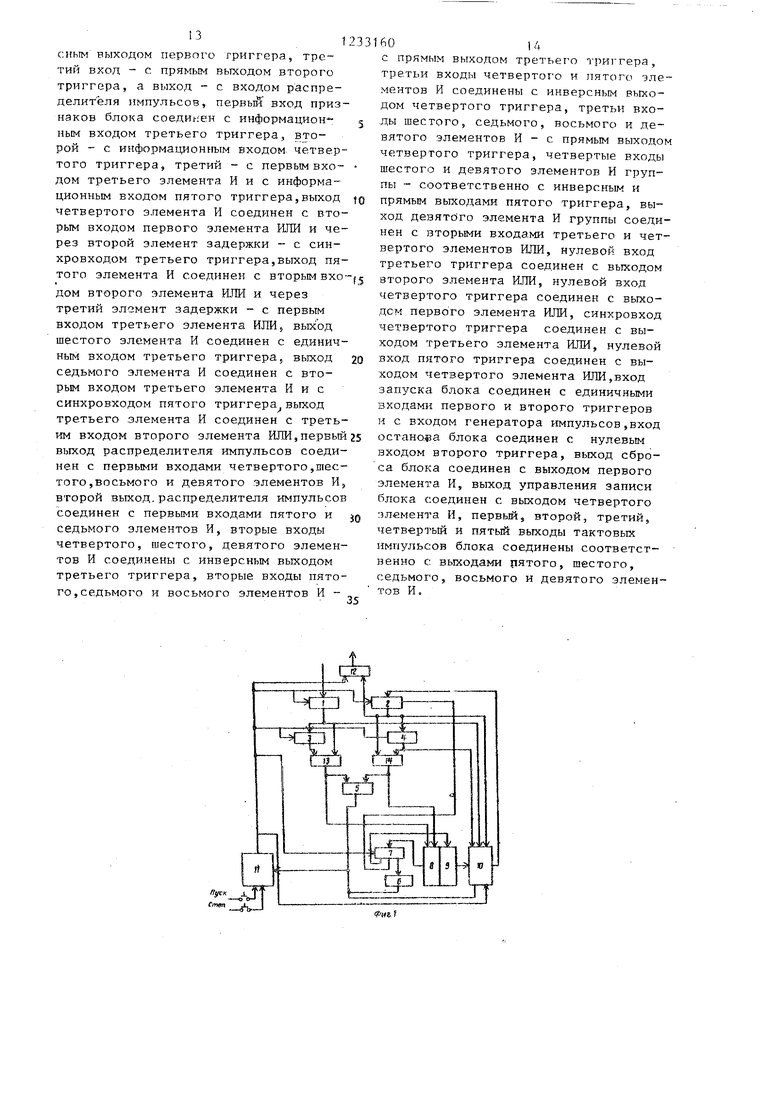

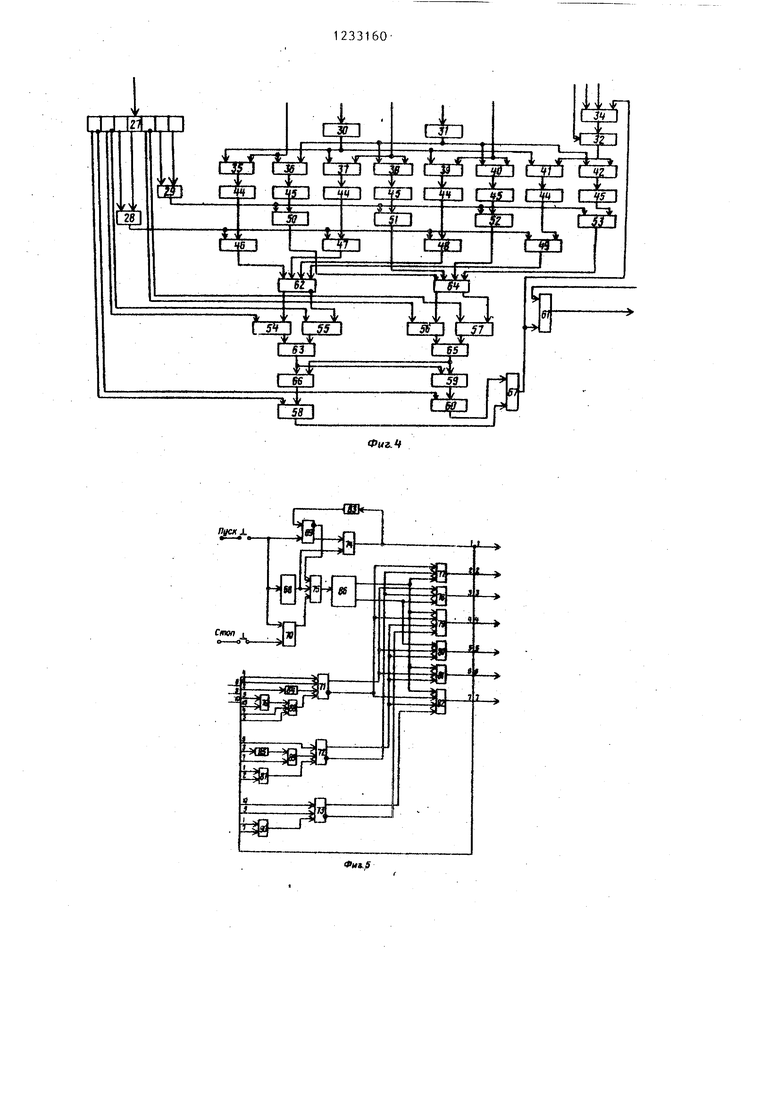

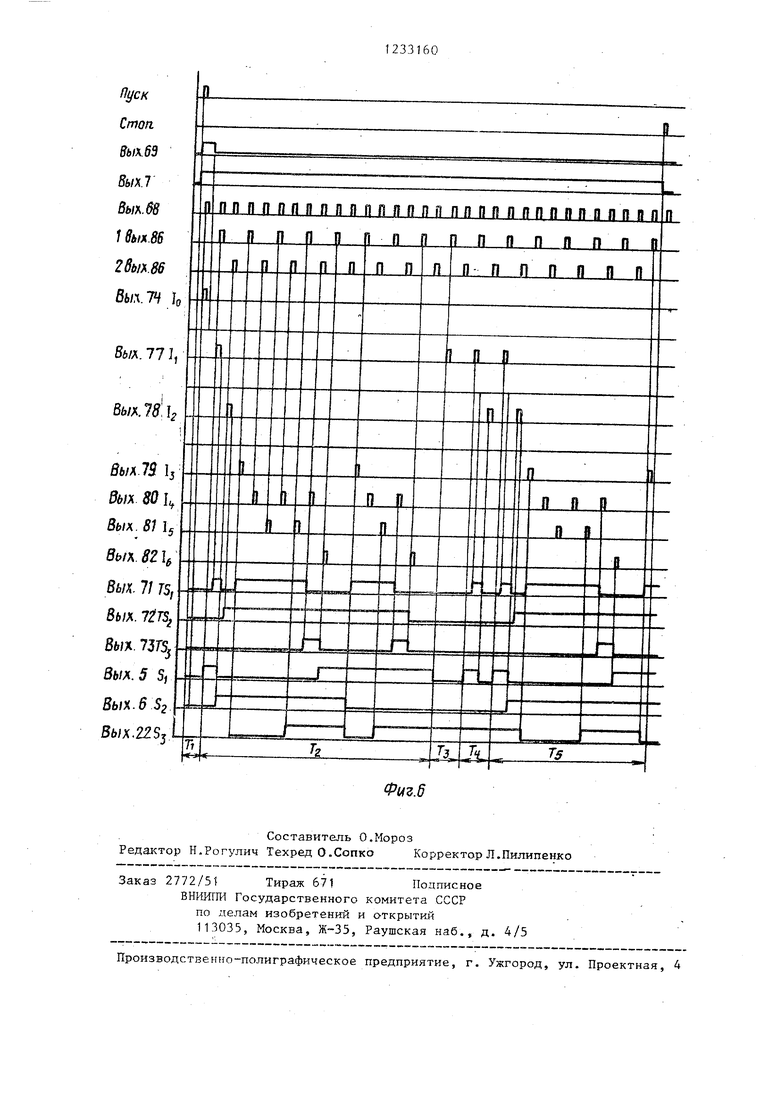

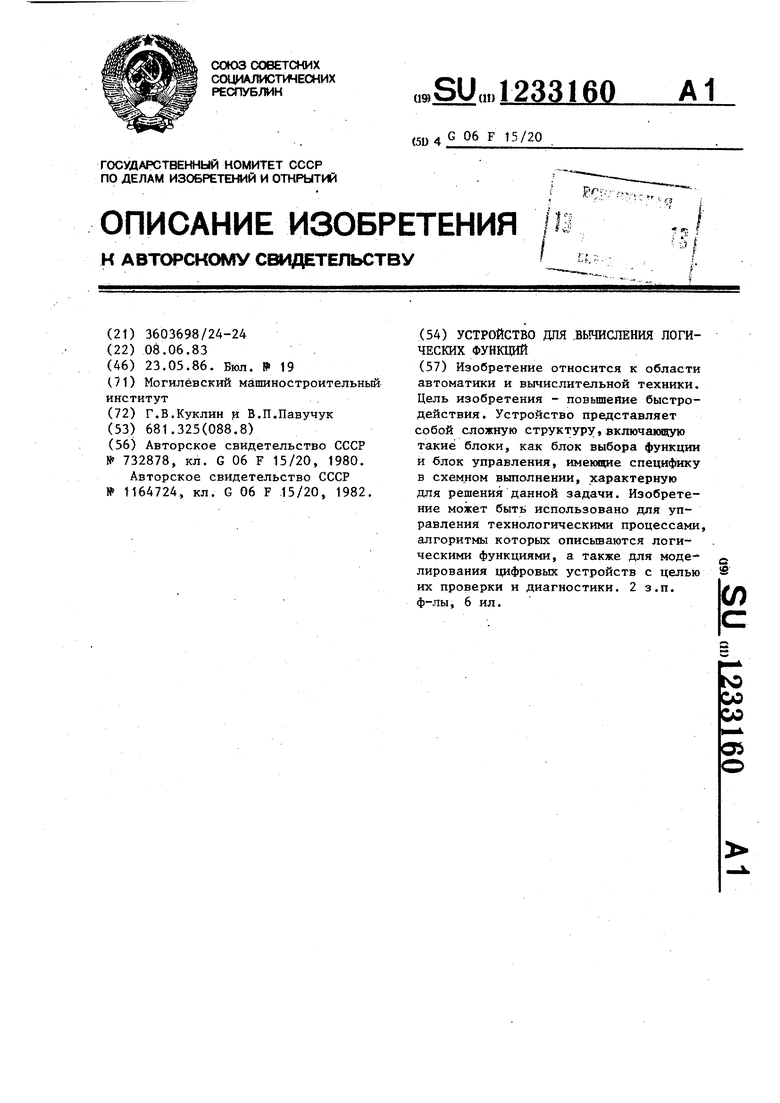

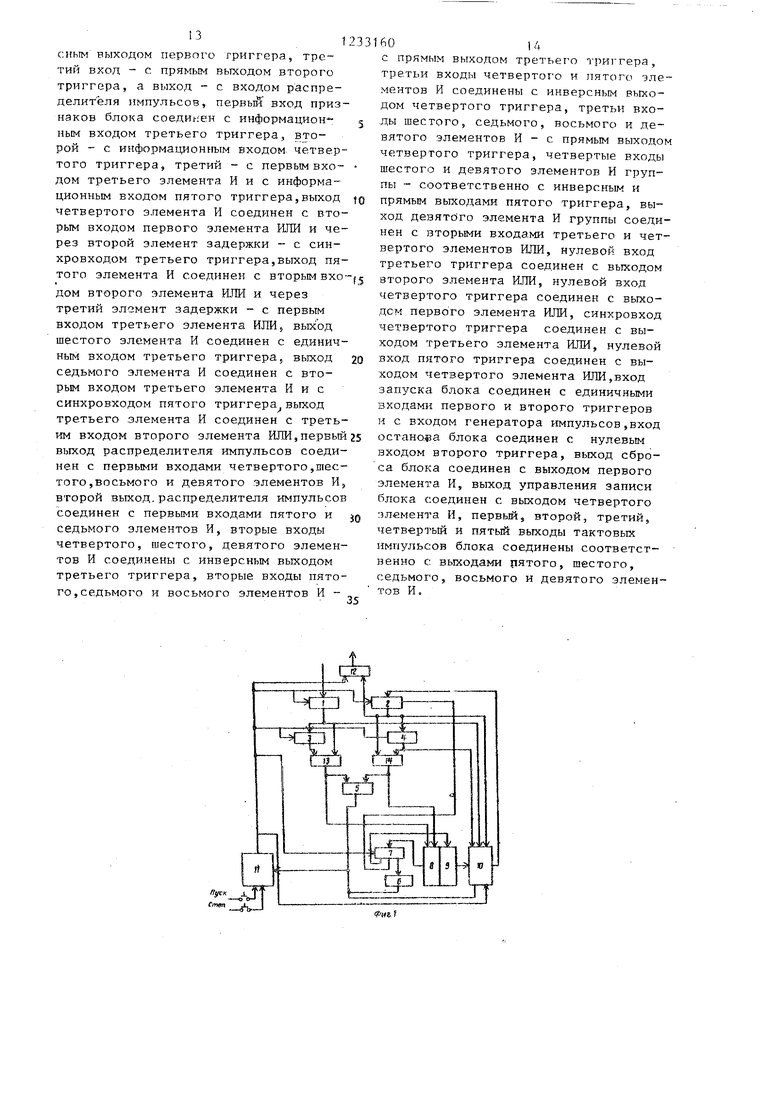

На фиг, 1 представлена структурная схема устррйства для вычисления логических функций; на фиг, 2 - структурная схема блока выбора функции; на фиг. 3 и 4 - структурная схема операционного блока; на фиг, 5 - структурная схема блока управления; на фиг.6 временная диаграмма работы устройства.

Устройство (фиг, 1) содержит регистр 1 новых значений входных сигналов, регистр 2 новых значений выходных сигналов, регистр 3 старых значений входных сигналов, регистр 4 ста- рьгх значений выходных сигналов, первый 5 и второй 6 элементы КПИ,бйок 7 выбора функции, первьй 8 и второй 9 блоки памяти, операционный блок 10, блок 11 управления, группу 12 элемен тов И, первую 13 и вторую 14 группы элементов ИСКЛЮЧАШЩЕ ИЛИ,

Блок 7 выбора функции (фиг, 2) содержит первую 15 и вторую 16 группы триггеров, первую 17 и вторую 18 груп

пы элементов И, группу 19 элементов задержки, элемент ИЛИ 20 и элемент 2 задержки.

Операционный блок 10 (фиг, 3 и 4) содержит схему 22 сравнения,, счетчик 23, регистр 24 числа инструкций,регистры 25 инструкций, дешифратор 26, регистр 27 операций, первьй 28 и вто рой 29 дешифраторы операндов, первьй 30 и второй 31 дешифраторы адресов, регистр 32 промежуточных переменных, десять групп 33-42 элементов И,три группы 43-45 элементов ИЛИ, шестнадцать элементов 46 - 61 И и шесть элементов 62 - 67 ИЛИ.

Блок 11 управления (фиг. 5) содержит генератор 68 импульсов, пять тригеров 69 - 73, девять элементов И 74 - 82, три элемента 83 - 85 задержки, распределитель 86 импульсов и четыре элемоита ИЛИ 87 - 90.

Устройство работает следующим об- pasoNf.

602

Алгоритм работы устройства основан ка выполнении последовательности операций, обеспечивающей вычисление только тех логических функций из системы логических функций (СЛФ), в которые входят переменные, изменившие свои значения,

СЛФ5 вычисляемые устройством, могут иметь ЛИД

V. (t,bf,rxH4,/,jn

, i;Vp(t,.,),P4,;

,(i-J, ZM,m , К,, . Рфг

де

к

t

к

- время начала вьшолне- ния очередного к-го

; шага вычисления логических функций;

-ц -1 входные переменные, принятые на (к-1)м шаге;

у (t ) - выходные переменные, выданные на (к-1)-м. шаге:

выходные переменные, вычисляемые на (к- 1)-м шаге, которые в начале к-го шага выдаются с выхода устройства.

W

Для определения вычисляемьгх на текущем шаге работы устройства логических функций (ЛФ) необходимо фиксировать старые и новые состояния входных и выходных переменных, для чего вводятся векторы W и VJ, :

J 1, h т) , W -{о/ J П, .V h } ,

W

Значения элементов векторов W и W хранятся в разрядах регистров 3,4 и 1,2 соответственно. Векторы W состоят каждьй из двух компонент: W, х , у ., ц f х , у J . Изменение значе ний входньгх переменных х, ,, поступивших в начале текущего шага, по отношению к входным переменным х , сохранившимся с предьщущего шага, а также изменение значений выходных переменных у , сформированных в конце предшествующего шага и переданных на текущий щаг, по отношению к входным переменным у , хранящимся с предшествующего шага (с момента передачи у : на предшествующем шаге), опреотличные от нуля значения

УН деля ют

элементов компонент х и у вектора , j 1,n+m}.Переменные, изменившие свои значения по отношению к предшествующим значениям, фиксируются единицами на соответствующих выходах первой группы 13 и второй группы 1А элементов ИСКЛЮЧАЩЕЕ ИЛИ и определяются по следукдцему правилу

cj.oj ©uj

J J J

j : 1 , h-t- h-1

Вьтолнение операции суммирования по модулю два осуществляется в устройстве с использованием двух групп элементов ИСКЛЮЧАЩЕЕ ИЛИ. Для определения номеров функций СЛФ, вычисляемых на текущем шаге, формируется матрица вхождений М размерности nx(n+m).Элемент матрицы равен 1 если в логическую функцию для вьиис ления у входит переменная х ,j

4.«J

1,п или переменная у , j п+1 п+т В противном случае m . 0. Со тавленная таким образом матрица входений М хранится в первом блоке 8 памяти. Решаемые на текущем шаге ЛФ определяются отличными от нуля элементами вектора решаемых ЛФ

, .TT;;;} .

Вектор W определяется в результате выполнения операции

W-MxUI,

которая в предлагаемом устройстве реализована применением памяти ассоциативного типа, когда в блоке 8 за фиксированы ассоциативные признаки, соответствующие элементам матрицы вхождений М, и подача на вход блока 8 сигналов с выхода первой группы 13 и второй группы 14 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ позволяет на его выходе получить значения элементов век- тора W , которые фиксируются в бло- ке 7 выбора функции. В соответствии с определенными по приведенному правилу элементами вектора Wp осуществлется последовательное вьгчисление ЛФ по определению значений у , если

р , „

uOj f 0. При этом адрес вычисляемой

ЛФ однозначно определяется номером

0

5

0

разряда блока 7, дпя которого.j 0, В соответствии с таким адресом вьмис- ляемая функция из блока 9 памяти передается в операционный блок 10.После того, как вычислены ЛФ, для которых uJ f О, текущий шаг работы ройства завершается окончанием формирования нового слова выходной информации у и устройство переходит на прием очередного нового слова входной информации х , а с выхода устройства вьздается сформированное слово-.выходной информации. Последовательность обработки информации по шагам с момента пуска устройства при W О и наличии вычисляемых функций (случаи 1/Wj, 0; О, вычисляемые функции отсутствуют - S О, и не представляют интереса,так как устройство вновь обращается за входной ин- фЬрмацией и подтверждает выходные сигналы до тех пор,пока не появляются изменения входной информации) можно представить таким образом: Нулевой шаг х° , х° . у

У/.

X V

- «5„ кЬЯ

0;

шаг

1) 2)

в«

Х

X

т

У,

УС.

3) при ,

X

Чх

У У

- н

4) при Si 1, вычисляем СЛФ и формируем

У. ;

1)

(ЬХ

УН

вых

2)

М7,М

/74 XH (± X,

иу.н

у

с.Т

1,

ст

п

УН

с т

вычислявх1,

и формируем

. (Ч

X

в«

вых

2) х;;„ x:®x:v ,

yj;. -У:®У.:

3), при S, 1 ,

X.

УС,

, У«

j

4) .при S 1 , вычисляем СЛФ и формируем У , . и т.д.

Для третьего шага , х , ,

Н из« MjM

yj имеют следующий смысл:

х - входное слово, полученное в начале текущего (третьего) шага из внешней среды (х ); х - отв из

ражает изменение полученного значения х по отношению к значению х , сохранившемуся с предьщущего шага: у - отражает изменение сформиро- ванного в конце предьщущего шага

значения у

по отношению к значению

у , сохранившемуся с предыдущего шага; - выходное слово, сформированное в конце текущего шага, которое в начале следующего шага вьщает- ся во внешнюю среду, как реакция на входное воздействие, поступившее в начале текущего щага.

По сигналу Пуск запускается блок 11 управления и начинает выраба тьюать управляющие сигналы 1 (фиг. 6). Импульсом „ устанавливаются в исходное нулевое состояние триггеры первой 15 и второй 16 групп блока выбора функции (фиг. 2), триггеры 71 - 73 в блоке 11 управления (фиг. 5), регистр 1 новых значений входных сигналов, регистр 2 новых значений выходных сигналов, регистр 3 старых значений входных сигналов и регистр 4 старых значений выходных сигналов (фиг. 1). В начале каждого нового шага в регистре 2 новых значений выходных сигналов записаны значения в.1ходных сигналов, соответ- ствуюшл е oKoH TaiiHio предшествующего

шага, а в регистре 3 старых значений входных сигналов и в регистре 4 старых значений выходных сигналов - на- 5 чалу предшествующего шага.Если первый элемент ИЛИ 5 не зафиксировал измене- н:ий входнкгх и (или) выходных сигналов т.е. S., 0, и если на выходе второго элемента ШШ 6 S 0, то блок 1 1 з прав0 ления выдает управляющие сигналы 1 , до тех пор, пока не зафиксированы изменения входной и (или) выходной информации. По сигналу I производится прием очередного нового слова вход5 ной информации в регистр 1 новых значений входных сигналов и выдача с выхода группы 12 элементов И слова в)1ходной информации, сформированного на предшествующем шаге в регистре 2

0 новых значений выходных сигналов, а также установка через элемент задержки в соответствии с состоянием признака S триггера 71 и сброс в нуле-- вое состояние триггера 72 в блоке 11

5 управления. Наличие либо отсутствие изменений входной и (или) выходной информациипостоянно фиксируется элементом ИЛИ 5, который через первую 13 и вторую 14 группы элементов ИС0 КПРШОЦЕЕ ИЛИ связан с регистрами

1-4 старых и новых значений вход- . ной и выходной информации. Сигналом Ij осуществляется опрос первого блока 8 памяти и занесение результатов

опроса на вторую группу триггеров 16 блока 7 выбора функции, передача содержимого регистров новых значений входных 1 и выходных 2 сигналов - соответственно в регистры старых

д значений входных 3 и выходных 4 сигналов, сброс триггера 71 и через элемент задержки его установка - в соответствии с состоянием признака

S триггера 72. Если S О,т.е.

5 нет вычисляемых ЛФ, то следующим

сигналом на выходе блока 11 управления является сигнал I, , если же S 1, т.е. есть вычисляемые ЛФ, то вырабатывается управляющий сигнал 1 .

0 По сигналу Ij с выходов элементов И

группы 18 блока 7 вьщается сигнал выборки-функции из второго блока 9 памяти, а с выходов триггеров группы 15 блока 7 - разрешение на прием ре- 5 зультата вычисления функции в тот

разряд регистра 2, номер которого соответствует HoMepV вычисляемой функции, устанавливаются в нулевое сое71

тояние счетчик 23 и регистр 32 промежуточных переменных и в единичное состояние триггер 71 блока 11 управления. Сигнал 1 производит передачу инструкции, номер которой соответст- вует числу в счетчике 23, которая выбирается дешифратором 26, на входы регистра 27 операций, первого 30 и второго 31 дешифраторов -адреса. Дешифратор 26 выбирает также разряд в ре- гистре 32 промежуточных переменных, номер которого соответствует номеру выбранной инструкции, для приема промежуточного результата. При сигнале Несравнение, т.е. S О, из блока 11 управления выдается далее сигнал Ij, по которому производится занесение результата выполненной инструкции в подготовленный для приема разряд регистра 32 промежуточных пере- менных и прибавляется единица в младший разряд счетчика 23. В случае появления сигнала Сравнение после прибавления очередной единицы, т.е. S, 1 , очередной сигнал I , помимо указанных действий, производит установку в единичное состояние триггера 73 и сброс в нулевое состояние триггера 71 в блоке 11 управления. Тогда следующим управляющим сигналом явля- ется 1,который производит занесение результата выполненной инструкции в подготовленный для приема разряд регистра 2 новых значений выходных сигналов, сбрасывает в нулевое состояние триггеры группы 15 блока 9 и триггер 73 блока 11, устанавливает в соответствии с признаком S триггер 72 блока 11,т.е. либо подтверждает единичное состояние, в случае если есть еще вычисляемые ЛФ, либо сбрасывает в нулевое состояние в противном случае. Таким образом, до выдачи сигнала со схемы 22 сравнения производится поочередное выполнение всех ин- струкций вычисляемой ЛФ. При выполнении последней инструкции выдается сигнал со схемы 22 сравнения и результат попадает п регистр 2 новых значений выходных сигналов. Затем процесс вычисления СЛФ повторяется для очередной функции до тех пор, пока не вычисляются все функции. Тогда триггеры 71-73 блока 11 оказьгеаются в нулевом состоянии и переводят блок 11 управления на выдачу сигналов для приема очередного входного и выдачу полученного выходного слова. Останов

jюf5 20 25 .j- 0 5055

1608

устройства может производиться в любой момент его работы нажатием кнопки Стоп.

Формула изобретения

1. Устройство для вычисления логических функций, содержащее регистр новых значений входных сигналов, регистр новых значений выходных сигналов, регистр старых значений входных сигналов, регистр старых значени выходных сигналов, первый и второй элементы ИЛИ, блок выбора функции, два блока памяти, операционный блок, блок управления, отличающее- с я тем, что, с целью повьшения быстродействия, в него введены группа элементов И, две группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, причем выходы элементов И группы соединены с выходами результата устройства, информационный вход регистра новых значений входных сигналов соединен с информационным входом устройства, выход регистра старых значений входных сигналов соединен с первыми вхсдамц элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы выходы которых соединены с первой группой входов первого элемента ИЛИ и первой группой информационных входов первог о блока памяти, выход регистра новых значений входных сигналов соединен с вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы и с входом регистра старых значений входных сигналов, выход регистра новых значений выходных сигналов соединен с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы и с входом регистра старых значений выходных сигналов, выход которого соединен с вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ t второй группы, выходы которых соединерш с второй группой входов первого элемента ИЛИ и с второй группой ин- формационных входов первого блока памяти, выход которого соединен с информационным входом блока выбора функции, первый выход которого соединен с входом второго элемента РШИ, второй выход - с управляющим входом записи регистра новых значений выходных сигналов, третий выход - с адресным входом второго блока памяти,вход инструкций операционного блока соединен с выходом второго блока памяти, первый, второй, и третий информацион

9

иые входы операционного блока соединены соответственно с выходами ре-- гистров старых значений выходных сигналов, новых значений входных сигналов и новых значений выходных сигна лов, выход результата операционного блока соединен с информационным входом регистра новых значений выходных сигналов, вторые входы элементов И группы соединены с выходом регистра новых значений выходных сигналов, выход сброса блока управления соединен с входом сброса блока выбора функции и входами сброса регистров старых и новых значений входных и выходных сигналов, выход управления записи блока управления соединен с первыми входами элементов И группы и синхровходом регистра новых значений входных сигналов, первый выход тактовых импульсов блока управления соединен с синхровходами регистров старых; значений входных и выходных сигналов и первым синхровходом блока выбора функции, второй выход тактовы импульсов блока управления соединен с вторым синхровходом блока выбора функции и первым синхровходом операционного блока, третий выход тактовых импульсов блока управления соеди нен с вторым синхровходом операционного блока, четвертый выход тактовых импульсов блока управления соединен с третьим синхровходом операционного блока, пятый вь1ход тактовых импульсов блока управления соединен с трет им синхровходом блока выбора функции и четвертым синхровходом операционного блока, входы запуска и останова блока управления соединены соответственно с входами запуска и останова устройства, первьй, второй и третий входы признаков блока управления соединены соответственно с выходами первого и второго элементов ИЛИ и с выходом признака окончания работы операционного блока, причем операционный блок содержит схему сравнения, счетчик, регистр числа инструкций, регистры инструкций, дешифратор регистр операций, два дешифратора операндов, два дешифратора адресов, регистр промежуточных переменных, десять групп элементов И, три группы элементов ИЛИ, шестнадцать элементов ,И и шесть элементов ИЛИ, причем первый вход схемы сравнения соединен с выходом регистра числа инструкций.

10

15

20

33

j 5 g g j

5

0

5

второй - с выходом счетчика, вь хол схемы сравнения соединен с выходом признака окончания работы операционного блока, вход дешифратора соединен с выходом счетчика, вход сброса счетчика соединен с первым синхровходом операционного блока, входы регистра числа инструкций и регистров инструкций соединены с входом инструкций операционного блока, первые входы элементов И первой группы соединены с вторым синхровходом операционного блока, вторые входы элементов И первой группы соединены с выходами регистров инструкций, третьи входы с соответствующими выходами дешифратора, а выходы - с входами соответст - вующих элементов ИЛИ первой, второй и третьей подгрупп первой группы, выходы которых соединены с входами соответственно регистра операций,первого и второго дешифраторов адреса, выходы элементов И второй группы соединены с входа1чи регистра промежуточных переменных, первьй, второй и третий информационные входы операционного блока соединены с первыми входами элементов И соответственно третьей и четвертой, пятой и шестой, седьмой и восьмой групп, первые входы элементов И девятой и десятой групп соединены с выходами регистра проме;куточных переменных, вторые входы элементов И третьей, пятой, седьмой и девятой групп соединены с вы- ходам1Я первого дешифратора адреса, вторые входы элементов И четвертой, тестой, восьмой и десятой групп соединены с выходами второго дешифратора адреса, первые входы первого,второго, третьего и четвертого элементов И соединены с выходами первого дешифратора операндов, первые входы пятого, шестого, седьмого и восьмого элеме нтов И соединены с выходами второго дешифратора операндов, выходы элементов И третьей, пятой, седьмой и девятой групп соединены с входами элементов ИЛИ второй группы,выходы которых соединены с вторыми входами первого, второго, третьего и четвертого элементов И, выходы кото- рьгх соединены с входами первого элемента ИЛИ, прямой и инверсный выходы которого соединены с первыми входами соответственно девятого и десятого элементов И , выходы которых соединены с входами второго элемен

II.

Я ШШ, выходы элементов И четвертой пестой, восьмой и десятой групп соединены с входами элементов ИЛИ треть группы, выходы которых соединены вторыми входами пятого, шестого, | едьмого и восьмого элемеытов И, выходы которых соединены с входами третьего элемента ИЛИ, прямой и инверсный выходы которого соединены с первыми входами соответственно одиннадцатого и двенадцатого элементов И, выходы которых соединены с входами четвертого элемента ИЛИ, первый вход пятого элемента ИЛИ соединен с выходом второго элемента ИЛИ, второй вход - с выходом четвертого элемента ИЛИ, а выход - с первым входом тринадцатого элемента И, выход которого соединен с первым входом шестого элемента ИЛИ, первьй вход четырнадцатого элемента И соединен с выходом второго элемента ИЛИ, второй вход - с выходом четвертого элемента ИЛИ, а выход - с первым входом пятнадцатого элемента И, выход кото- рого соединен с вторым входом шестого элемента ИЛИ, прямой и инверсны выходы первого разряда регистра операций соединены с вторыми входами соответственно тринадцатого и пятнадцатого элементов И, прямой и инверсньш выходы второго разряда регистра операций соединены с .вторыми входами соответственно девятого и десятого эле ментов И, прямые выходы третьего и четвертого разрядов регистра операций соединены с входами первого дешифратора операндов, прямой и инверсный выходы пятого разряда регистра операций соединены с вторыми входами соответственно одиннадцатого и двенадцатого элементов И, прямые выходы шестого и седьмого разрядов соединены с входами второго дешифратора операндов, первые входы элементов И второй группы соединены с третьим син- хровходом операционного блока и счетным входом счетчика, вторые входы - с вьгходами дешифратора, третьи входы - с выходом шестого элемента ИЛИ,

синхровход записи регистра промежуточных переменных соединен с первым синхровходом операционного блока,первый вход шестнадцатого, элемента И соединен с выходом шестого элемента ИЛИ, второй вход - с четвертым син- хровходом операционного блока, а выход - с выходом результата операционного блока.

10

15

20

33

, 25

0

0

0

5

2. Устройство по п. 1 , о т .4 и- чающееся- тем, что блок выбора функции содержит две группы триггеров, две группы элементов И, группу элементов задержки, элемент ИЛИ, элемент задержки, причем выход элемента ИЛИ соединен с нулевыми входами триггеров первой группы, выход i-ro элемента И первой группы соединен с первым входом(L+I)-го элемента И первой группы и первым входом (i + 1)-го элемента И второй группы, i 1, m - 1; m - число вычисляемых функций), первьй вход последнего элемента И второй группы соединен с выходом последнего элемента И первой группы, вторые входы элементов И первой и второй групп соединены соответственно с инверсными и прямыми выходами триггеров второй группы, прямые выходы триггеров второй группы объединены и соединены с первым выходом блока, прямые выходы триггеров первой группы объединены и соединены с вторым выходом блока, выходы элементов И второй группы соединены с единичньми входами соответствующих триггеров первой группы и соединены с третьим выходом блока, а через элементы задержки группы - с первыми нулевыми входами триггеров второй группы, инфор мационные входы триггеров второй группы объединены и соединены с информационным входом блока, вход сброса блока соединен с первым входом элемента ИЛИ и вторыми нулевыми входами триггеров второй группы, первьй синхровход блока соединен с синхровходами триггеров второй группы, второй - с входами первых элементов И первой и второй групп, третий - через элемент задержки с вторым входом элемента ИЛИ.

3. Устройство по п. 1, о т л и- чающееся тем, что блок управления содержит генератор импульсов, пять триггеров, девять элементов И,, три элемента задержки, распределитель импульсов, четьфе элемента ИЛИ, причем выход генератора импульсов соединен с первыми входами первого и второго элементов И,второй вход первого злемента И соединен с прямым выходом первого триггера, а выход - с первыми входами первого, второго и четвертого элементов ИЛИ и через первый элемент задержки - с нулевым входом первого триггера, второй вход второго элемента И соединен с инвер 1

сным выходом первого триггера, третий вход - с. прямым вьтходом второго триггера, а выход - с входом распределителя импульсов, первый вход признаков блока соединен с информацион - иым входом третьего триггера, второй - с информа11 1онпым входом четвертого триггера, третий - с первым вхо- дом третьего элемента И и с информационным входом пятого триггера,выход четвертого элемента И соединен с вторым входом первого элемента РШИ и через второй элемент задер жки - с син- хровходом третьего триггера,выход пятого элемента И соединен с вторым BXO дом второго элемента ИЛИ и через третий элемент задержки - с первым входом третьего элемента ИЛИ, выход шестого элемента И соединен с единичным входом третьего триггера,, выход седьмого элемента И соединен с вторым входом третьего элемента И и с синхровходом пятого триггера выход третьего элемента И соединен с третьим входом второго элемента ИЛИ,первый выход распределителя импульсов соединен с первыми входами четвертого,шестого,восьмого и девятого элементов И второй выход.распределителя импульсов соединен с первыми входами пятого и седьмого элементов И, вторые входы четвертого, шестого, девятого элементов И соединены с инверсным выходом третьего триггера, вторые входы пятого, седьмого и восьмого элементов И -

60i 4

с прямым выходом третьего триггера, третьи входы четвертого и пятого элементов И соединены с инверсным выходом четвертого триггера, третьи входы шестого, седьмого, восьмого и девятого элементов И - с прямым выходо четвертого триггера, четвертые входы шестого и девятого элементов И группы - соответственно с инверсным и прямым выходами пятого триггера, выход девятс1го элемента И группы соединен с вторыми входами третьего и четвертого элементов ИЛИ, нулевой вход третьего триггера соединен с выходом второго элемента ИЛИ, нулевой вход четвертого триггера соединен с выходом первого элемента ИЛИ, синхровход четвертого триггера соединен с выходом третьего элемента ИЛИ, нулевой вход пятого триггера соединен с выходом четвертого элемента ИЛИ,вход запуска блока соединен с единичными )зходами первого и второго триггеров и с входом генератора импульсов,вход остано,а блока соединен с нулевым входом второго триггера, выход сброса блока соединен с выходом первого элемента И, выход управления записи блока соединен с выходом четвертого элемента И, первый, второй, третий, четвертый и пятый выходы тактовых импульсов блока соединены соответственно с выходами пятого, шестого, седьмого, восьмого и девятого элементов И,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления систем логических функций | 1982 |

|

SU1269146A1 |

| Устройство для реализации логических функций | 1981 |

|

SU1164724A1 |

| Устройство для реализации логических функций | 1983 |

|

SU1257658A2 |

| Ячейка однородной вычислительной среды | 1986 |

|

SU1386987A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Логический процессор | 1986 |

|

SU1315995A1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1644145A1 |

| Устройство для управления распределенными объектами | 1985 |

|

SU1290261A1 |

Изобретение относится к области автоматики и вычислительной техники. Цель изобретения - повышение быстродействия. Устройство представляет собой сложную структуру, включакнцую такие блоки, как блок выбора функции и блок управления, имеющие специфику в схемном выполнении, характерную для решения данной задачи. Изобретение может быть использовано для управления технологическими процессами, алгоритмы которых описьшаются логическими функциями, а также для моделирования цифровых устройств с целью их проверки и диагностики. 2 з.п. ф-лы, 6 ил. о S (Л

Фи& f

i..g..:

/ k

(

LM

-3 /

I 24 25 j I 25 I i 25 (

-dLJI

nn Гз5

S

X

Пз1

т

Фиг.З

Фиг. 2

I

Ф N Г

n Гз5

I

у V Ч

X

з1

J US.

I

ши

т

л

Пуск Стоп. Bbi)i63 Яш. 7 Выкб8 16ш.86

гбш.ве

fib/xTV io Вш. 77 J,

ВЫ)(

Ij Вых 801 Вых. 81 Is Вы. 821

Вык. 71 75, Вых. BbJK. 7Щ Вых. 5 S, Яь;х.5 52 6WX.22S7

Составитель О.Мороз Редактор Н.Рогулич Техред О.Сопко Корректор Л.Пилипенко

Заказ 2772/51 Тираж 671 Подписное ВНИИГШ Государственного комитета СССР по 11елам изобретений и о-ткрыткй 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Ф143.6

| Устройство для реализации логических функций | 1977 |

|

SU732878A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для реализации логических функций | 1981 |

|

SU1164724A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-23—Публикация

1983-06-08—Подача