4

оо со ф

Изобретение относится к вычислительной технике и может быть использовано при организации и тестировании программе

Цель изобретения - повышение достоверности работы устройства И сокращение объема информации о ходе вьтолнения программы без снижения ее достоверности.

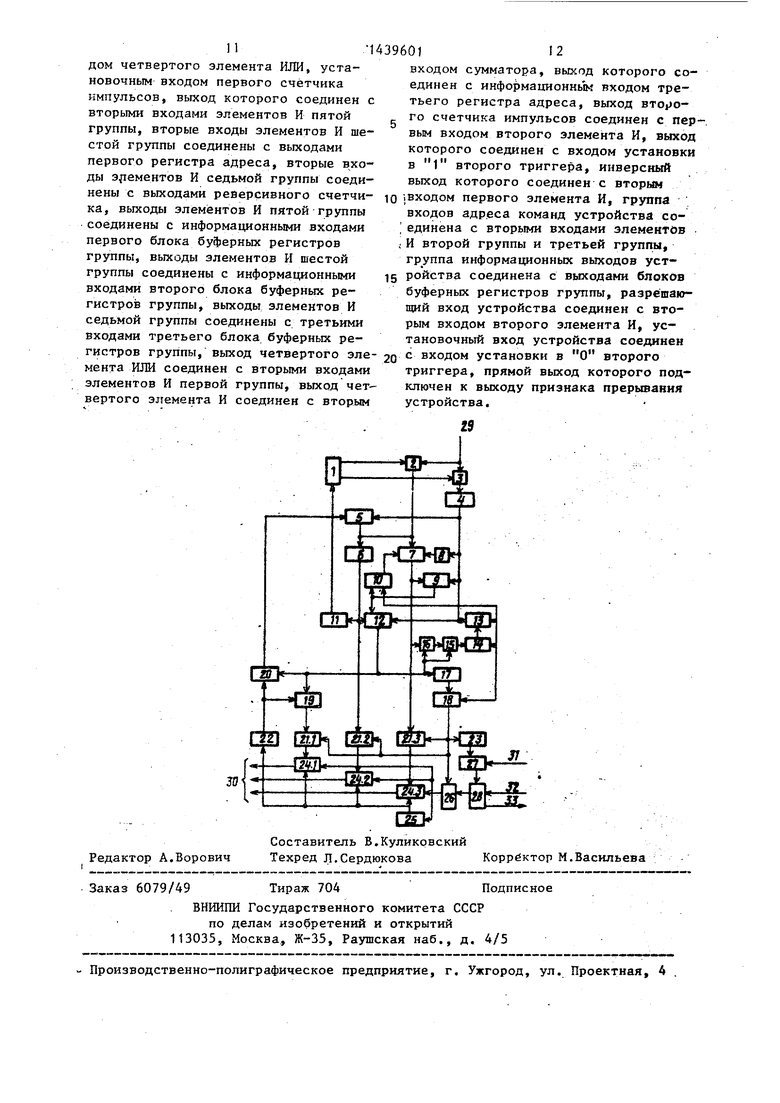

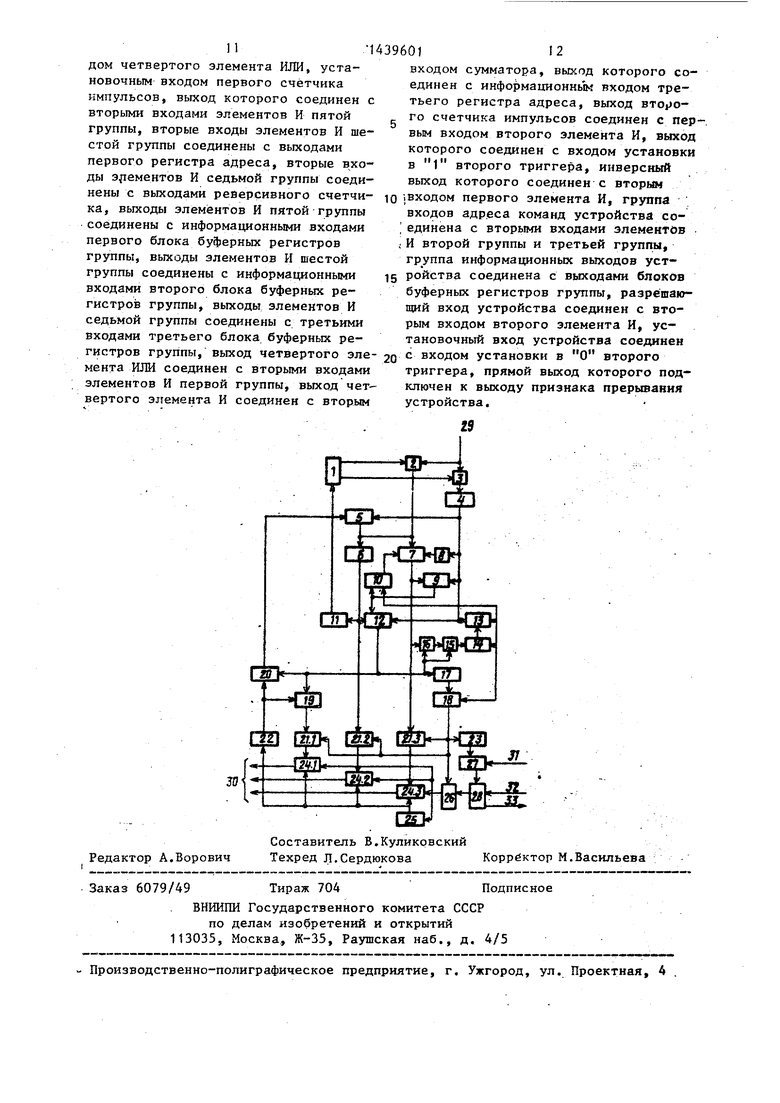

На чертеже представлена структурная устройства о

Устройство содержит первый триггер 1, вторую группу элементов И 2, третью группу элементов ИЗ, второй регистр адреса 4, первуй группу элементов И 5, первый регистр 6 адре- |Са, счетчик 7 адреса, первый зле- мент ИЛИ 8, первую схему 9 сравнения, третий элемент ИЛИ 10, второй элемент ИЛИ 11, вторую 12 и третью 13 схемы сравнения, третий регистр 14 адреса, сумматор 15, четвертую группу элементов И 16, элемент HEJ7, пятый эле- нент ИЛИ 18, первый счетчик 19.им- пульсов, четвертьй элемент ИЛИ 20, . пятую, шестую и седьмую группы элементов 21.1,.21.2 и 21.3 соответственно, шестой элемент ИЛИ 22, второй счетчик 23 импульсов, с первого по . третий блоки буферных регистров груп- пы 24.1, 24.2 и 24.3 соответственно, распределитель 25 импульсов, первый элемент И 26, второй элемент И 27, второй триггер 28, группу адресных входов 29 устройства, группу информационных выходов 30 устройства, управляющий вход 31 устройства5 вход 32 установки устройства, выход 33 признака прерывания устройства. - .

Первый триггер 1 предназначен для управления потоком адресов отлаживаемой программы.

Регистры 4, 6 и 14 адреса предна-эначены для приема, хранения и вьща- чи п-разрядного кода исполнительного адреса, поступающего параллельным кодом на группы адресных входов регистров.

Счетчик 7 адреса служит дня кране ния адреса программы, который может инкрементироваться и декрементиро- , ваться.

Схемы 9, 12 и 13 сравнения пред- назйачены для сравнения адресов и вы работки сигнала Равно.

Сумматор 15 предназначен для вы-. полнения операции сложения,

5 0 5 Q - 0

5

5

Счетчик 19 импульсов предназначен для счета импульсов и обнуляет свое значение по установочному входу.

Счетчик 23 импульсов (кольцевой) предназначен для счета импульсов и . вырабатывает сигнал на выходе при его переполнении.

Группа блоков 24 буферных регистров состоит иэ п-регистров, преднаг значенных для приема, хранения и выдачи п-разрядного параллельного кода. На каждом входе всех регистров установлены элементы И на три входа. Первые входы всех элементов И объединены и ябляются входом записи блока. Вторые входы элементов И также объединены и образуют группу управляющих входов. Третьи входы каждого элемента И объедкнепы в.группу информационных входов блока,

Распределитель 25 импульсов предназначен для коммутации информации, которая поступает в группу блоков буферных регистров

Второй триггер 28 предназначен для формирования сигнала прерывания устройства,

Устройство работает следующим образом,

Адрес начапьной команды, поступа-. ющий по вкоду 29 через группу элементов И 2, записывается в счетчик 7 адреса и первый регистр 6 адреса. После того, как адрес начальной команды запишется в регистр 6, сигнал : с выхода элемента ИЛИ 11 устанав- ; ливает триггер 1 в состояние Б результате,группа элементов И 2 запирается и открывается группа эле- ментов ИЗ. Такое состояние тригге- ра 1 сохраняется до тех пор, пока устройство не будет установлено в исходное состояние,,

Адрес следующей команды со входа 29 через группу элементов И.З, запомнившись во втором регистре 4 адреса, поступает на первые входы трех схем сравнения 9, 12 и 13 и на вход первого элемента lOTi S. На выходе первого элемента ИЛИ 8 появляется сигнал, который увеличивает содержимое счетчика 7 адреса на единицу. На второй вход первой схемы 9 сравнения с выхода счетчика 7 адреса nor ступит увеличенный на единицу адрес предьщущей команде. В зависимости от результата этого сравнения реализуются два режима работы устройства.

Первый режим работы устройства. Если-содержимое второго регистра 4 равно содержимому счетчика 7 (т.е. в ЭВМ выполняются команды с последовательными адресами), то схема 9 сравнения вырабатывает сигнал логического О, и устройство переходит в режим ожидания изменения . в ЭВМ команды.

Работа устройства в данном случае соответствует выполнению в ЭВМ непрерывной цепочки команд с после- довательными адресами. При этом содержимое регистра 6 определяет первую команду (нижний адрес набора адресов команд) набора выполненных команд, а на счетчике 7 происходит увеличение верхней границы набора адресов команд.

В том случае, когда содержимое с счетчика 7 и регистра 4 не равны (т.е. адрес последующей команды отличается от предыдущего на число, отличное от единицы), работа уст- .ройства соответствует переходу в программе от одного линейного набора команд к другому. В этом случае схема 9 сравнения вьфабатывает сигнал логической 1, который, переходя через элемент ИЛИ 10, уменьшает содержимое счетчика 7 адреса на единицу (производят возврат к адресу

15

яш1яется едмпич ный cHrtian. Сигнал выхода элемента И 26 постугшет так же на первые пходы каждого из груп пы 24 блоКс-1 буферных регистров, что разрешает запись содержимого регист ра 7 адреса в третий блок буферных регистров, содержимого регистра 6 в второй блок и содержимого счетчика

50 19 импульсов в первый блок. Одновре менно сигнал с выхода распределител 25 импульсов через элемент ИЛИ 22 о нуляет содержимое счетчика 19 импул сов и далее через элемент ИЛИ 20 ра решает перезапись через элемент И 5 содержимого регистра 4 в регистр 6 и счетчик 7, т.е. устройство подготовлено для приема и обработки ново последовательности адресов, нижний адрес которой записан в регистре 6. Если содержимое регистра 4 равно содержимому регистра 6 (т.е. вновь поступивший адрес совпадает с.нижни адресом только что выполненной посл

25 довательности команд, что свидетель ствует о выполнении в программе цик лического участка), то схема сравне ния 12 вырабатывает сигнал логической 1, который увеличивает содер

3Q жимое счетчика 19 на единицу, инвертировавшись элементом НЕ 17 и не разрешает перезапись содержимого счетчика 7 адреса, регистра 6 и сче чика 19 в группу 24 блоков буферных регистров. Этот же сигнал поступает

20

команды, от которой производится пере-- на первые входы сумматора 15 и эле- дача управления в программе). Кроме ментов И 16, в результате чего сотого, по этому же сигналу схема 12 сравнения производит сравнение нижнего адреса исполненного набора адресов команд с вновь поступившим из регистра 4 адреса (нижний адрес новой последовательности адресов команд). В этом случае осуществляется второй режим работы.

Если содержимое регистра 4 не рав- сравнения через элемент ИЛИ 20 и

40

держимое счетчика 7 адреса через элементы И 16, увеличившись на единицу в сумматоре 15, запоминается в третьем регистре 14 адреса (т..е. в регистре 14 запоминается адрес первой команды, следующей за последней командой циклического участка).Кроме того, сигнал с выхода схемы 12

но содержимому регистра 6 (т.е. переход программы от одного набора адресов команд к другому не является циклическим), то элемент 12 сравнения вырабатывает логический О, который инвертируется элементом НЕ 17 через элемент ИЛ1 18, увеличивает содержимое счетчика 23 на единицу, открывав ВТ элементы И группы 21, элемент И 26, с выхода которого поступает . сигнал на управляющий вход распреде- лителя 25 импульгои, и на первом выходе распределителя 25 импульсов поэлементы И 5 группы разрешает перезапись содержимого регистра 4 в регистр 6 и счетчик 7. В дальнейшем устройство работает во втором режиме

SO до поступления в регистр 4 адреса первой команды, следующей за последней командой циклического участка, В этом случае схема 13 сравнения вырабатывает сигнал сравнения - логи55 ческую 1, по которому содержимое счетчика 7 адреса уменьшается на еди ницу (т.е. восстанавливается адрес команды верхней границы циклическо15

439601

яш1яется едмпич ный cHrtian. Сигнал с выхода элемента И 26 постугшет также на первые пходы каждого из группы 24 блоКс-1 буферных регистров, что разрешает запись содержимого регистра 7 адреса в третий блок буферных регистров, содержимого регистра 6 во второй блок и содержимого счетчика

50 19 импульсов в первый блок. Одновременно сигнал с выхода распределителя 25 импульсов через элемент ИЛИ 22 обнуляет содержимое счетчика 19 импульсов и далее через элемент ИЛИ 20 разрешает перезапись через элемент И 5 содержимого регистра 4 в регистр 6 и счетчик 7, т.е. устройство подготовлено для приема и обработки новой последовательности адресов, нижний адрес которой записан в регистре 6. Если содержимое регистра 4 равно содержимому регистра 6 (т.е. вновь поступивший адрес совпадает с.нижним адресом только что выполненной после25 довательности команд, что свидетельствует о выполнении в программе циклического участка), то схема сравне- ния 12 вырабатывает сигнал логической 1, который увеличивает содер-

3Q жимое счетчика 19 на единицу, инвертировавшись элементом НЕ 17 и не разрешает перезапись содержимого счетчика 7 адреса, регистра 6 и счет-- чика 19 в группу 24 блоков буферных регистров. Этот же сигнал поступает

20

е-- на первые входы сумматора 15 и эле- ментов И 16, в результате чего сона первые входы сумматора 15 и эле- ментов И 16, в результате чего со

держимое счетчика 7 адреса через элементы И 16, увеличившись на единицу в сумматоре 15, запоминается в третьем регистре 14 адреса (т..е. в регистре 14 запоминается адрес первой команды, следующей за последней командой циклического участка).Кроме того, сигнал с выхода схемы 12

элементы И 5 группы разрешает перезапись содержимого регистра 4 в регистр 6 и счетчик 7. В дальнейшем устройство работает во втором режиме

до поступления в регистр 4 адреса первой команды, следующей за последней командой циклического участка, В этом случае схема 13 сравнения вырабатывает сигнал сравнения - логическую 1, по которому содержимое счетчика 7 адреса уменьшается на единицу (т.е. восстанавливается адрес команды верхней границы циклическо

го участка, производится гашение регистра 14 и через элемент ИЛИ 18 раз решается перезапись содержимого счетчика 19 импульсов, регистра 6 и счетчика 7 адреса в группу 24 блоков буферных регистров. По окончании записи сигнал с элемента ИЛИ 22 обнуляет содержимое счетчика 19 импулъ сов и через элементы ИЛИ 20 и И 5 осуществляет перезапись содержимого регистра 4 в регистр 6 и счетчик 7 адреса (т.е. ноной нижней границы очередной последовательности адресов команд),

Счетчик 23 считает количество выведенных в группу 24 блоков буферных регистров записей и выдаёт сигнал переполнения при выводе m записей (т - емкость каждого из блоков буфер- ньк регистров).

Сигнал переполнения поступает на первый вход элемента И 27 и при условии разрешения по входу 31 устройства поступает на первьш вход триг- гера 28. С прямого выхода триггера 28 поступает сигнал в приоритетную систему ЭВМ, сообщая о за полнении всех регистров блоков 24. Нулевой сигнал с инверсного выхода триггера

28 поступает на второй вход элемента И 26 и блокирует распределитель 25 импульсов и группу 24 блоков буфер™ ных регистров

Блокировка обеспечивает сохранение содерткимого блоков 24 до его переписи через группу выходов 30 в оперативную память ЭВМо После переписи содержимого блоков буферных регистров в оперативную память ЭВМ триггер 28 сбрасЫ зается сигналом по входу 32 и тем самым подготавливает группу 24 блоков буферных регистров к выводу m очередных записей,

Таким образом, в оперативную па- мять ЭВМ выведены m записей, состоящих из нижнего адреса набора команд верхнего адреса набора команд и чис- 1ла С, характеризующего количество ч. прохождений циклических участков: ее ли С О, то участок линейный и, следовательно, выполняеч ся один раз; если С f С), то участок диклическт-й и число возвратов к нижней границе цик ;лического участка равно С.

Особенлост - работы устройства при прохождении программой линейных и циклических участков представле а иа следующем примере.

1439601 6

Пусть га вход устройства поступает последовательность адресов команд;

а, ,

а е

а, а.

ад )

34

аз

а

4

Я 4

6 6

а,

а, а , ag j ag,

Рассмотрим процесс формирования последовательности записей A-f при работе предлагаемого устройства.

ESk

При поступлении первой исполняамой команды ее адреср: а запоминается в регистре 6 адреса и счетчике 7 адреса. Триггер 1 в дальнейщем обеспечивает приход следующих адресов команд на регистр 4 адреса. При поступ лении последовательности команд с адресами а, аэ, и a/j схема 9 сравнения вырабатывает сигнал сргв- нения - логический О, а содержимое счетчика адреса 7 увеличивается последовательно на единицу. Таким.образом, к моменту прихода команды с адресом аз содержимое регистра 6 адре са В a..j5 счетчика 7 адреса Е а,,(. Адрес команды а изменяет содержимое счетчика 7 адреса Е ад первая схема сравнения вырабатывает сигнал ие- сравнения - логическую который через третий элемент ИЛИ 10 уменьшает содержимое счетчика 7 на единицу, т.е. Е - a,j, и разрешает сравнение второй схемой 12 сравнения содержимого регистра 6 с адресом aj Поскопь ку а ал, сигнал несравнения - логический О, инвертировавшись элементом НЕ f7s разрешает перезапись coAepKiiHoro счетчика 19 импульсов, . регистра б адреса и счетчика 7 адре- , , са в соответствующие блоки группы 24 блоков буферных регистров. Поскольку в исходном состоянии содержимое (Ьм И г, Из) всех блоков 24 и счетчика импульсов 19 (с) имеет вид

С 0;

H-t (О,0,,,.J))|

lij - (О,0,,.,.,0);

И - (О,0,...,0),

то после выводапервой записи .содержимое блоков 24изменяется следующим образом:

7

Н (О, 0,..„,0);

(л, 0,...,0); . Н (а/}, 00) .

После вывода записи по сигналу через элементы ИЛИ 20 и 22 и элементы И 5 содержимое регистра 4 переписывается в регистр 6 и счетчик 7 адреса, т.е. . Следующий пришедший адрес а изменяет содержимое счетчика 7 на Е a/j, схема 9 сравнения вырабатывает сигнал сравнения - логический О и устройство переходит в режим ожидания следующего адреса. Следующий адрес а. Содержимое счетчика 7 становится равным Е aj. Схема 9 сравнения выработает сигнал несравнения - логическую 1, который изменяет значение Е, Е разрешает сравнение схеме 12 сравнения содержимого регистра

6В aj и адреса а. Сигнал сравнения - логическая 1 увеличивает с содержимое счетчика 19 С 1, откры- вает группу элементов И 16, с т матор

15 увеличивает содержимое счетчика

7адреса на единицу и в регистре 14 адреса запоминается адрес К а. Этот же сигнал разрешает запись через элемент ИЛИ 20 и группу элементов И 5 содержимого регистра 4 в регистр 6 и счетчик 7, т.е. В а, к

Е aj. При поступлении в последующем последовательности адресов

3;), аз, ад, аз, а, aj, а

устройство работает аналогично, содержимое регистра 6 и счетчика 7 обновляется на aj с поступлением команд с адресом ад, в этот же момент счетчик 19 импульсов увеличивает свое содержимое на единицу, а схема 13 сравнения вырабатывает сигнал не сравнения - логический О, не влияющий на работу устройства Таким образом, к моменту прихода команды с адресом а (адрес первой команды по выходу из циклического участка) содержимое счетчика 19 будет равно С 5, регистра 6 В ад и счетчика 7

Е Д4.

Адрес а,5 увеличивает содержимое счетчика 7 адреса на единицу, т„е. Е - а5, схема 9 сравнения вырабатывает сигнал сравненяя - логический О

396018

а схема 13 срапкения вырабатывает признак сравнения - логическую 1. Последний сигнал гасит содержимое регистра 14 и через элемент ИЛИ 10 уменьшает содержимое счетчика 7 на .единицу, т,ео Е а и через элемент 1ШИ 18 разрешает запись содержимого регистра 6, счетчика 7 и счетчика 19 10 S группу 24 блоков буферных регистров, так что

Н (О, 5, 0,...,0); 15 HIJ (а, aj. О,. ..,0); Н э (, ajf. О, ...,0).

После вывода записей содержимое 20 счетчика 19 импульсов обнуляется, а содержимое регистра 6 адреса и счетчика 7 адреса станет равным В , Е а.

Следующий адрес ад увеличивает со- 25 держимое счетчика 7 адреса на единицу, т.е. Е а. Следующий адрес ag, Е , схема 9 сравнения вырабатывает сигнал несравнения - 1, которьй уменьшает значение Е а, схема 12 30 сравнения вырабатывает сигнал несравнения - О, который, инвертировавшись элементом НЕ 17, разрешает перезапись содержимого регистра 6, счетчика 7 и счетчика 19 в группу 24 блоков буферных регистров, т,е.

35

40

Н (О, 5, О, 0,...,0); Hj (а,,, аз, , 0,...,0); Из (ац, а4, ag, 0,...,0),

, и разрешает перезапись содерзкимоего регистра 4 в регистр 6 и счетчик 7,

д т.е. В ag, Е ag. Адрес следующей комавды ag приводит к появлению на выходе схемы 9 сравнения сигнала 1, который уменьшает содержимое счетчика 7 на единицу, Е . Схема 12 сравнения вырабатывает признак сравнения - 1, содержимое счетчика 19 увеличивается на единицу, а в регистре 14 адреса записывается адрес а. Таким образом, к моменту прихода , адреса aj, содержимое счетчика адреса С 3. Адрес л/ увеличивает содержимое счетчика 7 на единицу, Е ау. Схема 13 сравнения вырабатывает сиг- нал сравнения 1, который через

элемент ИЛИ Ш изменяет содержимое счетчика 7, т.е. Е ag, гаснт содержимое регистра 14 я через элемеит ИЛИ 18 разрешает вывод очередной записи в блоки буферных регистров 24 Таким образом:

Нч (О, 5, О, 3, 0,...,0); Н2 (а, aj, а,,-, ag,..,0); 3 4 а ag,...,0).

Содержимое регистра 6 и счетчика 7 становится равным В - а, Е а,р.

Таким образом, последовательность записей , сформированная предлагае NbiM устройством,имеет вид

О, а, ад; -. 5, аз,

AI - О 5 6 3, ag, ag;

« в j 7 5 в

Формула изобретения

Устройство для контроля программ содержит первьиЧ и второй регистры адреса, первую схему сравнения, первый и второй элементы ИЛИ, счетчик адреса, первую группу элементов И и первый триггер, причем выходы элементов И первой группы соединены соответственно с информационныг- и входами первого регистра адреса и счетчика адреса, суммирующий вход которого соединен с выходом первого элемента ИЛИ, входы которого, первые входы элементов И первой группы, первая группа входов первой схемы сравнения соединены с выходами вто рого регистра адреса, вход установки в 1 первого-триггера соединен с выходом второго элемента ИЛИ входы которого соединены с выходами пер вого регистра адреса, информационны выходы счетчика адреса соединены с второй группой входов первой схемы .сравнения, отличающееся тем,, что, с целью повышения достоверности работы устройства, в него введены со второй по седьмую группы элементов И, первый и второй элемен39601 iO

ты И, первый и второй счетчики импульсов, вторая и третья схемы сравнения, сумматор, третий регистр адреса, элемент НЕ, третий, четвертый, пятый и шестой элементы ИЛИ, второй триггер, группа блоков буферных регистров и распределитель импульсов, причем первые входы элементов И вто- Q рой группы соединены с инверсным выходом первого триггера, первые входы элементов И третьей группы соединены с прямым вьрсодом первого триггера, выходы элементов И второй 5 группы соединены с информационными входами счетчика адреса, выходы элементов И третьей группы соединены с информационными входами второго регистра адреса, первые входы элемен- 2Q тов И четвертой группы соединены с вькодами счетчика адреса, выход первой схемы сравнения соединен с разрешающим входом второй схемы сравнения и первьгм входом третьего элемеи- 25 та ИЛИ, выход которого соединен с вычитающим входом счетчика адреса, выход второго регистра адреса соединен с первым информационным входом второй схемы сравнения и, первым -информацион- 30 ным входом третьей схемы сравнения, . второй информацио11ньй вход которой соединен с выходом третьего регистра адреса, выход второй схемы сравнения соединен с.первым входом четвертого элемента ИХШ, с суммирующим входом первого счетчика импульсов, с вторыми входами элементов И четвертой группы, с первым входом сугматора, с входом, элемента НЕ, выход которого соединен с первым входом пятого элемента ИЛИ, выход третьей схемы сравнения соединен с вторым входом третьего элемента ИЛИ, входом синхронизации третьего регистра адреса, вторым входом пятого элемента IinH, выход которого соединен с суммирующим .входом второго счетчика импульсов, первыми входами злеметгтов И пятой, шестой, седьмой групп, первым входом первого элемента И, выход которого соединен с входами записи первого, второго и третьего блоков буферных регистров группы, с входом пуска распределителя импульсов, выход которого соединен с входами снн- хронизации первого, второго и третьего блоков буферных регистров группы, входом шестого элемента ШШ, выход которого сое щнен с вторым вхо35

40

45

ПО

55

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1982 |

|

SU1049914A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1562921A1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

| Адаптивное устройство микропрограммного управления | 1984 |

|

SU1290317A1 |

| Устройство для ввода информации | 1980 |

|

SU924690A1 |

| Устройство тестового контроля | 1989 |

|

SU1691842A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1695372A1 |

| Устройство для отладки программ | 1984 |

|

SU1166122A1 |

| Устройство для распаковки команд | 1984 |

|

SU1251075A1 |

| Устройство для распаковки команд | 1990 |

|

SU1702367A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля программ. Цель изобретения - повышение достоверности работы. Устройство поз.воляет исключить повторную запись в памяти устройства адресов границ циклических участков и организовать своевременную вьщачу информации в оперативную память ЭВМ при заполнении памяти устройства, .что приводит к повышению на дежности устройства и сокращению объема информации о ходе вьшолнення программы без снижения ее достоверности. Адрес границ линейного участка и число его повторений хранятся в блоках буферных регистров. Триггер управляет перезаписью содержимого в оперативную память ЭВМ. Устройство подсчитывает количество циклических участков, количество записей в буфер И; вьфабатывает сигнал прерывания при переполнении буфера. Устройство для контроля програьт содержит два триггера, семь групп элементов И, два элемента И, шесть элементов ИЛИ, блок буферных регистров, распределитель импульсов, два счетчика импульсов, с четчик адреса, три регистра адреса, инвертор,сумматор и три схемы сравнения. 1 ил. (Л

| Патент США № 3931611, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Способ запуска криогенного насоса | 1980 |

|

SU879363A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-11-23—Публикация

1987-04-01—Подача