Изобретение относится к цифровой вычислительной технике, а именно к ОЗУ, содержащим средства контроля достоверности и исправления ошибок хранимой информации и предназначенным для использования в высоконадежных цифровых вычислительных системах.

Целью изобретения является упрощение контроля устройства

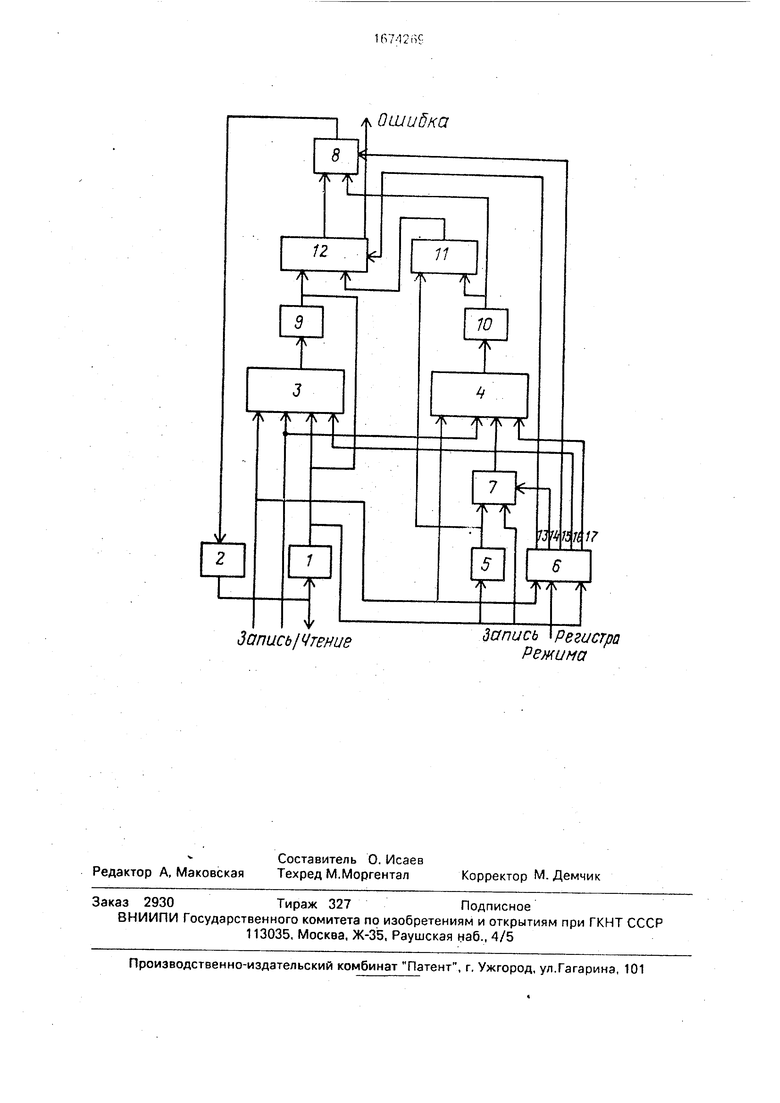

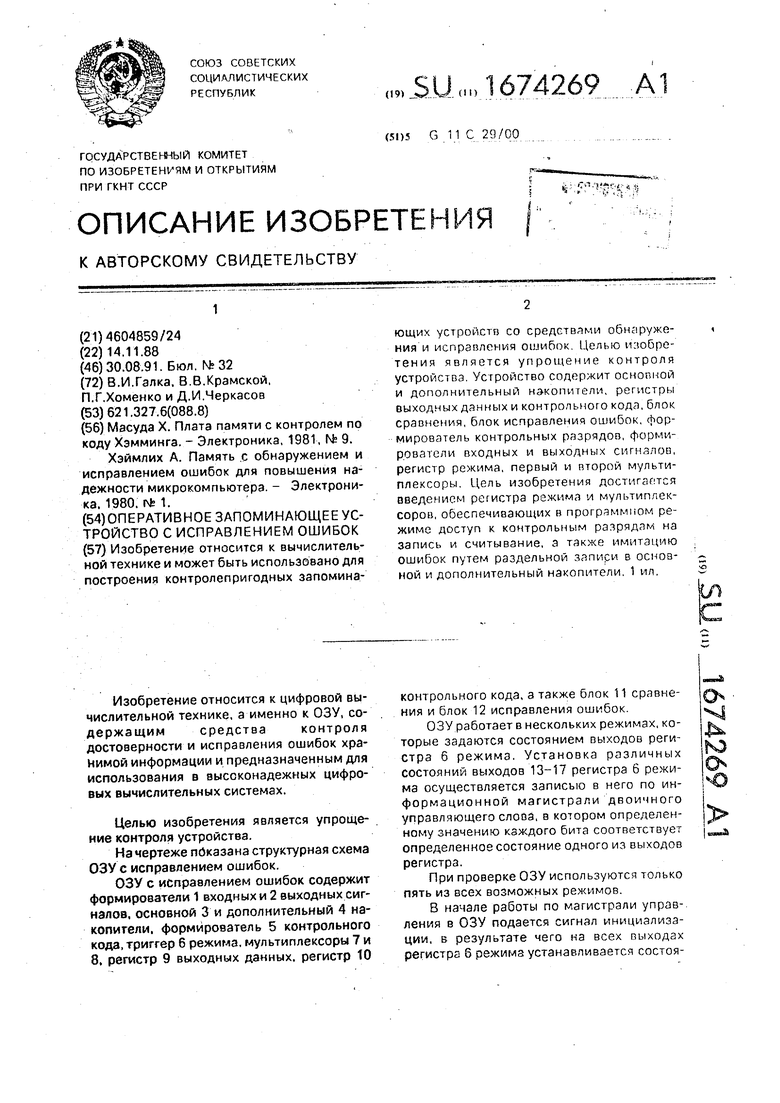

На чертеже показана структурная схема ОЗУ с исправлением ошибок.

ОЗУ с исправлением ошибок содержит формирователи 1 входных и 2 выходных сигналов, основной 3 и дополнительный Л накопители, формирователь 5 контрольного кода, триггер б режима, мультиплексоры 7 и 8, регистр 9 выходных данных, регистр 10

контрольного кода, а также блок 11 сравнения и блок 12 исправления ошибок

ОЗУ работает в нескольких режимах, которые задаются состоянием пы/одоь регистра 6 режима. Установка различных состояний выходов 13-17 регистра б режима осуществляется записью в него по информационной магистрали двоичного управляющего слооа, в котором определенному значению каждого бита соответствует определенное состояние одного из выходов регистра.

При проверке ОЗУ используются только пять из всех возможных режимов.

В начале работы по магистрали управления в ОЗУ подается сигнал инициализации, в результате чего на всех выходах регистра 6 режима устанавливается состояО

ю о

ние логического нуля, что соответствует переводу ОЗУ в режим 1.

Первый режим является рабочим режимом ОЗУ. На вход запрещения исправления ошибок блока 12 исправления ошибок уп- равляющие входы мультиплексоров 7 и 8, входы запрещения записи основного и дополнительного 4 накопителей поступают сигналы логического нуля, что соответствует разрешению исправления ошибки бло- ком 12, передачи информации с выходов формирователя 5 мультиплексором 7 и информации с информационных выходов блока 12 мультиплексором 8 и разрешению записи в оба накопителя 3 и 4. При записи в первом режиме информация, поступающая через формирователь 1 входных сигналов с информационной магистрали, записывается в основной накопитель 3, а ее контрольный код, формируемый формиро- вателем 5, записывается в дополнительный накопитель 4, поступая на его информационные входы через мультиплексор 7. При чтении информация, считываемая из основного накопителя 3, через регистр 9 выход- ных данных поступает на информационные входы блока 12 исправления ошибок. Одновременно формирователь 5 формирует контрольный код этой информации, который поступает на один из входов блока 11 срав- нения. На другие входы блока 11 сравнения через регистр 10 контрольного кода поступает контрольный код, считываемый из дополнительного накопителя 4. При равенстве указанных кодов на выходе блока 11 срав- нения кодов формируется признак отсутствия ошибки, который поступает на входы признака ошибки блока 12 исправления ошибок.

Информация, считанная из основного накопителя 3, без изменений передается на выход блока 12, а затем через мультиплексор 8 и формирователь 2 выходных сигналов выдается на информационную магистраль. Одновременно с выхода признака ошибки блока 12 исправления ошибок на магистраль управления выдается сигнал отсутствия ошибки.

В случае отличия кодов, поступающих на входы блока 11 сравнения, последний формирует признак ошибки, поступающий на входы признака ошибки блока 12 исправления ошибок. На основании этого признака в блоке 12 происходит исправление этой ошибки в информации, поступающей на ин- формационные входы блока 12, после чего через мультиплексор 8, формирователь 2 выходных сигналов она выдается на информационную магистраль одновременно с сигналом отсутствия ошибки, поступающим

на магистраль управления с управляющих выходов блока 12, а в случае неисправимой ошибки с выхода блока 12 через мультиплексор 8 и формирователь 2 на информационную магистраль выдается неопределенная информация одновременно с сигналом наличия неисправимой ошибки, поступающим на магистраль управления с выхода признака ошибки блока 12.

Второй режим предназначен для проверки основного накопителя 3 и регистра 9 выходных данных. Второй режим отличается от первого режима подачей сигнала логической единицы на вход запрещения исправления ошибки устройства блока 12 исправления ошибки, что соответствует запрещению исправления ошибок блоком 12.

Запись во втором режиме аналогична записи в первом режиме. При чтении информация, считываемая из основного накопителя 3, без изменения передается через блок 12 исправления ошибок, мультиплексор 8 и формирователь 2 выходных сигналов на информационную магистраль. Таким образом, во втором режиме ошибки, возникающие в основном накопителе 3 или регистре 9 выходных данных, обнаруживаются блоками, подключенными к тем же магистралям адреса, управления и информационной, что и описываемое ОЗУ, путем сравнения считываемой из ОЗУ информации с записанной в него ранее.

Поскольку информация, хранимая в дополнительном накопителе 4. не оказывает влияния на считываемую на ОЗУ информацию, состояние выходов 14 и 17 регистра 6 режима значения не имеет.

Третий режим предназначен для проверки дополнительного накопителя 4 и регистра 10 контрольного кода и отличается от первого режима подачей сигналов логической единицы на управляющие входы мультиплексоров 7 и 8, что соответствует передаче информации мультиплексором 7 с выходов формирователя 1 выходных сигналов, а мультиплексором 8 - с выходов регистра 10 контрольного кода.

При записи в третьем режиме информация, поступающая через формирователь 1 входных сигналов и мультиплексора 7 с информационной магистрали на информационные входы дополнительного накопителя 4, записывается в накопитель 4.

При чтении считываемая из дополнительного накопителя 4 информация через регистр 10 контрольного кода, мультиплексор 8 и формирователь 2 выходных сигналов поступает на информационную магистраль.

Таким образом, в третьем режиме имеется возможность проверки дополнительного накопителя 4 энапо ично проверь пс новного накопителя 3 по втором режим Поскольку информация, хранимая в накопителе 3. не оказывает влияние на счнгыв г- мую на ОЗУ информацию, сосгоямпр выходов 13 и 16 регисгра 6 режима знзче ния не имеет.

Четвертый режим предназначен для проверки формирователя 5 контрольных разрядов при исправных дополнительном накопителе 4 и регистре 10 контрольного кода. Четвертый режим отличается от псового режима подачей сигналя логической единицы на управляющий вход му/i., гиплек- сора 8, что соответствует переда ie мультиплексором 8 информации с выходон регистр 10 контрольного кода.

Запись в четвергом режиме аналогична записи в первом режиме. При чтении ин формация,считываемая из дополнительно го накопителя А. которая представляет собой контрольный код ранее записанной ( ОЗУ информации при условии что запись выполнялась в четвертом режиме, через регистр 10 контрольных разрядов, мультиплексор 8 и формирователь 2 выходныл сигналов передается на ин {юрмационную магистраль.

Таким образом, в четвертом режима имеется возможность проверки формирователя 5 контрольного кодя путем проверки правильности считываемых из ОЗУ контрольных кодов, соответс пующих ранее записанной информации. Поскольку информация, хранимая в основном накопителе 3, не влияет на считываемую из ОЗУ информацию, состояние выходов 13 и 16 регистра б режима значения не имеет.

Пятый режим предназначен для проверки блока 11 сравнения кодов б пока 12 исправления ошибок при исправж i/ основном 3 и дополнительном 4 накопителях, а также формирователе 5 контрольного кода и включает в себя режимы Va и V6. Режим Va отлиоется or первого подачей сигнала логической единицы на вход запрещения записи дополнительного накопителя Л, а режим V6 - подачей сигнала логической единицы на вход запрещения записи основного накопителя 3, что соответствует запрещению записи в накопитель ч (режим Va) и в накопитель 3 (режим V6). Запись в основной накопитель 3 в режиме Va и в дополнительный накопитель 4 в режиме V6 аналогична соответствующим действиям в первом режиме. Отличие от первого режима заключается в том, что при записи в режимах Va и V6 информация, ранее занесенная в дополнительный накопитель 4 (для режима Va) и основной накопитель 3 (для режима V6), сохррчч %тс /, 1 еиие в /а м У 6 аи п гн IHU чтению в первом рох- ип По мсдстл тг-пьное выполнении записи сначала и р- жпмр Va затем и режиме V6 позг тпчет

раздельно записывать ич } прмацч о ц ос ti cm мои накопитель 3, а с от нот i HV- Щий г и контрольный код в дополшме л.чый накопи ге/ Ь V

Таким образом, возможно моделировз0 ние ошибок либо о информации рг нящен- ся п основном н когнпрле , либо в соответствующем ей контрольном коде, хранящемся в дополнительном накопите- /,.-. -1.

5При чтении как п режиме Va, так и в

режиме V6 пнесенные при записи ошибки исправляются п случае исправных блоков 11 ср пнония кодов и блок.ч исправления ошибок Наличие ошибок р информации,

0 гии ыпл мои в пятом режиме из ОЗУ япля- Cit ч следствием отказов указанных блоков 1 I и 1. Проверка ОЗУ п пятом режиме оклю- ччет п себя проверку исправления ошибок в информации, хранящейся в н.т.отшт&ле 3, и

5 проверку отсутствия влияния ошибки в контрольном коде, хранящемся п накопителе 4, на достоверность считываемой из ОЗУ пи- Форм.щии.

ОЗУ с исправлением ошибок может

0 бить также испопьзопзно и качество ОЗУ Оз исправления ошибок с увеличенным obbt.-мом памяти за счет истюльзованич до- полнитсльно о накопителя Л для хранения ич мацип, записываемой п ОЗУ по ин5 (J орм,1ЦИОННОИ магистрали П случае одмиа- копии разрядности основного 3 и дополнительного 4 накопителей возможно получ- чие ОЗУ с удвоенным обгемом памяти

0При этом в каждый момент времени по

пнфоомационной магистрали будет возможен доступ только к одному из накопителей 3, 4, что определяется состоянием выходов регистра 6 режима.

5Для организации работы 03/ без исправления ошибок с увеличенным объемом памяти используются два режима. Шестой режим предназначен для организации доступа по информационной мз истрали к ос0 новному накопителю 3. Шестой режим отличается от первого режима подачей сигналов логической единицы нз н/од запрещен и ч исправления ошибок блока 12 исправления ошибок и вход запрещения за5 писи дополнительного накопителя 4, чюсо- отпстствует запрещению исправления ошибок блоком 12 и запрещению записи в дополнительный накопитель 4.

При записи в ОЗУ информация с информационной магистрали записывается в основной накопитель 3 так же, как и в первом режиме, Чтение ОЗУ в шестом режиме аналогично чтению во втором режиме.

Таким образом, ОЗУ работает в шестом режиме, как ОЗУ без исправления ошибок с основным накопителем 3. Информация, хранимая в дополнительном накопителе А, при этом не разрушается. Поскольку запись в дополнительный накопитель 4 отсутствует, состояние выхода 14 регистра 6 режима значения не имеет.

Седьмой режим предназначен для организации доступа по информационной магистрали кдополнительному накопителю4. По сравнению с первым режимом седьмой режим отличается подачей сигналов логической единицы на управляющие входы мультиплексоров 7,8, а также на вход запрещения записи основного накопителя 3, что соответствует разрешению передачи информации мультиплексором 7 с выходов формирователя 1 входных сигналов, а мультиплексором 8 - с выходов регистра 10 контрольных разрядов и запрещению записи в основной накопитель 3. Запись в ОЗУ в седьмом режиме аналогична записи в третьем режиме. Отличие от третьего режима заключается в обязательном запрещении записи в основной накопитель 3.

Таким образом, в седьмом режиме ОЗУ работает, как ОЗУ без исправления ошибок с дополнительным накопителем 4. Информация, хранимая а основном накопителе 3, при этом не разрушается.

Поскольку информация, хранимая в основном накопителе 3, не влияет на считываемую из ОЗУ информацию, состояние выхода 13 регистра 6 режима значения не имеет.

Введением мультиплексоров и управления раздельной записью в накопители, а также возможности запрещения исправления ошибок в устройстве достигается возможность доступа к содержимому обоих накопителей, а следовательно, проверки их исправности методами проверки ОЗУ без исправления ошибки, а также проверки исправности цепей исправления ошибок, что обеспечивает возможность достоверно установить факт отказа и локализовать его с точностью до узла. Тем самым увеличивается ремонтопригодность устройства, Достоверное диагностирование позволяет выявлять отказы во всех узлах ОЗУ и, таким образом, отличать состояние неисправности устройства от состояния работоспособности.

Использование в работе только исправных ОЗУ дает возможность считать их отказоустойчивость равной расчетной для исправных устройств, которая выше, чем работоспособность устройств.

Формула изобретения

Оперативное запоминающее устройство с исправлением ошибок, содержащее основной и дополнительный накопители, адресные входы и входы записи-считывания которых являются одноименными входами

устройства, а выходы соединены с входами соответственно регистра выходных данных и регистра контрольного кода, выходы которых подключены к входам первой группы соответственно блока исправления ошибок

и блока сравнения, информационные входы основного накопителя соединены с выходами регистра выходных данных, с входами формирователя контрольного кода и с выходами формирователей входных сигналов, входы

которых подключены к выходам формирователей выходныхсигналов и являются информационнымивходами-выходамиустройства, входы второй группы блока исправления ошибок соединены с выходами

блока сравнения, входы второй группы которого подключены к выходам формирователя контрольного кода, а выход признака ошибки блока исправления ошибок является выходом признака ошибки устройства,

отличающееся тем, что, с целью повышения надежности устройства, в него введены регистр режима, первый и второй мультиплексоры, причем входы выборки и информационные входы регистра режима

подключены соответственно к одним из адресных входов устройства и к выходам формирователей входных сигналов, выходы регистра режима с первого по пятый соединены соответственно с управляющими входами блока исправления ошибок первого и второго мультиплексоров и с входами запрещения записи основного и дополнительного накопителей, информационные входы первой и второй групп первого мультиплексора подключены соответственно к выходам формирователя контрольного кода и к одним из выходов формирователей входных сигналов, выходы первого мультиплексора соединены с информационными входами

дополнительного накопителя, информационные входы первой и второй групп второго мультиплексора подключены соответственно к выходам группы блока исправления ошибок и к выходам регистра контрольного

кода, выходы второго мультиплексора соединены с входами формирователей выходных сигналов, синхровход регистра режима соединен с входом записи-считывания устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1644233A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1709396A1 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737511A1 |

| Запоминающее устройство с коррекцией ошибок | 1990 |

|

SU1753492A1 |

| Запоминающее устройство с самоконтролем | 1988 |

|

SU1522292A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737510A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| Запоминающее устройство с исправлением ошибок | 1984 |

|

SU1236559A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения контролепригодных запоминающих устройств со средствами обнаружения и исправления ошибок. Целью изобретения является упрощение контроля устройства. Устройство содержит основной и дополнительный накопители, регистры выходных данных и контрольного кода, блок сравнения, блок исправления ошибок, формирователь контрольных разрядов, формирователи входных и выходных сигналов, регистр режима, первый и второй мультиплексоры. Цель изобретения достигается введением регистра режима и мультиплексоров, обеспечивающих в программном режиме доступ к контрольным разрядам на запись и считывание, а также имитацию ошибок путем раздельной записи в основной и дополнительный накопители. 1 ил.

| Масуда X | |||

| Плата памяти с контролем по коду Хэмминга | |||

| - Электроника | |||

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Хэймлих А | |||

| Память с обнаружением и исправлением ошибок для повышения надежности микрокомпьютера | |||

| - Электроника, 1980 | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-08-30—Публикация

1988-11-14—Подача