(Л

сл кэ

со

4

14)

Изобретение относится к радиотехнике и может быть использовано D радиоприемных устройствах для частотного детектирования в широком диапазоне частот и уровней сигнала.

Цель изобретения - уменьшение нелинейных искажений выходного сигнала .

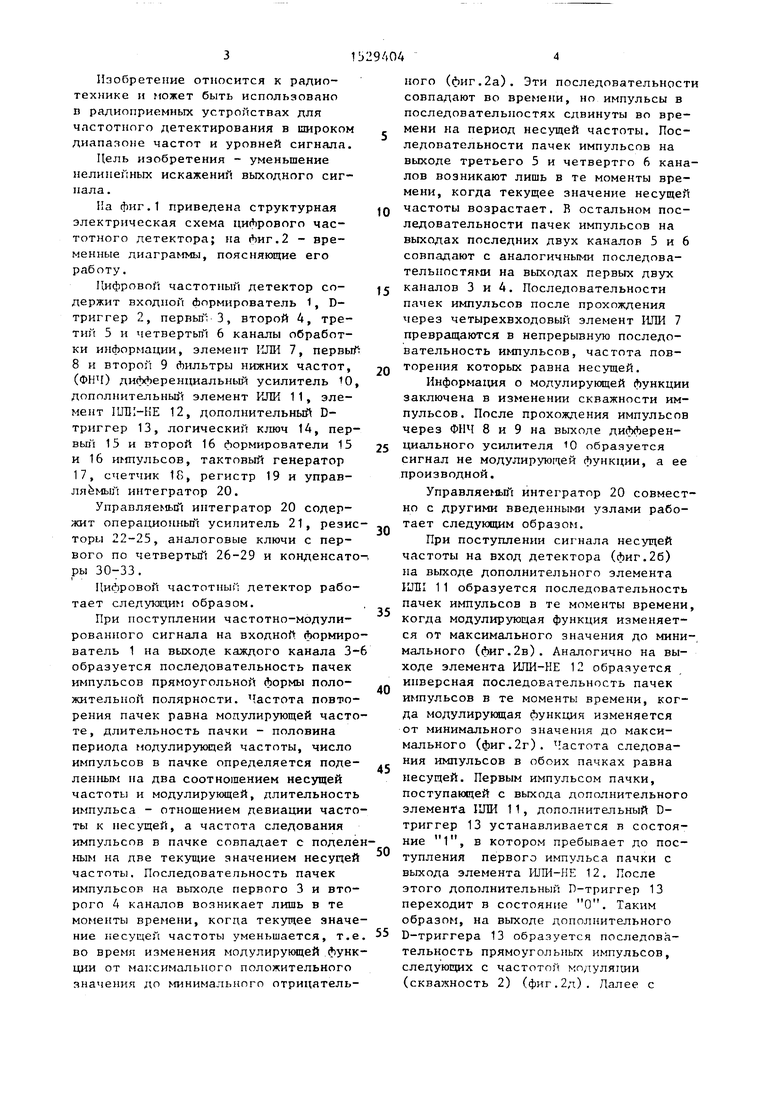

На фиг.1 приведена структурная электрическая схема цифрового частотного детектора; на фиг.2 - временные диаграммы, поясняющие его работу.

Цифровой частотный детектор содержит входной формирователь 1, D- триггер 2, пepвьп 3, второй 4, третий 5 и четвертьп 6 каналы обработки информации, элемент I Jul 7, первый 8 и второй 9 Лильтры нижних частот, (ФНЧ) дифференциальный усилитель Ш, дополнительный элемент ИЛИ 11, элемент 1Ш11-КЕ 12, дополнительный D- триггер 13, логический ключ 14, пер- вьш 15 и второй 16 формирователи 15 и 16 импульсов, тактовый генератор 17, счетчик 18, регистр 19 и управ- ляёмьц интегратор 20.

Управляемьп интегратор 20 содержит операционньп усилитель 21, резисторы 22-25, аналоговые ключи с первого по четвертьп 26-29 и конденсато ры 30-33.

Цифровой частотный детектор работает следующим образом.

При поступлении частотно-модулированного сигнала на входной формирователь 1 на выходе каждого канала 3образуется последовательность пачек импульсов прямоугольной формы положительной полярности. Частота повторения пачек равна модулирующей частоте, длительность пачки - половина периода модулирующей частоты, число импульсов в пачке определяется поделенным на два соотношением несущей частоты и модулирующей, длительность импульса - отношением девиации частоты к несущей, а частота следования импульсов в пачке совпадает с поделеным на две текущие значением несущей частоты. Последовательность пачек импульсов на выходе первого 3 и второго 4 каналов возникает лшпь в те моменты времени, когда текущее значение 1 есу1цей частоты уменьшается, т.е во время изменения модулирующей функции от максимального положительного значения до минимального отрицатель

5

0

5

0

5

0

5

0

5

ного (фиг.2а). Эти последовательности совпадают во времени, но импульсы в последовательностях сдвинуты во времени на период несущей частоты. Последовательности пачек импульсов на выходе третьего 5 и четвертго 6 каналов возникают лишь в те моменты времени, когда текущее значение несущей частоты возрастает. В остальном последовательности пачек импульсов на выходах последних двух каналов 5 и 6 совпадают с аналогичными последовательностями на выходах первых двух каналов 3 и 4. Последовательности пачек импульсов после прохождения через четырехвходовый элемент ИЛИ 7 превращаются в непрерывную последовательность импульсов, частота повторения которых равна несущей.

Информагщя о модулирующей функции заключена в изменении скважности импульсов. После прохождения импульсов через ФНЧ 8 и 9 на выходе дифференциального усилителя 10 образуется сигнал не модулирующей функции, а ее производной.

Управляеньп интегратор 20 совместно с другими введенными узлами работает следующим образом.

При поступлении сигнала несущей частоты на вход детектора (фиг.26) на выходе дополнительного элемента ILTOI 1 1 образуется последовательность пачек импульсов в те моменты времени, когда модулирующая функция изменяется от максимального значения до мини-, мального (фиг.2в). Аналогично на выходе элемента ИЛИ-НЕ 12 образуется инверсная последовательность пачек импульсов в те моменты времени, когда модулирукяцая функция изменяется от минимального значения до максимального (фиг.2г). Частота следования импульсов в обоих пачках равна несущей. Первым импульсом пачки, поступающей с выхода дополнительного элемента ИЛИ 11, дополнительный D- триггер 13 устанавливается в состояние 1, в котором пребывает до поступления первого импульса пачки с выхода элемента ИЛИ-НЕ 12. После этого дополнительный П-триггер 13 переходит в состояние О. Таким образом, на выходе дополнительного D-триггера 13 образуется последовательность прямоугольных импульсов, следующих с частотой модуляции (скважность 2) (фиг.2д). Далее с

515

помощью логического ключа 14 и тактового генератора 17 формируется периодическая последовательность пачек импульсов прямоугольно формы. Длительность пачки равна половине периода модулирующей функции, а число импульсов в пачке - отношению тактовой частоты к модулирующерЧ (фиг.2е). С помощью счетчика 18 осуществляется счет импульсов в пачке. В это время в регистре 19 хранится результат счета импульсов в предыдущей пачке. Счетчик 18 начинает счет в момент времени, например, t и прекращает счет в момент времени t. По заднему фронту импульсов, поступающих с выхода дополнительного D- триггера 13, осуществляется запуск формирователей 15 и 16. По истечении времени t , , которое определяется параметрами первого формирователя 15 с выхода последнего поступает импуль разрешения записи на регистр 19, используемьп в качестве элемента памяти (фиг.2ж). Информация со счетчика 18 переписывается в регистр 19. По истечении времени t дд происходит обнуление счетчика 18 импульсом, поступающим с выхода второго формирователя 16 (фиг.2з). С выходов регистра 19 сигналы управления поступают на соответствующие входы аналоговых ключей 26-29. При этом с выхода первого разряда регистра 19 сигнал управлени поступает на первый аналоговый ключ 26, с второго разряда - на второй аналоговый ключ 27 и т.д. Интегрирующие конденсаторы 30-33 , подключаемые к операционному усилителю 21 через соответствующие аналоговые ключи 26-29 имеют номинальную величину, oпpeдeляe гyю весом соответствующего разряда регистра 19. Если, например, величина конденсатора 30 первого аналогового ключа 26 равна С, то для второго ключа 27 она составляет 2С, для третьего ключа 28 - 4С и т.д. по формуле (где п - номер разряда регистра 19), Количество разрядов может быть произвольным, ем больше используется разрядов, тем точнее работает управляемый интегратор 20. Выходное напряжение управляемого интегратора 20 определяется выражением

и

аых

1

(t) j UB.(t)dt, (1)

4046

из которого слелует, что при постпяп- ных величинах резисторов 22-25 можно с помощью интегрирую1чих кондеисатп- ров 30-33 изменять постоянную времени интегратора.

.Чем больше период модулирующей Аункции, тем большее число записывается в регистр 19 при постоянной тактовой частоте. В этом случае суммарное значение емкости интегрирующих конденсаторов больше. Таким образом, имеется возможность автоматически управлять постоянной времени используемого интегратора в зависимости от частоты модулирующей функ1ЩИ.

20

Формула изобретения

Пифровой частотный детектор п(1 авт.св. 1376226, отличающийся тем, что, с целью уменьшения нелинейных искажений выходного сигнала, введены дополнительны мент ПЛИ, первьп и второй входы кото рого соединены с выходами лержтго и второго каналов обработки информп1.г.1 соответственно элемент , прру/ыг

и второй входы которого сседиье)Ь1 с выходами третьего и -.етвертогс) каналов обработки информаш-ги соствс но, дополнительный D-триггер, тлкто вый вход и вход сброса KOTo;;orii :,v

динены с пыходам1 дополнительного элемента ИЛИ и элемента lilfll-HK cocir ветственно, тактовый генератор, г.е ;- Bbtfi и второй формирователи иг-глул&сои, управляемый интегратор и последовательно соединенные лог ический ключ, счетчик и регистр, выходы которого соединены с управляюшими входами уп равляемого интегратора, вход котор .- го соединен с выходом дифферен1р апь-ного усилителя, л выход управляемого интегратора является пыходом ци()ровгг го частотного детектора, D- вход дополнительного П-триггера подключен к шине логической единицы, а

его выход соединен с управляющими входами логического клича и первого и второго фop D poвaтeлeй импульсов, тактовые входы которых соединены с выходом тактового генератора, л выхо

ды первого и второго сЬорьшрователей импульсов подключены к входу запис.ч регистра и входу сброса счетчика со- ответствен}1о,

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотный детектор | 1984 |

|

SU1307534A1 |

| Цифровой частотный детектор | 1990 |

|

SU1757079A1 |

| Устройство для цифровой записи-воспроизведения цифровой информации | 1990 |

|

SU1788521A1 |

| Устройство конференц-связи для систем с дельта-модуляцией | 1986 |

|

SU1418926A1 |

| Адаптивный восстанавливающий фильтр в дельта-модуляторе с двойным интегрированием | 1990 |

|

SU1795553A1 |

| Цифровой частотный детектор | 1985 |

|

SU1376226A1 |

| СПОСОБ ОБРАБОТКИ ГИДРОАКУСТИЧЕСКИХ СИГНАЛОВ СО СЛОЖНЫМ ЗАКОНОМ МОДУЛЯЦИИ | 2001 |

|

RU2293356C2 |

| Цифровой частотный дискриминатор | 1982 |

|

SU1131036A1 |

| Дельта-модулятор для передачи речевых сигналов | 1990 |

|

SU1795554A1 |

| Устройство для передачи и приема дискретных сигналов | 1990 |

|

SU1758894A1 |

Изобретение относится к радиотехнике. Цель изобретения - уменьшение нелинейных искажений выходного сигнала. Цифровой частотный детектор содержит входной формирователь 1, D-триггеры 2 и 13, каналы 3,4,5 и 6 обработки информации, эл-ты ИЛИ 7 и 11, фильтры 8 и 9 нижних частот, дифференциальный усилитель 10, эл-т ИЛИ-НЕ 12, логический ключ 14, формирователи 15 и 16 импульсов, тактовый генератр 17, счетчик 18, ренгистр 19 и управляемый интегратор 20. Цель достигается за счет обеспечения возможности автоматического управления постоянной времени интегратора 20 в зависимости от частоты модулирующей ф-ции. 2 ил.

.t

фие.г

Y

affi

.i

.2

| Цифровой частотный детектор | 1985 |

|

SU1376226A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-12-15—Публикация

1987-07-20—Подача