Изобретение относится к импульсной технике и может быть использовано в устройствах обработки информации.

Цель изобретения - расширение функциональных возможностей за счет обеспечения селекции импульсов с длительностью t 2. Т (где k I,2,...,NJ Т - период следования импульсов генератора импульсов; N - число разрядов первого счетчика импульсов).

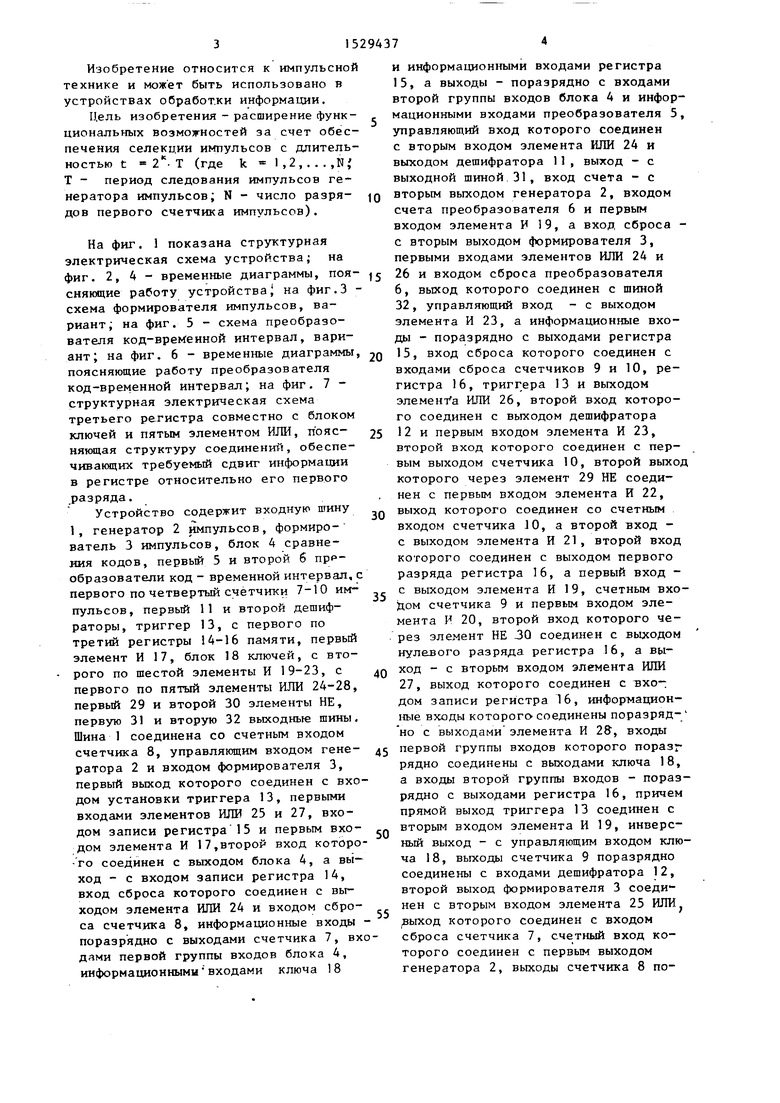

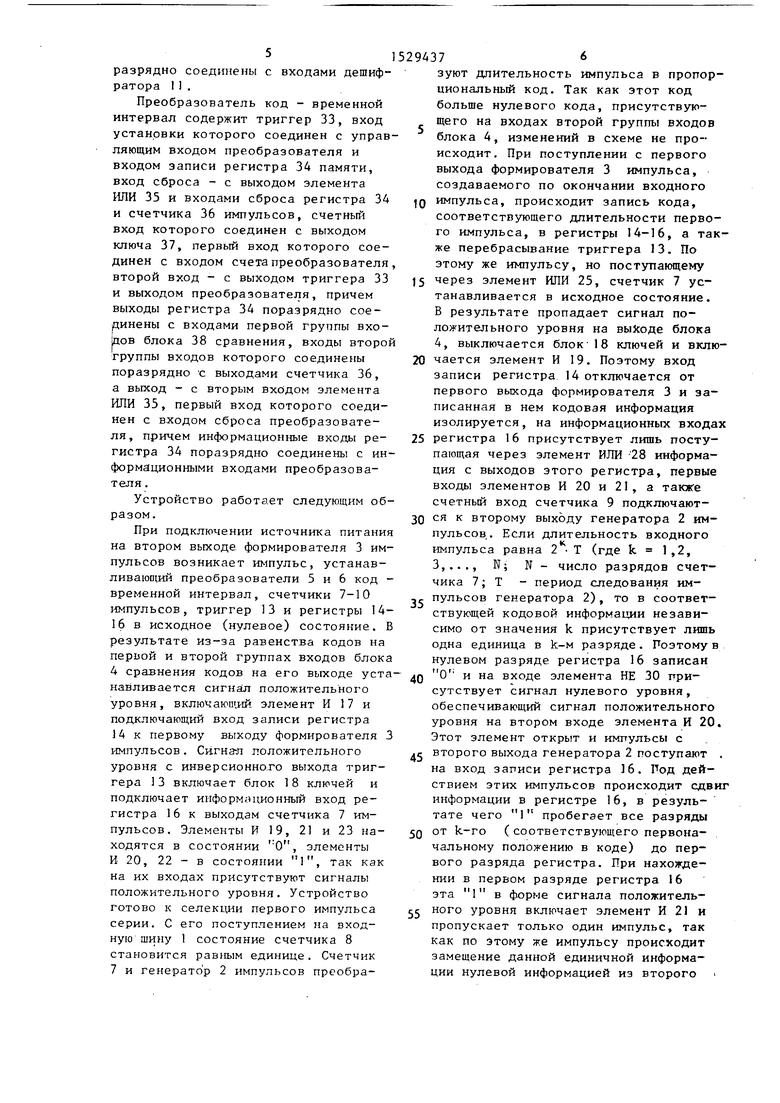

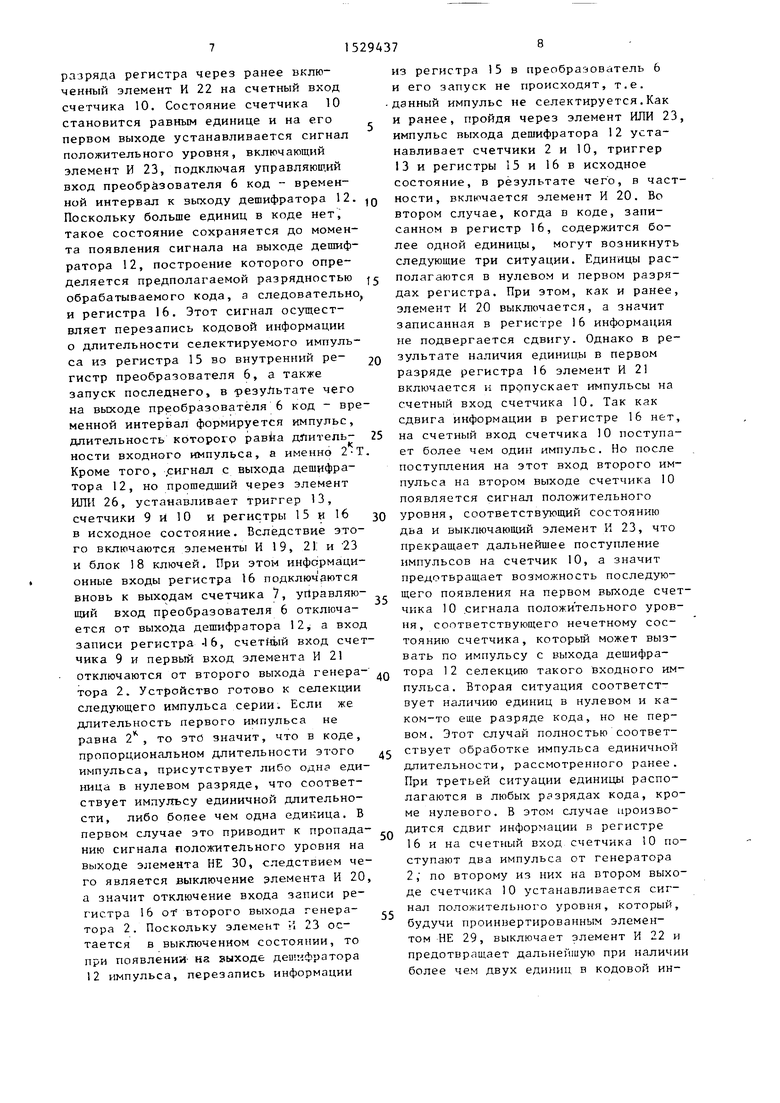

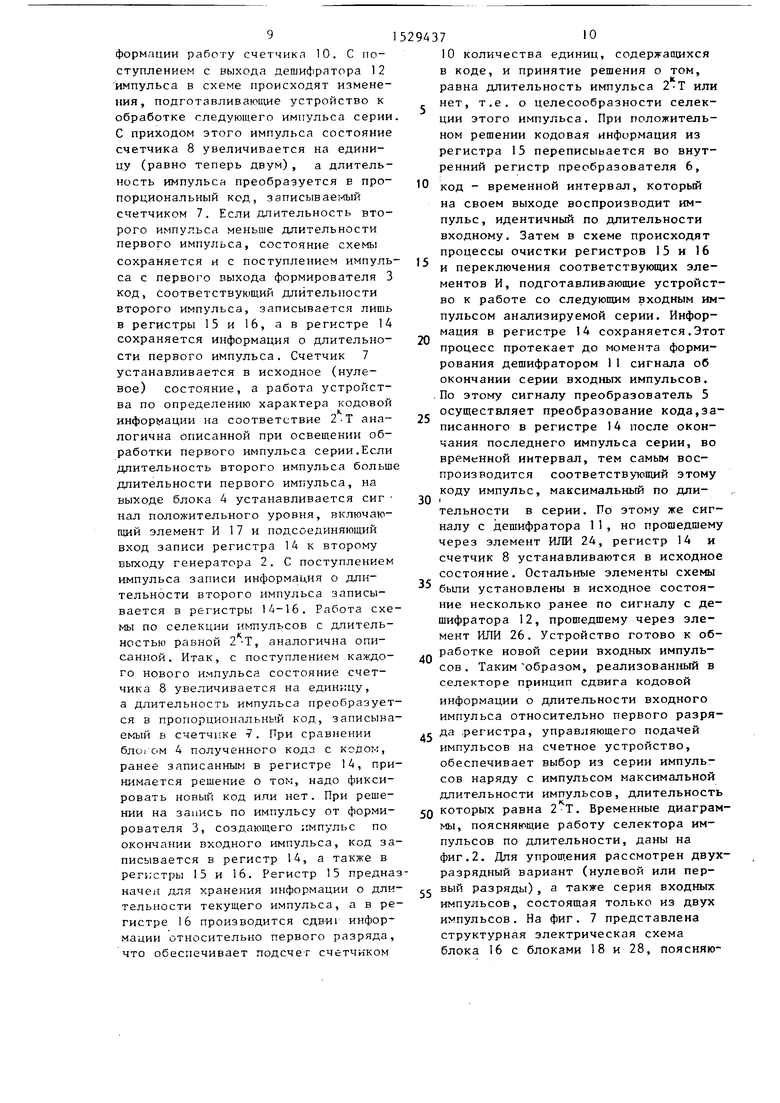

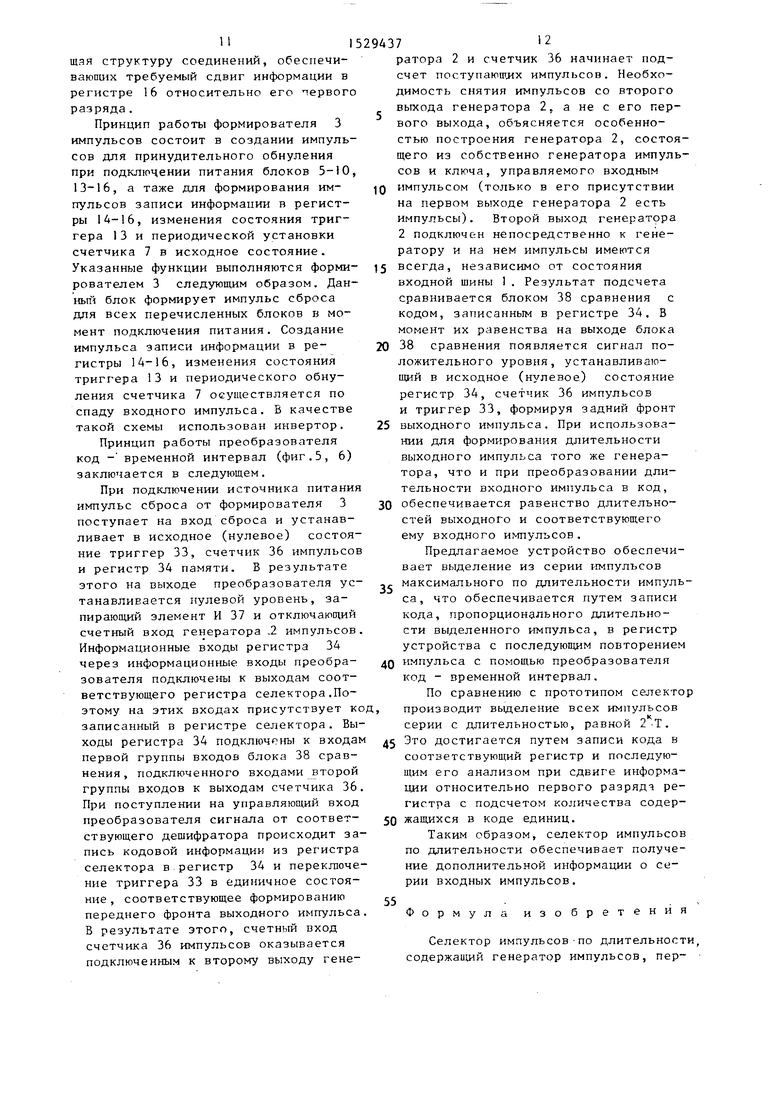

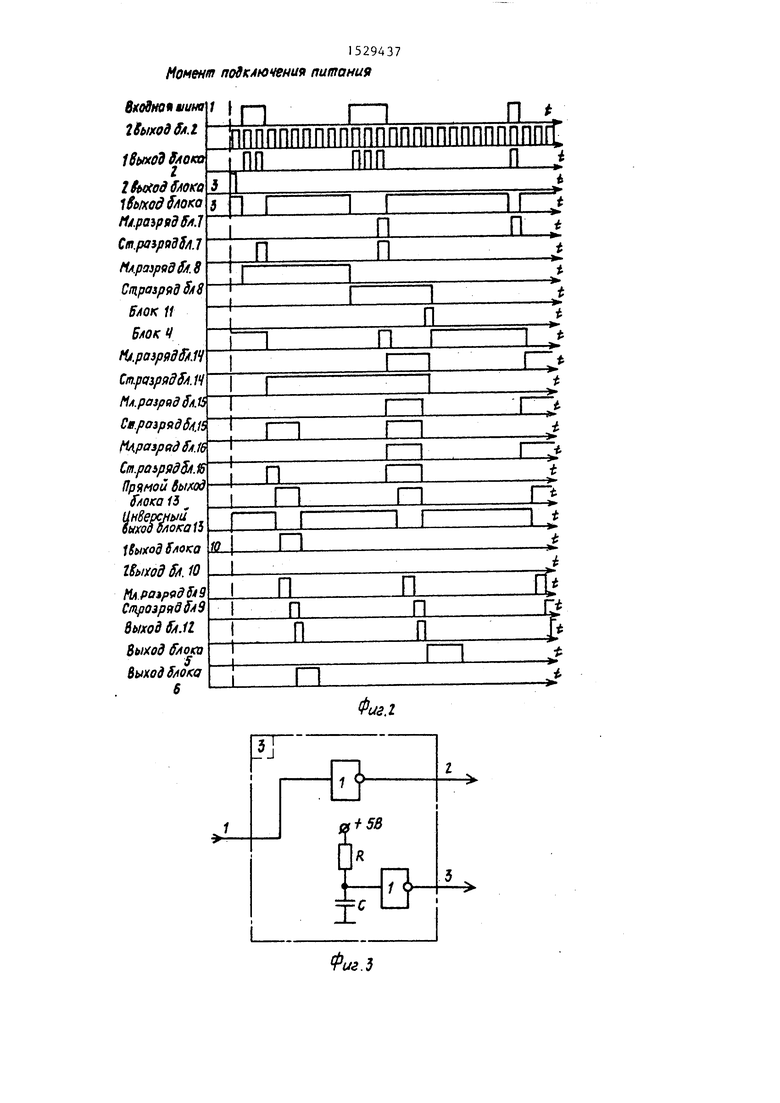

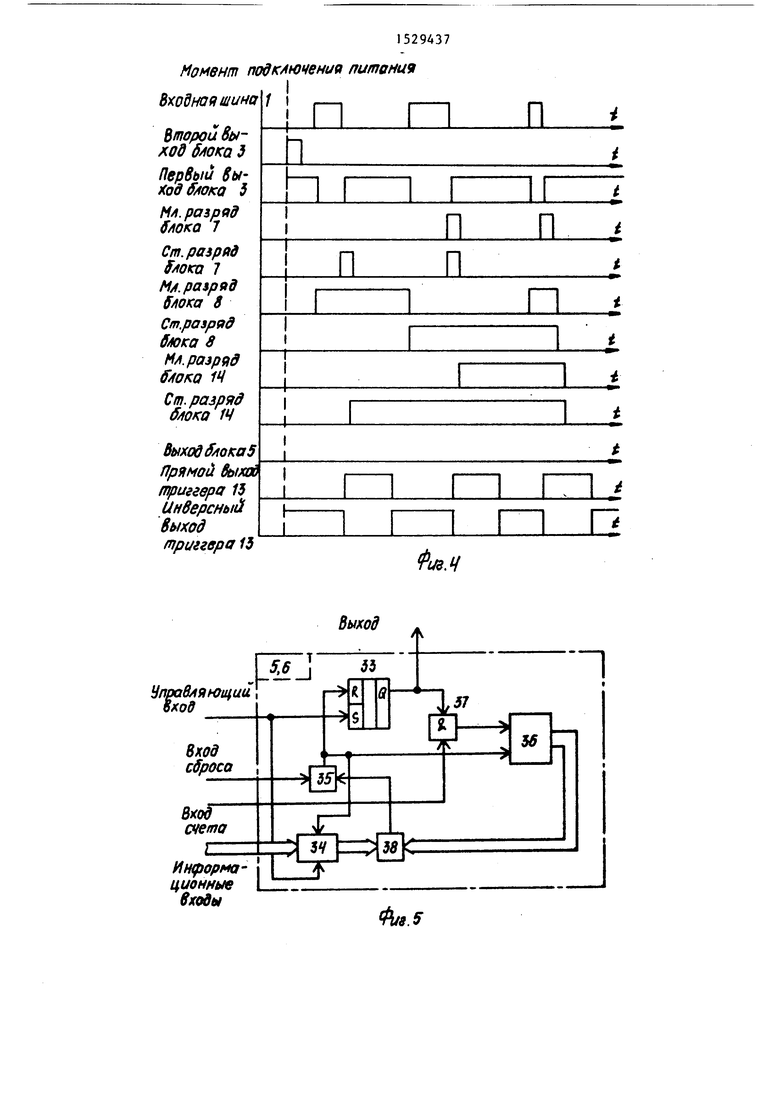

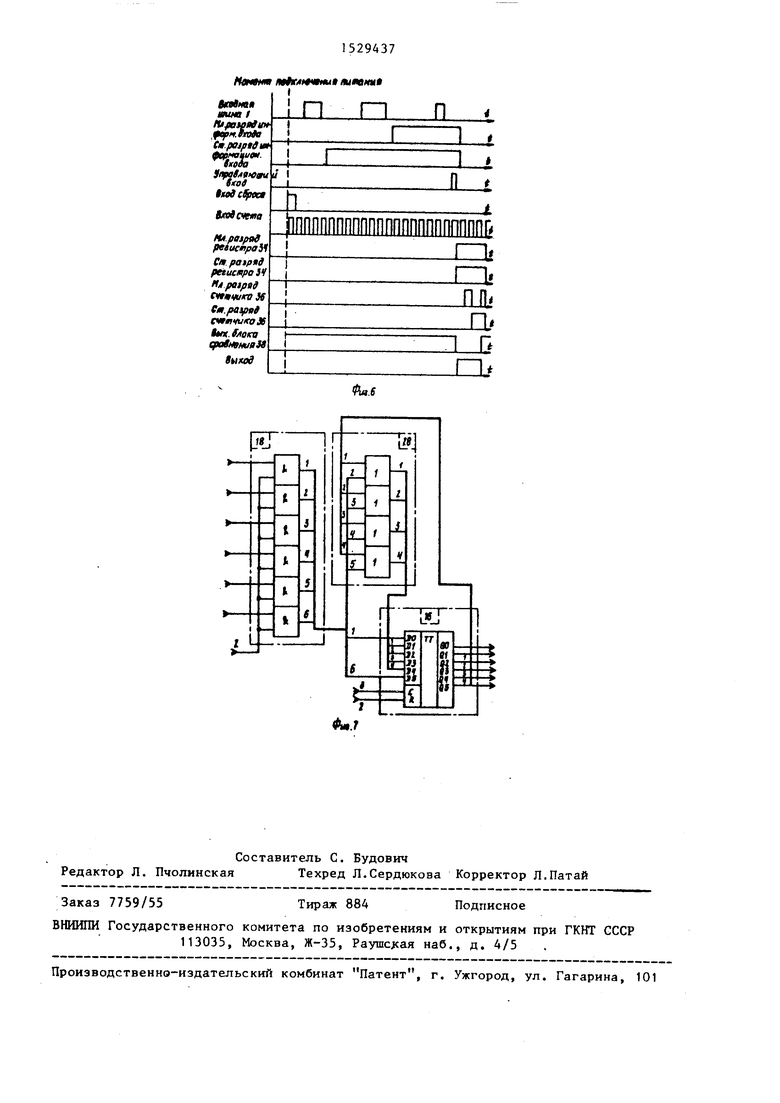

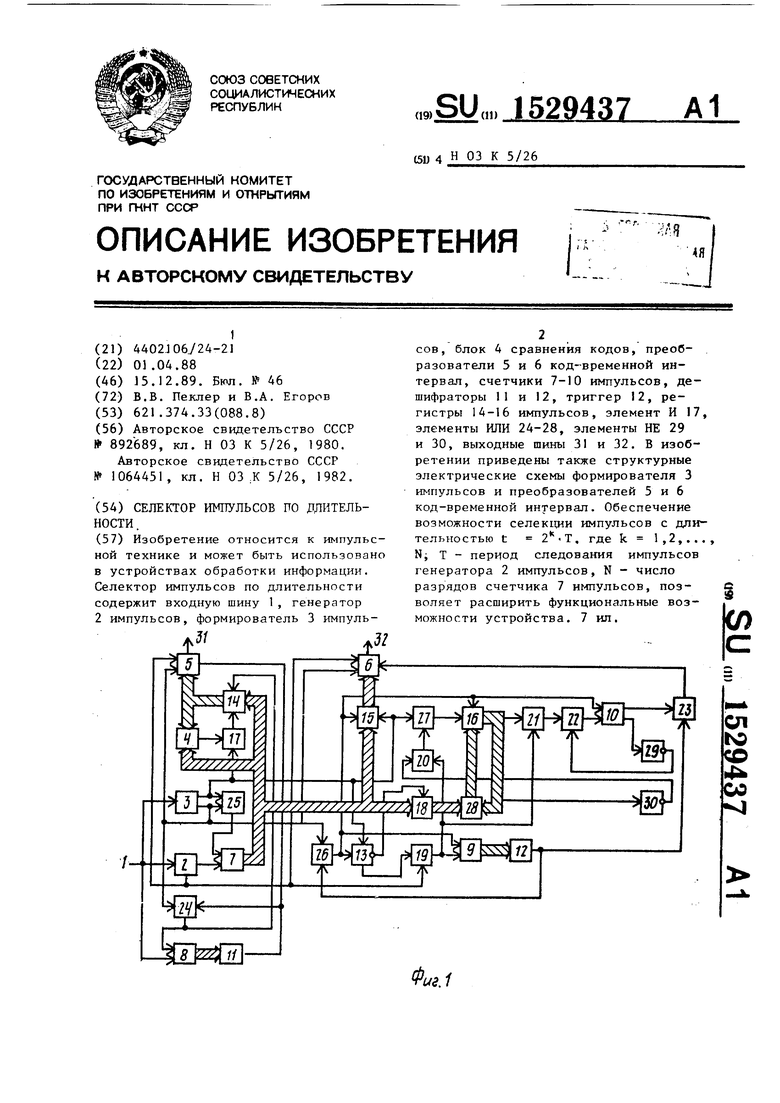

На фиг. 1 показана структурная электрическая схема устройства; на фиг. 2, А - временные диаграммы, поясняющие работу устройстваi на фиг.З схема формирователя импульсов, вариант; на фиг. 5 - схема преобразователя код-временной интервал, вариант; на фиг. 6 - временные диаграммы поясняющие работу преобразователя код-временной интервал; на фиг. 7 - структурная электрическая схема третьего регистра совместно с блоком ключей и пятым элементом ИЛИ, поясняющая структуру соединений, обеспечивающих требуемый сдвиг информации в регистре относительно его первого разряда.

Устройство содержит входную шину

1, генератор 2 импульсов, формирователь 3 импульсов, блок 4 сравнения кодов, первый 5 и второй б преобразователи код - временной интервал, первого по четвертый счётчики 7-10 импульсов, первый 11 и второй дешифраторы, триггер 13, с первого по третий регистры 14-16 памяти, первьй элемент И 17, блок 18 ключей, с второго по шестой элементы И 19-23, с первого по пятый элементы ИЛИ 24-28, первый 29 и второй 30 элементы НЕ, первую 31 и вторую 32 выходные шины. Шина 1 соединена со счетным входом счетчика 8, управляющим входом генератора 2 и входом формирователя 3, первый выход которого соединен с входом установки триггера 13, первыми входами элементов ИЛИ 25 и 27, входом записи регистра 15 и первым входом элемента И 17,второй вход которо - го соединен с выходом блока 4, а выход - с входом записи регистра 14, вход сброса которого соединен с выходом элемента ИЛИ 24 и входом сброса счетчика В, информационные входы поразрядно с выходами счетчика 7, вхдами первой группы входов блока 4, информационными входами ключа 18

0

5

0

5

0

5

0

5

0

5

и информационными входами регистра 15, а выходы - поразрядно с входами второй группы входов блока 4 и информационными входами преобразователя 5, управляющий вход которого соединен с вторым входом элемента ИЛИ 24 и выходом дешифратора 11, выход - с выходной шиной.31, вход счета - с вторым выходом генератора 2, входом счета преобразователя 6 и первым входом элемента И 19, а вход сброса - с вторым выходом формирователя 3, первыми входами элементов ИЛИ 24 и 26 и входом сброса преобразователя 6, выход которого соединен с шиной 32, управляющий вход - с выходом элемента И 23, а информационные входы - поразрядно с выходами регистра 15, вход сброса которого соединен с входами сброса счетчиков 9 и 10, регистра 16, триггера 13 и выходом элементна ИЛИ 26, второй вход которого соединен с выходом дешифратора 12 и первым входом элемента И 23, второй вход которого соединен с первым выходом счетчика 10, второй выход которого через элемент 29 НЕ соединен с первым входом элемента И 22, выход которого соединен со счетным входом счетчика 10, а второй вход - с выходом элемента И 21, второй вход которого соединен с выходом первого разряда регистра 16, а первый вход - с выходом элемента И 19, счетным входом счетчика 9 и первым входом элемента И 20, второй вход которого через элемент НЕ 30 соединен с выходом нулевого разряда регистра 16, а выход - с вторьтм входом элемента ИЛИ 27, выход которого соединен с входом записи регистра 16, информационные входы КОТОРОГО соединены поразряд- но с выходами элемента И 28, входы первой группы входов которого поразг рядно соединены с выходами ключа 18, а входы второй группы входов - поразрядно с выходами регистра 16, причем прямой выход триггера 13 соединен с вторым входом элемента И 19, инверсный выход - с управляющим входом ключа 18, выходы счетчика 9 поразрядно соединены с входами дешифратора 12, второй выход формирователя 3 соединен с вторым входом элемента 25 ИЛИ |Выход которого соединен с входом сброса счетчика 7, счетный вход которого соединен с первым выходом генератора 2, выходы счетчика 8 повходами дешифразрядно соединены ратора I.

Преобразователь код - временной интервал содержит триггер 33, вход установки которого соединен с управляющим входом преобразователя и входом записи регистра 34 памяти, вход сброса - с выходом элемента ИЛИ 35 и входами сброса регистра 34 и счетчика 36 импульсов, счетный вход которого соединен с выходом ключа 37, первый вход которого соединен с входом счета преобразователя второй вход - с выходом триггера 33 и выходом преобразователя, причем выходы регистра 34 поразрядно соединены с входами первой группы вхо- 1дов блока 38 сравнения, входы второй группы входов которого соединены поразрядно -с выходами счетчика 36, а выход - с вторым входом элемента ИЛИ 35, первый вход которого соединен с входом сброса преобразователя, причем информационные входы регистра 34 поразрядно соединены с информационными входами преобразователя ,

Устройство работает следующим образом.

При подключении источника питания на втором выходе формирователя 3 импульсов возникает импульс, устанав- ливаюп1ий преобразователи 5 и 6 код - временной интервал, счетчики 7-10 импульсов, триггер 13 и регистры 14- 16 в исходное (нулевое) состояние. В результате из-за равенства кодов на перьой и второй группах входов блока 4 сравнения кодов на его выходе уста найливается сигнал положительного уровня, включающий элемент И 17 и подключающий вход залиси регистра 14 к первому выходу формирователя 3 импульсов. Сигнал положительного уровня с инверсионного выхода триггера 13 включает блок 18 ключей и подключает информационный вход регистра 16 к выходам счетчика 7 импульсов. Элементы И 19, 21 и 23 находятся в состоянии О, элементы И 20, 22 - в состоянии 1, так как на их входах присутствуют сигналы положительного уровня. Устройство готово к селекции первого импульса серии. С его поступлением на входную шину 1 состояние счетчика 8 становится paaiaiM единице. Счетчик 7 и генерато р 2 импульсов преобразуют длительность импульса в пропорциональный код. Так как этот код больше нулевого кода, присутствующего на входах второй группы входов блока 4, изменений в схеме не происходит. При поступлении с первого выхода формирователя 3 импульса, создаваемого по окончании входного

импульса, происходит запись кода, соответствующего длительности первого импульса, в регистры 14-16, а также перебрасывание триггера 13. По этому же импульсу, но поступающему

через элемент ИПИ 25, счетчик 7 устанавливается в исходное состояние. В результате пропадает сигнал положительного уровня на выходе блока 4, выключается блок 18 ключей и включается элемент И 19. Поэтому вход записи регистра 14 отключается от первого выхода формирователя 3 и записанная в нем кодовая информация изолируется, на информационных входах

регистра 16 присутствует лишь поступающая через элемент ИЛИ - 28 информация с выходов этого регистра, первые входы элементов И 20 и 21, а таюге счетный вход счетчика 9 подключаются к второму выходу генератора 2 им

5

0

5

0

5

пульсов.. Если длительность входного импульса равна 2 Т (где k 1,2, 3,..., N; N - число разрядов счетчика 7; Т - период следования импульсов генератора 2), то в соответствующей кодовой информации независимо от значения k присутствует лишь одна единица в k-м разряде. Поэтому в нулевом разряде регистра 16 записан О и на входе элемента НЕ 30 присутствует сигнал нулевого уровня, обеспечивающий сигнал положительного уровня на втором входе элемента И 20. Этот элемент открыт и импульсы с второго выхода генератора 2 поступают . на вход записи регистра 16. Под действием этих импульсов происходит сдвиг информации в регистре 16, в результате чего 1 пробегает все разряды от k-ro (соответствующего первоначальному положению в коде) до первого разряда регистра. При нахождении в первом разряде регистра 16 эта 1 в форме сигнала положительного уровня включает элемент И 21 и пропускает только один импульс, так как по этому же импульсу происходит замещение данной единичной информации нулевой информацией из второго

разряда регистра через ранее включенный элемент И 22 на счетный вход счетчика 10, Состояние счетчика 10 становится равным единице и на его первом выходе устанавливается сигнал положительного уровня, включающий элемент И 23, подключая управляющий вход преобразователя 6 код - временной интервал к выходу дешифратора 12. Поскольку больше единиц в коде нет, такое состояние сохраняется до момента появления сигнала на выходе дешифратора 12, построение которого определяется предполагаемой разрядностью обрабатываемого кода, а следовательно и регистра 16. Этот сигнал осуществляет перезапись кодовой информации о длительности селектируемого импульса из регистра 15 во внутренний ре- гистр преобразователя 6, а также запуск последнего, в результате чего на выходе преобразователя 6 код - временной интервал формируется импульс, длительность которого равйа дЛитель- ности входного импульса, а именно 2-Т Кроме того, .сигнал с выхода дещ}1фра- тора 12, но прошедший через элемент ИЛИ 26, устанавливает триггер 13, счетчики 9 И 10 и регистры 15 и 16 в исходное состояние. Вследствие этого включаются элементы И 19, 21: и 23 и блок 18 ключей. При этом информационные входы регистра 16 подключаются вновь к выходам счетчика 7, уйравляю- ший вход преобразователя 6 отключается от выхода дешифратора 12, а вход записи регистра -16, счетньт вход счетчика 9 и первый вход элемента И 21 отключаются от второго выхода генера- тора 2. Устройство готово к селекции следующего импульса серии. Если же длительность первого импульса не равна 2, то это значит, что в коде, пропорциональном длительности этого импульса, присутствует либо одна единица в нулевом разряде, что соответствует импульсу единичной длительности, либо бопее чем одна единица. В первом случае это приводит к пропада- нию сигнала положительного уровня на выходе элемента НЕ 30, следствием чего является выключение элемента И 20 а значит отключение входа записи регистра 16 от второго выхода генера- тора 2. Поскольку элемент И 23 остается в выключенном состоянии, то при появлении- на выходе дешифратора 12 импульса, перезапись информации

Q 0 5 О Q д .

5

из регистра 15 в преобразователь 6 и его запуск не происходят, т.е. данный импульс не селектируется.Как и ранее, пройдя через элемент ИЛИ 23, импульс выхода дешифратора 12 устанавливает счетчики 2 и 10, триггер 13 и регистры 15 и 16 в исходное состояние, в результате чего, в частности, включается элемент И 20. Во втором случае, когда в коде, записанном в регистр 16, содержится более одной единицы, могут возникнуть следующие три ситуации. Единицы располагаются в нулевом и первом разрядах регистра. При этом, как и ранее, элемент И 20 выключается, а значит записанная в регистре 16 информация не подвергается сдвигу. Однако в результате наличия единицы в первом разряде регистра 16 элемент И 21 включается н пропускает импульсы на счетный вход счетчика 10. Так как сдвига информации в регистре 16 нет, на счетный вход счетчика 10 поступает более чем один импульс. Но после поступления на этот вход второго импульса на втором выходе счетчика 10 появляется сигнал положительного уровня, соответствующий состоянию дьа и выключающий элемент И 23, что прекращает дальнейшее поступление импульсов на счетчик 10, а значит предотвращает возможность последующего появления на первом выходе счетчика 10 сигнала положительного уровня, соответствующего нечетному состоянию счетчика, который может вызвать по импульсу с выхода дещифра- тора 12 селекцию такого входного импульса. Вторая ситуация соответствует наличию единиц в нулевом и каком-то еще разряде кода, но не первом. Этот случай полностью соответствует обработке импульса единичной длительности, рассмотренного ранее. При третьей ситуации единицы располагаются в любых разрядах кода, кроме нулевого. В этом случае производится сдвиг информации в регистре 16 и на счетный вход счетчика 10 поступают два импульса от генератора 2, по второму из них на втором выходе счетчика 10 устанавливается сигнал положительного уровня, который, будучи проинвертированным элементом НЕ 29, выключает элемент И 22 и предотвращает дальнейшую при наличии более чем двух един1П1 в кодовой информации работу счетчика 10. С поступлением с выхода дешифратора 12 импульса в схеме происходят изменения, подготавливающие устройство к обработке следующего импульса серии С приходом этого импульса состояние счетчика 8 увеличивается на единицу (равно теперь двум), а длительность импульса преобразуется в пропорциональный код, записывает-ОзШ счетчиком 7. Если длительность второго импульса меньше длительности первого импульса, состояние схемы сохраняется и с поступлением импульса с первого выхода формирователя 3 код, соответствующий длительности второго импульса, записывается лИшь в регистры 15 и 16, а в регистре 14 сохраняется информация о длительности первого импульса. Счетчик 7 устанавливается в исходное (нулевое) состояние, а работа устройства по определению характера кодовой информации на соответствие 2-Т аналогична описанной при освещении обработки первого импульса серии.Если длительность второго импульса больше дпительности первого импульса, на выходе блока 4 устанавливается сиг нал положительного уровня, включающий элемент И 17 и подсоединяющий вход записи регистра 14 к второму выходу генератора 2. С поступлением импульса записи информация о длительности второго импульса записывается в регистры 14-16. Работа схемы по селекции и myльcoв с длительностью равной 2 Т, аналогична описанной. Итак, с поступлением каждого нового импульса состояние счетчика 8 увеличивается на единицу, а длительность импульса преобразуется в пропорциональный код, записываемый в счетч1 Ке . При сравнении бло1 ом 4 полученного кодз с кодом, ранее записанным в регистре 14, принимается решение о тог-;, надо фиксировать новый код или нет. При решении на запись по импульсу от формирователя 3, создающего импульс по окончании входного импульса, код записывается в регистр 14, а также в рег1;стры 15 и 16. Регистр 15 предназначен для хранения информации о длительности текущего импульса, а в регистре 16 производится сдв-иг информации относительно первого разряда, что обеспечивает подсчет счетчиком

15

20

2943710

10 количества единиц, содержащихся в коде, и принятие решения о том, равна длительность импульса 2-Т или нет, т.е. о целесообразности селекции этого импульса. При положительном решении кодовая информация из регистра 15 перепнсыьается во внутренний регистр преобразователя 6, 10 код - временной интервал, который на своем выходе воспроизводит импульс, идентичный по длительности входному. Затем в схеме происходят процессы очистки регистров 15 и 16 и переключения соответствующих элементов И, подготавливающие устройство к работе со следующим входным импульсом анализируемой серии. Информация в регистре 14 сохраняется.Этот процесс протекает до момента формирования дешифратором 11 сигнала об окончании серии входных импульсов. .По этому сигналу преобразователь 5 осуществляет преобразование кода,записанного в регистре I4 после окончания последнего импульса серии, во временной интервал, тем самым воспроизводится соответствующий этому

коду импульс, максимальный по длиI

тельности в серии. По этому же сигналу с дешифратора 11, но прошедшему через элемент ИЛИ 24, регистр 14 и счетчик 8 устанавливаются в исходное состояние. Остальные элементы схемы

были установлены в исходное состояние несколько ранее по сигналу с дешифратора 12, прошедшему через элемент ИЛИ 26. Устройство готово к обработке новой серии входных импульсов. Таким образом, реализованный в селекторе принцип сдвига кодовой информации о длительности входного импульса относительно первого разря., да .регистра, управляющего подачей импульсов на счетное устройство, обеспечивает выбор из серии импульсов наряду с импульсом максимальной

30

40

длительности импульсов, длительность которых равна 2 Т. Временные диаграммы, поясняющие работу селектора импульсов по длительности, даны на фиг.2. Для упрощения рассмотрен двухразрядный вариант (нулевой или первый разряды), а также серия входных импульсов, состоящая только из двух импульсов. На фиг. 7 представлена структурная электрическая схема блока 16 с блоками 18 и 28, поясняющая структуру соединений, обеснечи- ваюпшх требуемый сдвиг информации в регистре 16 относительно его червого разряда.

Принцип работы формирователя 3 импульсов состоит в создании импульсов для принудительного обнуления при подключении питания блоков 5-10, 13-16, а таже для формирования импульсов записи информации в регистры 14-16, изменения состояния триггера 13 и периодической установки счетчика 7 в исходное состояние. Указанные функции выполняются формирователем 3 следующим образом. Дан- Hbrii блок формирует импульс сброса для всех перечисленных блоков в момент подключения питания. Создание импульса записи информации в регистры 1 А-16, изменения состояния триггера 13 и периодического обнуления счетчика 7 осуществляется по спаду входного импульса. В качестве такой схемы использован инвертор. Принцип работы преобразователя код - временной интервал (фиг.5, 6) заключается в следующем.

При подключении источника питания импульс сброса от формирователя 3 поступает на вход сброса и устанавливает в исходное (нулевое) состояние триггер 33, счетчик 36 импульсов и регистр 34 памяти. В результате этого на выходе преобразователя устанавливается нулевой уровень, запирающий элемент И 37 и отключающий счетный вход генератора .2 импульсов Информационные входы регистра 34 через информационные входы преобразователя подключены к выходам соответствующего регистра селектора.Поэтому на этих входах присутствует ко записанный в регистре селектора. Выходы регистра 34 подключены к входам первой группы входов блока 38 сравнения, подключенного входами второй группы входов к выходам счетчика 36 При поступлении на управляющий вход преобразователя сигнала от соответствующего дещифратора происходит запись кодовой информации из регистра селектора в регистр 34 и переключение триггера 33 в единичное состояние, соответствующее формированию переднего фронта выходного импульса В результате этого, счетный вход счетчика 36 импульсов оказывается подключенным к второму выходу генед,

2943712

ратора 2 и счетчик 36 начинает подсчет поступающих импульсов. Необходимость снятия импульсов со второго выхода генератора 2, а не с его первого выхода, обьясняется особенностью построения генератора 2, состоящего из собственно генератора импульсов и ключа, управляемого входным Q импульсом (только в его присутствии на первом выходе генератора 2 есть импульсы). Второй выход генератора 2 подключен непосредственно к генератору и на нем импульсы имеются 5 всегда, независимо от состояния

входной шины 1. Результат подсчета сравнивается блоком 38 сравнения с кодом, записанным в регистре 34. В момент их равенства на выходе блока 20 38 сравнения появляется сигнал положительного уровня, устанавливающий в исходное (нулевое) состояние регистр 34, счетчик 36 импульсов и триггер 33, формируя задний фронт 25 выходного импульса. При использовании для формирования длительности выходного импульса того же генератора, что и при преобразовании длительности входного импульса в код, 30 обеспечивается равенство длительностей выходного и соответствующего ему входного импульсов.

Предлагаемое устройство обеспечивает выделение из серии импульсов максимального по длительности импульса, что обеспечивается путем записи кода, пропорционального длительности выделенного импульса, в регистр устройства с последующим повторением импульса с помощью преобразователя код - временной интервал.

По сравнению с прототипом селектор производит выделение всех импульсов серии с длительностью, равной 2-Т. 45 Это достигается путем записи кода в соответствующий регистр и последующим его анализом при сдвиге информации относительно первого разрядэ регистра с подсчетом количества содер- 50 жащихся в коде единиц.

Таким образом, селектор импульсов по длительности обеспечивает получение дополнительной информации о серии входных импульсов.

35

40

55

Ф о

р м у л

изобретения

Селектор импульсовпо длительности, содержащий генератор импульсов, пер-

вый выход которого соединен со счетным входом первого счетчика импульсов, а управляющий вход - с входной шиной, входом формирователя импульсов и счетным входом второго счетчика импульсов, выходы которого поразрядно соединены с входами первого депЕифратора, выход которого соединен

мационными входами второго регистра, а вход записи - с выходом первого элемента И, второй вход которого соединен с выходом блока сравнения кодов, причем выход третьего элемента ИЛИ соединен с входами сброса триггера, третьего и четвертого счетчиков импульсов, второго и третьего регист

| название | год | авторы | номер документа |

|---|---|---|---|

| Селектор импульсов по длительности | 1988 |

|

SU1647876A1 |

| Устройство селекции импульсов по длительности | 1990 |

|

SU1758863A1 |

| Селектор импульсов по длительности | 1986 |

|

SU1422383A1 |

| Селектор импульсов по длительности | 1989 |

|

SU1688399A1 |

| Пересчетное устройство | 1980 |

|

SU921093A1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1993 |

|

RU2042183C1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 2013 |

|

RU2534971C1 |

| Комбинированное устройство временной задержки и формирования импульсов | 1987 |

|

SU1443151A1 |

| АДАПТИВНЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1991 |

|

RU2043648C1 |

| Фазометр мгновенных значений | 1981 |

|

SU980015A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах обработки информации. Селектор импульсов по длительности содержит входную шину 1, генератор 2 импульсов, формирователь 3 импульсов, блок 4 сравнения кодов, преобразователи 5 и 6 код-временной интервал, счетчики 7-10 импульсов, дешифраторы 11 и 12, триггер 13, регистры 14-16 импульсов, элемент И 17, элементы ИЛИ 24-28, элементы НЕ 29 и 30, выходные шины 31 и 32. В изобретении приведены также структурные электрические схемы формирователя 3 импульсов и преобразователей 5 и 6 код-временной интервал. Обеспечение возможности селекции импульсов с длительностью T=2K.T, где K=1,2,..., N, T - период следования импульсов генератора 2 импульсов, N-число разрядов счетчика 7 импульсов, позволяет расширить функциональные возможности устройства. 7 ил.

с управляющим входом первого преобра- Q ров памяти, а второй вход - с первым

ции импульсов , где k 1,2,,

зователя код - временной интервал, вьгход которого соединен с первой выходной шиной, а также блок сравнения кодов, входы пер(зой группы входов которого поразрядно соедине1ты с выходами первого счетчика импульсов, а также первый регистр памяти, отличающийся тем, что, с целью расширения функциональных возможностей за счет обеспечения селек- с длительностью t

N, Т период следования 1{мпульсов генератора импульсов, F - число разрядов первого счетчика импульсов, в него введены с первого по пятый элементы ИЛИ, с первого по шестой элементы И, второй и третий регистры памяти, третий и четвертый счетчики импульсов, первый и второй элементы НЕ, триггер, второй дешифратор, второй преобразователь код - временной интервал, блок ключей и вторая выходная шина, причем первый выход формирователя импульсов соединен с первыми входами первого элемента Р1 и второго элемента ИЛИ, установочным входом триггера, первым входом четвертого элемента ИЛИ и входом записи второго регистра, а второй вы- ход - с входами сброса первого и второго преобразователей код - временной интервал, вторым входом второго элемента ИЛИ и первыми входами первого и третьего элементов ИЛИ, при- чем второй вход первого элемента ИЛИ соединен с выходом первого дешифратора, а выход - с входами сброса второго счетчика импульсов и первого регистра памяти, выходы которого пораз- рядно соединены с информационными входами первого преобразователя код - временной интервал и также поразрядно с входами второй группы входов блока срав}1ения кодов, информационные входы поразрядно - с выходами первого счетчика импульсов, с информационными входами блока ключей и с инфор5

0

5 0

входом шестого элемента И и выходом второго дешифратора, входы которого поразрядно соединены с выходами третьего счетчика импульсов, счетный вход которого соединен с первыми входами третьего и четвертого элементов И и выходом второго элемента И, первый вход которого соединен с вторым выходом генератора импульсов и входами счета первого и второго преобразователей код - временной интервал, а второй вход - с прямым выходом триггера, инверсный выход которого соединен с управляющим входом блока ключей, выходы которого поразрядно соединены с входами первой группы входов пятого элемента ИЛИ, выходы которого поразрядно соединены с информационными входами третьего регистра памяти, вход записи которого соединен с выходом четвертого элемента ИЛИ,ВЬгходы поразрядно - с входами второй группы входов пятого элемента ИЛИ, а выход нулевого разряда через второй элемент НЕ - с вторьп входом третьего элемента И, выход которого соединен с вторым входом четвертого элементов ИЛИ, причем выходы второго регистра памяти поразрядно соединены с информационными входами второго преобразователя код - временной интервал, выход которого соединен с второй выходной шиной, а управляющий вход - с выходом шестого элемента И, второй вход которого соединен с первым выходом четвертого счетчика импульсов, второй выход которого соединен через первый элемент НЕ с первым входом пятого элемента И, выход которого соединен со счетным входом четвертого счетчика импульсов, а второй вход - с выходом четвертого элемента И, второй вход которого соединен с выходом первого разряда третьего регистра памяти, причем выход второго элемента ИЛИ соединен с входом сброса первого счетчика импульсов.

Фиг.

MoMeHHJ подк ечени9 питани9

Выход

Фиг.У

HtMtm аитвмы

Составитель С. Будович Редактор Л. Пчолинская Техред Л.Сердюкова Корректор Л.Патай

Заказ 7759/55

Тираж 884

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Payшc «aя наб., д. 4/5

Производственно-издательский комбинат Патент, г, Ужгород, ул. Гагарина, 101

Подписное

| Селектор импульсов по длительности | 1980 |

|

SU892689A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Селектор импульсов по длительности | 1982 |

|

SU1064451A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-12-15—Публикация

1988-04-01—Подача