Изобретение относится к импульсной технике, может быть использовано в устройствах обработки информации.

Цель изобретения - обеспечение возможности выделения импульсов, максимальных по длительности, в парах соответствующих импульсов первой и третьей групп импульсов, а также второй и четвертой групп импульсов входной импульсной последовательности, содержащей N 2м импульсов, где М 2, причем первая группа импульсов образована с первого по 2 -й импульсами входной импульсной последовательности, вторая группа - с (2 + +1)-го по 2(ми)-й, третья группа - с (2(м

+1)-го по(2.м-2(м 2)-й, четвертая группа-с (2м-2()-го по 2м-й при одновременном обеспечении возможности распределения выделенных импульсов по выходным шинам в зависимости от результатов сравнения.

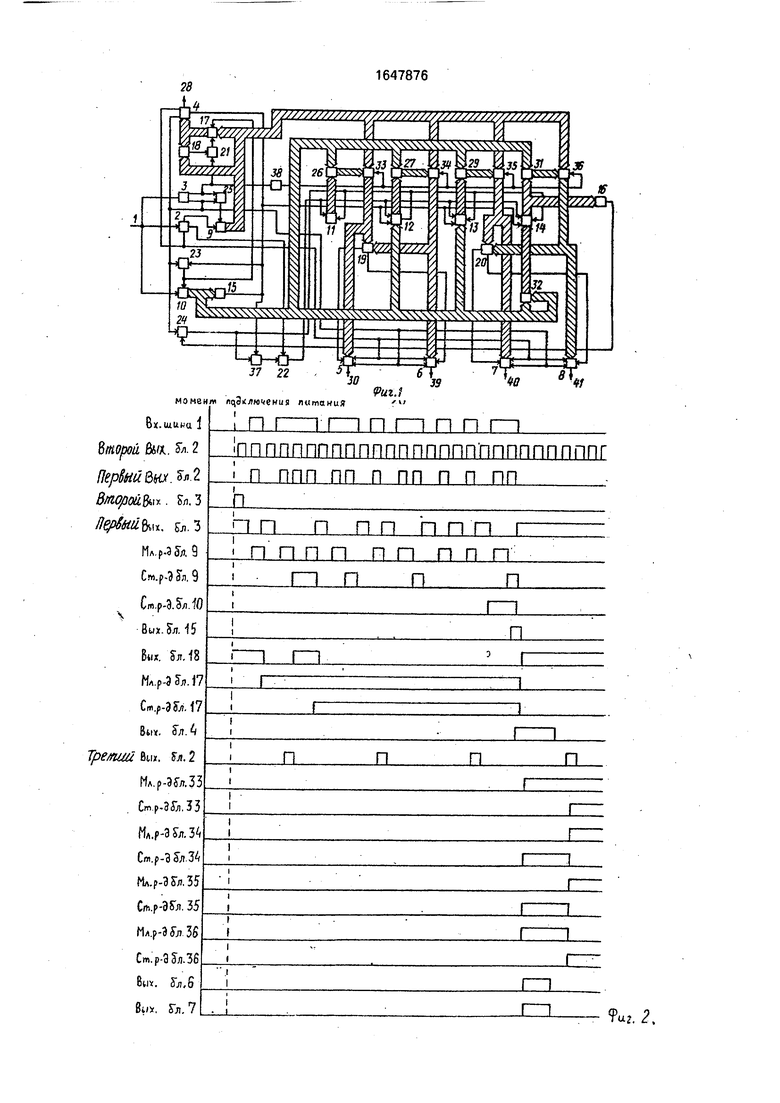

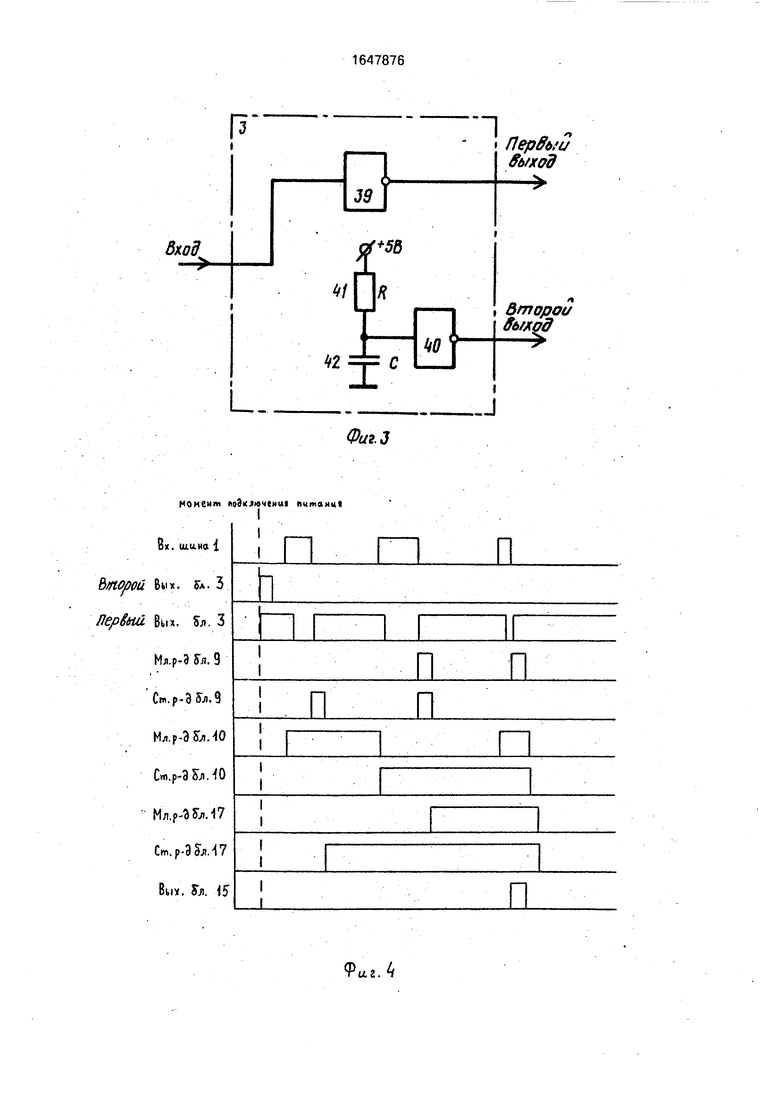

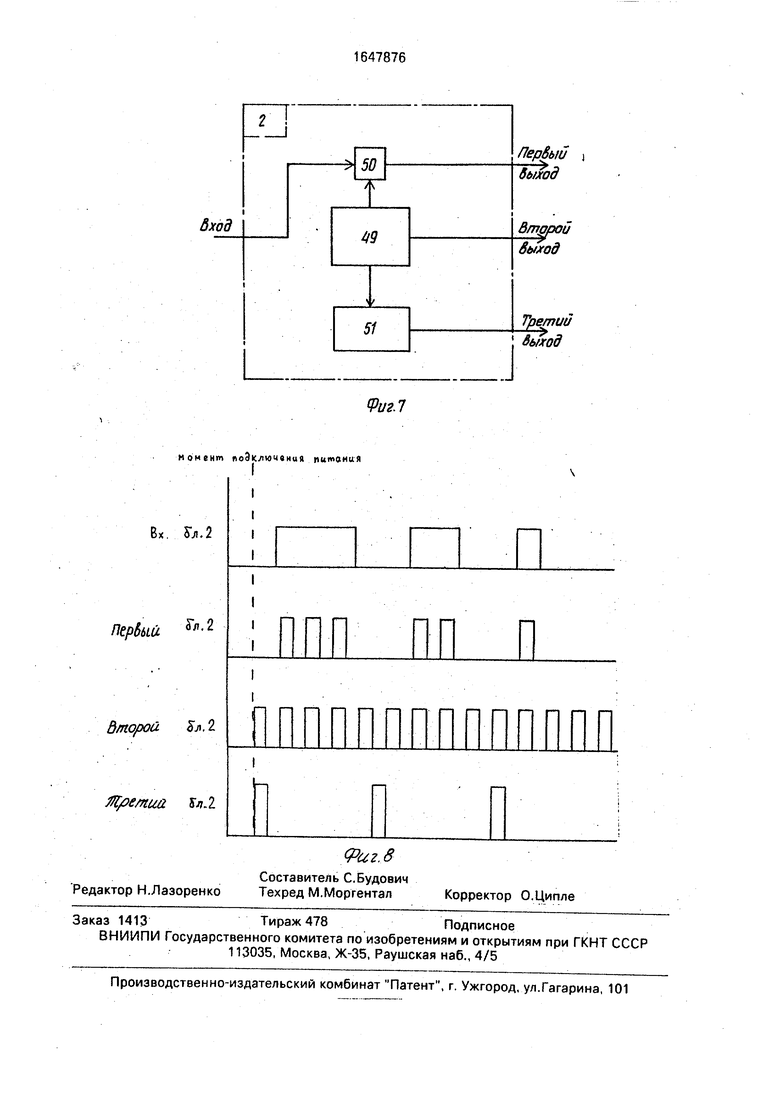

На фиг. 1 показана структурная электрическая схема устройства; на фиг.2 - временные диаграммы, поясняющие работу устройства; на фиг.З - структурная электрическая схема формирователя импульсов; на фиг.4 - временные диаграммы, поясняющие работу формирователя импульсов в зависимости со счетчиками; на фиг. 5 - структурная электрическая схема преобразователей код-временной интервал; на фиг.6 - вреО Јь Ч 00

VI сь

менные диаграммы, поясняющие работу преобразователя код-временной интервал; на фиг.7 - структурная электрическая схема генератора импульсов; на фиг.8 - временные диаграммы, поясняющие работу генератора импульсов.

Селектор импульсов на длительности содержит входную шину 1, которая соединена с входами генератора 2 импульсов и формирователя 3 импульсов, первый преобразователь 4 код-временной интервал, счетный вход которого соединен со счетными входами с второго по пятый преобразователей 5-8 код-временной интервал, Первый выход генератора 2 соединен со счетным входом первого счетчика 9 импульсов, шина 1 - со счетным входом второго счетчика 10 импульсов, счетный вход третьего счетчика 11 импульсов - со счетными входами с четвертого по шестой счетчиков 12-14 импульсов. Выходы счетчика 10 поразрядно соединены со входами первого дешифратора 15, выходы счетчика 14 - со входами второго дешифратора 16. Выходы счетчика 9 поразрядно соединены с инфор мационными входами регистра 17 памяти и с входами первой группы входов первого блока 18 сравнения кодов, управляющие входы преобразователей 5 и 6 - соответственно с первым и вторым выходами второго блока 19 сравнения кодов, управляющие входы преобразователей 7 и 8 - соответственно с первым и вторым выходами третьего блока 20 сравнения кодов. Первый выход формирователя 3 соединен с первым входом первого элемента И 21, второй выход генератора 2 - со счетным входом преобразователя 4, а третий выход - с вторым входом второго элемента И 22. Второй выход формирователя 3 соединен со входами сброса преобразователей 4-8, первыми входами первого и второго элементов ИЛИ 23 и 24, первый и второй выходы формирователя 3 соединены соответственно с первым и вторым входами третьего элемента ИЛИ 25. Выходы счетчика 10 поразрядно соединены со входами первых групп входов четвертого и пятого элементов ИЛИ 26 и 27. Выход преобразователя 4 соединен с первой выходной шиной 28, выходы счетчика 10 поразрядно соединены со входами первой группы входов шестого элемента ИЛИ 29, выход преобразователя 5 соединен с второй выходной шиной 30.

Выходы счетчика 10 поразрядно соединены с входами первой группы входов седьмого элемента ИЛИ 31 (М + 1)-й информационный вход счетчика 12, (М+1}-й и М-й информационные входы счетчика 13, (М+1)-й вход первой и группы входов

(М+1)-й и М-й входы второй группы входов восьмого элемента ИЛИ 32 соединены с общей шиной, с М-го по первый информационные входы счетчика 12 и с М-го по первый

входы первой группы входов элемента ИЛИ 32 соединены соответственно с (М+1)-го по второй выходами счетчика 10, с (М-1)-го по первый информационные входы счетчика 13 и с (М-1)-го по первый входы второй группы

0 входов элемента ИЛИ 32 соединены соответственно с (М+1)-го по третий выходами счетчика 10. Выходы счетчика 9 поразрядно соединены с информационными входами с первого по четвертый запоминающих бло5 ков 33-36. Выход элемента ИЛИ 24 соединен со входом сброса триггера 37, первый выход формирователя 3 соединен со входом элемента НЕ 38. Выходы преобразователей 6-8 соединены соответственно с третьей

0 по пятую выходными шинами 39-41. Выход блока 18 соединен с вторым входом элемента И 21, выход которого соединен с входом записи регистра 17, выходы которого поразрядно соединены с входами второй группы

5 входов блока 18 и информационными входами преобразователя 4, а вход сброса соединен с входом сброса счетчика 10 и выходом элемента ИЛИ 23, второй вход которого соединен с выходом дешифратора 15, управ0 ляющим входом преобразователя 4, установочными входами счетчиков 12-14 и входом установки триггера 37, выход которого соединен с первым входом элемента 22, выход которого соединен со счетным

5 входом счетчика 11. Выход элемента ИЛИ 25 соединен с входом сброса счетчика 9, второй вход элемента ИЛИ 24 соединен с выходом дешифратора 16, а выход - с входами сброса счетчиков 11-14, выходы кото0 рых поразрядно соединены с входами вторых групп входов соответственно элементов ИЛ И 26 и 27,29 и31, выходы которых поразрядно соединены с адресными входами блоков 33-36, управляющие входы кото5 рых соединены с выходом элемента НЕ 38. Выходы блока 33 поразрядно соединены с информационными входами преобразователя 5 и входами первой группы входов блока 19, выходы блока 34 - поразрядно с

0 информационными входами преобразователя 6 и входами второй группы входов блока 19, выходы блока 35 - поразрядно с информационными входами преобразователя 6 и входами первой группы входов бло5 ка 20, выходы блока 36 - поразрядно с информационными входами преобразователя 8 и входами второй группы входов блока 20. Выходы элемента ИЛИ 32 поразрядно соединены с информационными входами счетчика 14,

На фиг.2 цифрами обозначены сигналы на выходах соответствующих элементов и шинах.

Формирователь 3 импульсов содержит два инвертора 39,40, резистор 41 и конденсатор 42, соединенные между собой в соответствии с фиг.З.

Преобразователи 4-8 содержат триггер 43, ключ 44, счетчик импульсов 45, элемент ИЛИ 46, регистр 47, элемент 48 сравнения, соединенные между собой в соответствии с фиг.5.

Селектор импульсов по длительности работает следующим образом.

При подключении источника питания на втором выходе формирователя 3 импульсов возникает импульс, устанавливающий преобразователи 4-8, счетчики 9-14 импульсов, регистр 17 и триггер 37 в исходное (нулевое) состояние. В результате, из-за равенства кодов на входах групп входов блока 18 сравнения кодов на его выходе устанавливается сигнал уровня.логической 1, подключающий вход записи регистра 17 к первому выходу формирователя 3 импульсов; отсутствие сигнала уровня логической 1 на выходе триггера 37 отключает счетные входы счетчиков 11-14 от третьего выхода генератора 2 импульсов; наличие сигнала уровня логической 1 на выходе элемента 38 обеспечивает режим считывания запоминающих блоков 33-36, а их исполнение дает при этом нулевую информацию на их выходах, вследствие чего сигналы уровня логической 1 на выходах блоков 19 и 20 сравнения кодов отсутствуют. Селектор готов к селекции первого импульса серии. С его поступлением на входную шину 1 состояние счетчика 10 становится равным 1, а совокупность счетчика 9 и генератора 2 импульсов преобразует длительность импульса в пропорциональный код. Так как этот код больше нулевого кода, присутствующего на входе второй группы входов формирователя блока 18, изменения в схеме не происходит. При поступлении с первого выхода формирователя 3 импульса, формируемого по окончании входного импульса, происходит запись кода, соответствующего длительности первого импульса, во-первых, в регистр 17, а во-вторых, вследствие пропадания на время действия этого импульса сигнала уровня логической 1 на выходе элемента 38, а значит перехода запоминающих блоков 33-36 в режим записи, в эти запоминающие блоки по адресу, определяемому состоянием счетчика 10, т.е. по адресу 1. По этому же импульсу, но поступающему через элемент ИЛИ 25, счетчик 9 устанавливается в исходное состояние. В результате, пропадает сигнал уровня логической 1 на выходе блока 18. Поэтому вход записи регистра 17 отключается от первого выхода формирователя 3 5 и записанная в нем кодовая информация изолируется. По окончании действия импульса на выходе элемента 38 устанавливается вновь сигнал уровня логической 1 переводящий запоминающие блоки 33-36 в

0 режим считывания, изолируя записанную в них информацию. Эта кодовая информация поступает на их выходы, а значит, и на группы входов блоков 19 и 20. Так как эти коды равные, на выходах блоков 19 и 20

5 сигналы уровня логической 1 не появляются. Устройство готово к селекции следующего импульса серии. С его приходом состояние счетчика 10 увеличивается на единицу (равно теперь двум), а длитель0 ность импульса преобразуется в пропорциональный код, записываемый счетчиком 9. Если длительность второго импульса меньше длительности первого импульса, состояние устройства сохраняется и с

5 поступлением импульса с первого выхода формирователя 3 код, соответствующий длительности второго импульса, записывается лишь в запоминающие блоки 33-36, а в регистре 17 сохраняется информация о

0 длительности первого импульса. Счетчик 9 устанавливается в исходное (нулевое) состояние и устройство готово к селекции третьего импульса серии. Если длительность второго импульса больше длительности

5 первого импульса, на выходе блока 18 устанавливается сигнал уровня логической 1, подключающий вход записи регистра 17 к первому выходу формирователя 3. Поэтому с поступлением импульса записи информа0 ция, помимо запоминающих блоков 33-36 записывается и в регистр 17. После этого в устройстве происходят изменения, изолирующие информацию в отмеченных блоках, причем в запоминающих блоках 33-36 она

5 располагается по адресу 2 (состояние счетчика 10). Итак, с поступлением каждого нового импульса состояние счетчика 10 увеличивается на 1, формируя адрес записи для блоков 33-36, а длительность импульса

0 преобразуется в пропорциональный код, записываемый в счетчике 9. По сравнении в блоке 18 полученного кода с кодом, ранее записанным в регистре 17, принимается решение о том, надо фиксировать новый код,

5 или нет. При решении на запись, по импульсу от формирователя 3, формирующего импульс по окончании входного импульса, код записывается в регистр 17, а также в запоминающие блоки 33-36. В противном случае запись информации о длительности

входного импульса производится лишь в блоки 33-36. Этот процесс протекает до момента формирования дешифратором 15 сигнала об окончании серии входных импульсов. По этому сигналу преобразователь 4 осуществляет преобразование «.ода, записанного в регистре 17 после окончания последнего импульса серии, во временной интервал, тем самым воспроизводится соответствующий этому коду импульс, максимальный по длительности в серии.

Для обеспечения попарного сравнения импульсов в группах по длительности необходимо первоначально сформировать исходные адреса, в которые следует установить счетчики 11-14. Такими адресами являются номера импульсов, последних в предшествующей, по отношению к данной, четверти. Например, для N 2 8 такими адресами будут следующие номера: О для первой группы, 2 для второй группы, 4 для третьей группы и 6 для четвертой группы. В двоичном представлении это будут числа 0, 21, 22 и 21 2 . Проведя обобщение на весь рассматриваемый спектр возможных серий длины N 2 , получаем следующие начальные адреса: первая - 0, вторая - , третья - 2k четвертая - . Данные адреса записываются как исходные в соответствующие счетчики 11-14 и представляют каждый для своей группы нулевую границу,

Кроме этого, по сигналу с дешифратора 15 триггер 37 устанавливается в единичное состояние, подключая тем самым счетные входы счетчиков 11-14 к третьему выходу генератора 2 импульсов. По этому же сигналу с дешифратора 15, прошедшему через элемент ИЛИ 23, регистр 17 и счет«ик 10 устанавливаются в исходное состояние. Селектор приступает к осуществлению второй части своей работы. Заведение связей со счетчика 10 и построение элемента 32 ИЛИ обеспечивает формирование начальных адресов групп импульсов По этим адресам импульсы считываются в блоки 19 и 20 соответственно и по результату сравнения принимается сигнал о том, какой импульс из пары сравниваемых подлежит селекции. Так, если код, соответствующий длительно- , ста первого импульса первой группы, считы- ваемый из блока 33, больше кода длительности первого импульса третьей группы, поступающего из блока 34, то на первом выходе блока 19 появляется сигнал, поступающий на управляющий вход преобразователя 5, и восстановлению подлежит первый импульс в первой группе, т.е. больший в первой паре сравнения. В противном случае появляется сигнал на втором выходе

блока 19, запускающий преобразователь 6, а значит восстановлению подлежит первый импульс в третьей группе, опять же больший по длительности в первой паре сравниваемых соответствующих кодов. Если же оказывается, что сравниваемые коды равны, восстановления не происходит. Аналогичные процессы происходят и в блоке 20, где сравниваются коды, поступающие из бло0 ков 35 и 36, т.е соответствующие импульсам второй и четвертой групп. По окончании восстановления импульсов преобразователями 5-8 на счетные входы счетчиков 11-14 поступает импульс с третьего выхода генера5 тора 2; период этих импульсов выбран сообразно максимально возможной длительности импульса во входной последовательности. Состояние счетчиков 11-14 увеличивается на единицу, т.е. соответству0 ет номерам вторых импульсов в каждой из групп. И так далее, до установления в счетчике 14 адреса, соответствующего последнему импульсу в серии. При этом на сравнение поставлены коды, соответствую5 щие длительности импульсов, последних в группах. По результатам сравнения принимаются решения на селекцию, а дешифратор 16 формирует сигнал, устанавливающий триггер 37 и счетчики 11-14 в исходное со0 стояние. Селектор готов к обработке новой серии входных импульсов. Таким образом, реализованный в селекторе принцип идентичной записи кодовой информации о длительностях всех импульсов серии в четыре

5 запоминающих блока с последующих их считыванием по адресам, соответствующим группам с целью сравнения между собой импульсов первой, третьей и второй, четвертой групп, позволяет производить селекцию

0 импульсов серии, наибольших в указанных парах сравнения, что производится наряду с селекцией импульса максимальной длительности в серии импульсов. Временные диаграммы, поясняющие работу селектора

5 импульсов по длительности, даны на фиг.2. Для упрощения графического представления рассмотрен двухразрядный вариант (нулевой и первый разряды), а также серия входных импульсов, состоящая только из N

50 импульсов,

Принцип работы формирователя 3 импульсов состоит в следующем. Данный блок формирует импульсы для осуществления принудительного обнуления при подключе55 нии питания блоков 4-14, 17и 37, а также для формирования импульсов записи информации в регистр 17 и запоминающие блоки 33-36 и периодической установки счетчика 10 в исходное состояние. Указанные Функции выполняются блоком 3 следующим образом. Данный блок формирует импульс сброса( второй выход) для перечисленных блоков а момент подключения питания. Формирование импульса записи информации в регистр 17 и заполняющие блоки 33-36, (для периодического обнуления счетчика 9) осуществляется по спаду входного импульса. Для этого использован триггер с заведением цепи обратной связи на вход сброса (первый выход) формирователя 3 импульсов (представлена на фиг.З). Временные диаграммы, поясняющие работу блока 3, даны на фиг.4.

Принцип работы преобразователя код- временной интервал заключается в следующем. При подключении источника питания импульс сброса от блока 3 поступает на вход сброса и устанавливает в исходное (нулевое) состояние триггер, счетчик импульсов и регистр хранения кода. В результате этого на выходе преобразователя устанавливается нулевой уровень, соответствующий отсутствию импульса на выходе и отключающий вход счетчика импульсов от счетного входа преобразователя, т.е. от второго выхода генератора 2 импульсов. Вход регистра хранения кода через информационные входы преобразователя подключен к выходу соответствующего блока селектора (регистра, запоминающего устройства). Поэтому на этих входах присутствует код, записанный в отмеченных блоках. Выход регистра хранения кода подключен к первому входу элемента сравнения, подключенного вторым входом к выходу счетчика. При поступлении на управляющий вход преобразователя сигнала управления происходит запись кодовой информации из регистра селектора в регистр хранения и переключения триггера в единичное состояние, соответствующее формированию переднего фронта выходного импульса. В результате этого счетный вход счетчика импульсов подключается к второму выходу генератора 2 и счетчик производит подсчет поступающих импульсов. Необходимость снятия импульсов с второго выхода генератора 2, а не с его первого выхода, объясняется особенностью внутреннего построения генератора 2, состоящего (фиг.7) из собственно генератора 49 и элемент 50 И, управляемого входным импульсом (только при его присутствии на первом выходе блока 2 есть импульсы) и делителя 51 частоты, второй выход генератора 2 подключен непосредственно к генератору, и на нем, при работающем генерь оре, импульсы будут всегда, независимо от состояния входной шины 1. Результаты подсчета сравниваются элементом сравнения с кодом, записанным в регистре

хранения. В момент их равенства на выходе элемента сравнения появляется сигнал положительного уровня, устанавливающий в исходное (нулевое) состояние регистр хра- 5 нения кода, счетчик импульсов, триггер, заканчивая тем самым формирование выходного импульса. Использование для восстановления длительности выходного импульса импульсов от того же генератора,

0 что и при прямом преобразовании длительности входного импульса в код, обеспечивает равенство длительностей выходного и соответствующего входного импульсов. Временные диаграммы, поясняющие рабо5 ту преобразователя код-временной интервал, представлены на фиг.6.

Устройство обеспечивает выделение из серии импульсов максимального по длительности импульса, что обеспечивается пу0 тем записи кода, пропорционального длительности выделенного импульса, в регистр устройства последующим повторением импульса с помощью преобразователя кода во временной интервал. По сравнению

5 с известным предлагаемый селектор производит выделение импульсов, наибольших по длительности в парах сравнения.

Тем самым, селектор импульсов по длительности обеспечивает получение необхо0 димой дополнительной информации с серии входных импульсов.

Формула изобретения Селектор импульсов по длительности, содержащий генератор импульсов, вход ко5 торого соединен с входной шиной и входом формирователя импульсов, а первый выход - со счетным входом первого счетчика импульсов, выходы которого поразрядно соединены с информационными входами регистра па0 мяти, вход сброса которого соединен с входами сброса второго счетчика импульсов и выходом первого элемента ИЛИ, вход записи - с выходом первого элемента И, а выходы - поразрядно с информационными

5 входами первого преобразователя код-временной интервал, выход которого соединен с первой выходной шиной, счетный вход-с вторым выходом генератора импульсов и счетным входом второго преобразователя

0 код-временной интервал, вход сброса - с первыми входами первого и второго элементов ИЛИ, а управляющий вход - с вторым входом первого элемента ИЛИ и выходом первого дешифратора, входы кото5 рого поразрядно соединены с выходами второго счетчика импульсов, счетный вход которого соединен с входной шиной, причем первый вход формирователя импульсов соединен с первым входом первого элемента И и первым входом третьего элемента

ИЛИ, второй вход которого соединен с вторым выходом формирователя импульсов, входом сброса второго преобразователя код- временной интервал и первым входом первого элемента ИЛИ, а выход - с входом сброса первого счетчика импульсов, выходы которого поразрядно соединены с входами первой группы входов первого блока сравнения кодов, входы второй группы входов которого поразрядно ссоединены с выхода- ми регистра памяти, а выход - с вторым входом первого элемента И, причем выход второго элемента ИЛИ соединен с входом сброса триггера, выход которого соединен с первым входом второго элемета И, выход второго преобразователя код - временной интервал соединен с второй выходной шиной, а также четвертый и пятый элементы ИЛИ, элемент НЕ, второй дешифратор и третий и четвертый счетчики импульсов, о т- личающийся тем, что, с целью обеспечения возможности выделения импульсов, максимальных по длительности в парах соответствующих импульсов первой и третьей групп импульсов, а также второй и четвертой групп импульсов входной импульсной последовательности, содержащей N - 2 импульсов, где М 2, причем первая группа импульсов образована с первого по 2 2 -й импульсами входной импульсной последовательности, вторая группа - с 2

-И-и по 2()-й третья группа -с(2() го по (, четвертая группа - с (2м-2()+1}-го по 2м-й при одновременном обеспечении возможности распределения выделенных импульсов по выходным шинам в зависимости от результатов сравнения, в него введены с шестого по восьмой элементы ИЛИ, с первого по четвертый запоминающие блоки, пятый и шестой счетчи- ки импульсов, второй и третий блоки сравнения кодов, с третьего по пятый преобразователи код - временной интервал и с третьей по пятую выходные шины, которые соединены с выходами соответственно с третьего по пятый преобразователи код - временной интервал и с третьей по пятую выходные шины, которые соединены с выходами соответственно с третьего по пятый преобразователей код - временной интер- вал, входы сброса которых соединены с вторым выходом формирователя импульсов, счетные входы - с вторым выходом генератора импульсов, информационные входы с второго по пятый преобразователей код - временной интервал поразрядно соединены с выходами соответственно с первого по четвертый запоминающих блоков, управляющие входы которых соединены с выходом элемента НЕ, информационные входы - поразрядно с выходами первого счетчика импульсов, а адресные входы - поразрядно с выходами соответственно с четвертого по седьмой элементов ИЛИ, входы первой группы входов которых поразрядно соединены с выходами второго счетчика импульсов, а выходы второй группы входов - поразрядно с входами соответственно с третьего по шестой счетчиков импульсов, выходы сброса которых соединены с выходом второго элемента ИЛИ, счетные входы с- с выходом второго элемента И, установочные входы с четвертого по шестой счетчиков импульсов соединены с выходом первого дешифратора и входом установки триггера, причем (М+1)-й информационный вход четвертого счетчика импульсов, (М+1)-й и М-й информационные входы пятого счетчика импульсов, (М+1)-й вход группы входов восьмого элемента ИЛИ соединены с общей шиной, с М-го по первый информационные входы четвертого счетчика импульсов и с М-го по первый входы первой группы входов восьмого элемента ИЛИ соединены соответственно с (М+1)-го по второй выходами второго счетчика импульсов, с (М-1)-го по первый информационные входы пятого счетчика импульсов и с (М-1)-го по первый входы второй группы входов восьмого элемента ИЛИ соединены соответственно с {М+1)-го по третий выходами второго счетчика импульсов, причем выходы восьмого элемента ИЛИ поразрядно соединены с информационными входами шестого счетчика импульсов, выходы которого поразрядно соединены с входом второго дешифратора, выход которого соединен с вторым входом второго элемента ИЛИ, выходы первого запоминающего блока поразрядно соединены с входами первой группы входов второго блока сравнения кодов, входы второй группы входов которого поразрядно соединены с выходами второго запоминающего блока, а первый и второй выходы - с управляющими входами соответственно второго и третьего преобразователей код - временной интервал, выходы третьего запоминающего блока поразрядно соединены с входами первой группы входов третьего блока сравнения кодов, входы второй группы входов которого поразрядно соединены с выходами четвертого запоминающего блока, а первый и второй выходы - с управляющими входами соответственно четвертого и пятого преобразователей код - временной интервал, причем первый выход формирователя импульсов соединен с входом элемента НЕ, третий выход генератора импульсов - с вторым входом второго элемента И.

Я 22

30

Риг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Селектор импульсов по длительности | 1988 |

|

SU1529437A1 |

| Устройство селекции импульсов по длительности | 1990 |

|

SU1758863A1 |

| Селектор импульсов по длительности | 1986 |

|

SU1422383A1 |

| Селектор серий импульсов | 1989 |

|

SU1670781A1 |

| Селектор импульсов по длительности | 1989 |

|

SU1688399A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Кольцевая система громкоговорящей связи с временным разделением каналов | 1990 |

|

SU1699359A3 |

| Устройство для измерения частоты и ритмичности сердечных сокращений | 1984 |

|

SU1219048A1 |

| СЕЛЕКТОР СИГНАЛОВ ПО ДЛИТЕЛЬНОСТИ | 1990 |

|

RU2028027C1 |

| УСТРОЙСТВО СЕЛЕКЦИИ ДВУХ РЕТРАНСЛИРОВАННЫХ СИГНАЛОВ | 1996 |

|

RU2103811C1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах обработки информации. Целью изобретения является обеспечение возможности выделения импульсов, максимальных по длительности в парах соответствующих импульсов первой и третьей групп импульсов, а также второй и четвертой групп импульсов входной импульсной последовательности, содержащей N 2 импульсов, где М , 2, причем первая группа импульсов образована с первого по 2 2 -й импульсами входной импульсной последовательности, вторая группа - с (2()+1)-го по 2()-й. третья группа - с ( f 1)-ro по(2 м-2()-й, четвертая группа - с (2 М-2(М 2)+1)-го по 2м-й, при одновременном обеспечении возможности распределения выделенных импульсов по выходным шинам в зависимости от результатов сравнения. Селектор импульсов по длительности содержит входную шину 1, генератор 2 импульсов, формирователь 3. импульсов, преобразователи 4 и 5 код - временной интервал, счетчики 9-12 импульсов, дешифраторы 15 и 16, регистр 17 памяти, блок 18 сравнения кодов, элементы И 21 и 22, элементы ИЛИ 23-27, выходные шины 28 и 30, триггер 37 и элемент НЕ 38. Цель достигается за счет введения преобразователей 6-8 код-временной интервал, счетчиков 13 и 14 импульсов, блоков 19 и 20 сравнения кодов, элементов ИЛИ 29, 31 и 32, запоминающих блоков 33-36, выходных шин 39-41 и образования новых функциональных связей.8 ил.

9W. 2.

r

диод

чг

L.

Фиг.З

номеит поЭключени питания

Вх. тина 1 Вых. 5л. 3

Вых. Ь. 3

Мл.р-3 Уд. 9 Ст..9 Мл.р-Э5лНО Ст.р-З&л.-Ш

Мл.р-«5л.-17

Cm.p-3SJr.17

ВЫУ. . 5

1

Л

Раг.«

П

Пер0ьш бь/ход

-

Второй

1, OfTTPOi

ffb/лод

..J

п

пп

п

п

43

yUEL. Ьх.

W

Инф. Входы

77 77/// 47 TZ/tyw

подключения литания

1647876

Выход

А

44

/ V

45

1ь

I

I

Фиг. 6

момент гоЭк/чомвния питания

Вх 5л. 2

перббш

Гя.2

ппп пп п

дторой м. 2

пппппппппппп

| Селектор импульсов по длительности | 1982 |

|

SU1064451A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Селектор импульсов по длительности | 1988 |

|

SU1529437A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-05-07—Публикация

1988-07-19—Подача