- I I |,;5 27

Rii - 1.1.0 LHiMlJb

Изобретение относится к импульсной технике и предназначено для построения цифровых устройств.

Цель изобретения - расширение функциональных возможностей логического элемента.

На чертеже приведена схема предлагаемого логического элемента.

Логический элемент содержит пер- вый и второй 2 входные транзисторы базы которых через первый 3 и второй 4 резисторы подключены к шине 5 питания, эмиттеры подключены к первому 6 и второму 7 входам устройства, а коллекторы соединены с базами соответственно первого 8 и второго

9промежуточных транзисторов, коллектор первого промежуточного транзистора 8 через третий резистор

10подключен к шине 5 питания, эмиттер второго промежуточного транзистора 9 соединен с базой двухэмит- терного транзистора 11, первый эмиттер 12 которого соединен с базой второго промежуточного транзистора

9, второй эмиттер 13 - с базой первого промежуточного транзистора 8, а коллектор через четвертый резистор 14 подключен к общей шине 15 входу 16 первого инвертирующего выходного каскада 17, выход которого является первым выходом 18 устройства, эмиттер первого промежуточного транзистора 8 соединен с анодом первого диода 19, катод которого через пятый резистор 20 подключен к общей шине 15, коллектор первого промежуточного транзистора 8 соединен с анодом второго диода 21, катод которого под- ключен к входу 22 первого неинвертирующего каскада 23, выход которого является вторым выходом 24 устройства, катод первого диода 19 подключен к входу 25 второго инвертирую шего каскада 26, выход которого является третьим выходом 27 устройства коллектор второго промежуточного транзистора 9 соединен с анодом третьего диода 28i катод которого под- ключен к входу 29 второго неинвертирующего каскада 30, выход которого является четвертым выходом 31 устройства, база первого промежуточного транзистора 8 соединена с катодом четвертого диода 32, анод которого соединенен с эмиттером третьего промежуточного транзистора 33, коллекто которого соединен с коллектором первого промежуточного транзистора 8, а база - с базой второго промежуточного транзистора 9, коллектор которого через шестой резистор 34 подключен к шине питания 5.

Предлагаемый логический элемент работает следующим образом.

Пусть в исходном состоянии на входах 6 и 7 присутствует низкий потенциал, что соответствует значению О. В этом случае входные транзисторы 1 и 2 открыты, на их коллекторах и базах промежуточных транзисторов 8, 9 и 33 находится низкий потенциал, что обусловливает закрытое состояние промежуточных транзисторов 8, 9 и 33. На коллекторах промежуточных транзисторов 8, 9 и 33 присутствует высокий потенциал и на входы 22 и 29 неинвертирующего 23 и неинвертирующего 30 каскадов поступает ток от щины 5 питания соответ- свенно через резистор 10, прямо включенный диод 21, резистор 34, прямо включенный диод 28, что соответствует высокому потенциалу на входах 22 и 29 неинвертирующего 23 и Неинвертирующего 30 каскадов. Неинвертирующий 23 и неинвертирующий 30 каскады повторяют сигналы, поступающие на их входы 22 я 29 к на выходах 24 и 31 устройства присутствует высокий потенциал, т.е. 1. Промежуточные транзисторы 8, 9 и 33 закрыты, их эмиттерные токи отсутствуют, входы 25 и 16 инвертирующего 26 и инвертирующего 17 выходных каскадов имеют низкий потенциал, так как входы 25 и 16 соединены соответственно через резисторы 20 и 14 с общей шиной 15. Инвертирующий 17 и инвертирующий 26 выходные каскады инвертируют сигналы, постуйающие на их входы 16 и 25 и на выходах 18 и 27 устройства присутствует высокий потенциал, т.е. 1.

Если на входе 6 присутствует О, а на входе 7 - 1, то входной транзистор 1 открыт, потенциал его коллектора и базы промежуточного транзистора 8 низкий, что обуславливает закрытое состояние промежуточного транзистора 8. Эмиттерный ток закрытого промежуточного транзистора 8 отсутствует, и на входе 25 инвертирующего выходного каскада 26 имеется низкий потенциал, так как вход 25 пoдfcлючeн к общей шине 15 через

резистор 20. Инвертирующий выходной каскад 26 инвертирует сигнал, поступающий на его вход 25, и на выходе 27 устройства присутствует высокий потенциал, т.е. 1.

Входной транзистор 2 Находится в инверсном активном режиме и его базовый ток, определяемый резистором 4 обусловливает открытое состояние про межуточного транзистора 9. Эмиттер- ный ток промежуточного транзистора 9 через базу двухэмиттерного транзистора 11 ответвляется во второй эмиттер 13, соединенный с низким потенциалом коллектора открытого входного транзистора 1, Двухэмиттер- ный транзистор 11 открыт, на его коллекторе и входе 16 инвертирующего выходного каскада имеется низ- кий потенциал. Инвертирующий выход- ной каскад 17 инвертирует сигнал, поданный на его вход 16 и на выходе 18 устройства присутствует высокий потенциал. На коллекторе открытого промежуточного транзистора 9 находится низкий потенциал и на вход 29 неинвертирующего выходного каскада 30 ток от шины питания 5 не поступает, что соответствует низкому по- тенциалу на входе 29, Неинвертирующий выходной каскад 30 повторяет сигнал, поданный на его вход 29 и на выходе 31 устройства присутствует низкий потенциал, т.е. О.

Промежуточный транзистор 33 открыт, так как в его базу поступает ток от входного транзистора 2, находящегося в инверсном активном режиме, а эмиттер промежуточного трав- зистора 33 через прямо включенный диод 32 соединен с низким потенциало коллектора открытого входного транзистора 1 . На коллекторе открытого промежуточного транзистора 33 имеет- ся низкий потенциал, и на вход 22 неинвертирующего выходного каскада 23 ток от щины 5 питания не поступает, что соответствует низкому потенциалу на 22 неинвертирующего выходного каскада 23, Неинвертирую- вшй выходной каскад 23 повторяет сигнал, поданный на его вход 22, и на выходе 24 устройства присутствует низкий потенциал, т.е. О.

Если на входе 6 присутствует , а на входе 7 - О, входной транзистор 1 находится в инверсном активном режиме и его базовый ток, опре

д 0 5 о

д 5 0 5

5

деляемый резистором 3 обуславливает открытое состояние промежуточного транзистора 8. На коллекторе открытого промежуточного транзистора 8 имеется низкий потенциал, и ток от шины питания 5 не поступает на вход 22 Неинвертирующего выходного каскада 23, что соответствует низкому потенциалу на входе 22, Неинвертирующий выходной каскад 23 повторяет сигнал, поданный на его вход 22 и на выходе 24 устройства присутствует О.

Эмиттерный ток открытого промежуточного транзистора 8 создает на входе 25 инвертирующий выходной каскад 26 и резисторе 20 положительное падение напряжения,, что соответствует подаче на вход 25 1. Инвертирующий выходной каскад 26 инвертирует сигнал, поданный на его вход 25, и на выходе 27 устройства присутствует О.

Промежуточные транзисторы 9 и 33 закрыты, так как их базы соединены с низким потенцалом коллектора открытого входного транзистора 2. На коллекторе закрытого промежуточного транзистора 9 имеется высокий потенциал, и на вход 29 неинвертирующего выходного каскада 30 ток от шины 5 питания через резистор 34, прямо включенный диод 28, что соответствует подаче 1 на вход 29. Неинвертирующий вогходной каскад 30 повторяет сигнал, поданный на его вход 29, и на выходе 31 устройства присутствует 1. Эмиттерный ток закрытого промежуточного транзистора 9 отсутствует, на входе 16 инвертирующего выходного каскада 17 имеется низкий потенциал, так как вход 16 подкл)очен через резистор 14 к общей тине 15. Инвертирующий выходной каскад 17 инвертирует сигнал, подан- на его вход 16, и на выходе 18 устройства присутствует 1.

Если на входах 6 и 7 присутствует 1, входные транзисторы 1 и 2 находятся в инверсном активном режиме и их базовые токи, определяемые резисторами 3 и 4, обусловливает открытое состояние промежуточных транзисторов 8 и 9. Промежуточный транзистор 33 открыт, и через эмиттерный переход промежуточного транзистора 33 и диод 32 протекает, так как база промежуточного транзистора

7

33 и катод диода 32 подключены к одинаковым потенциалам без открытых промежуточных транзисторов 8 и 9.

На коллекторе открытого промежуточного транзистора 8 имеется низкий потенциал, и на вход 22 неинвертирую шего выходного каскада 23 ток от шины питания не поступает, что соответствует подаче на вход 22 уровня О. Неинвертирующий выходной -каскад 23 повторяет сигнал, поданный на его дход 22, и на выходе 24 устройства присутствует О, Эмиттерный ток открытого промежуточного транзистора 8 создает на входе 25 инвертирующего выходного каскада 26 и резисторе 20 положительное падение .напряжения, что соответствует подаче на вход 25 уровня 1. Инвертирующий выходной каскад 26 инвертирует сигнал, поданный на его вход 25, и на выходе 27 устройства присутствует О. Двух- эмиттерный транзистор 11 находится в инверсном активном режиме, так как его первый 12 и второй 13 эмиттеры соединены с высокими потенциалами коллекторов входных транзисторов 1 и 2 и эми терный ток открытого промежуточного транзистора 9 ответвляется в коллектор двухэмиттерного транзистора 11, что создает на входе

16инвертирующего выходного каскада

17и резисторе 14 положительное падение напряжения, т.е. высокий по-г тенциал на входе 16. Инвертирующий выходной каскад 17 инвертирует сигнал, поданный еа его вход 16, и на выходе 18 устройства присутствует низкий потенциал, т.е. О.

Диоды 21 и 28 предназначены для надежного запирания неинвертирующего 23 и неинвертирующего 30 выходных каскадов при различных значениях сигналов на входах 6 и 7. Диод 19 предназначен для обеспечения одинаковых порогов включения промежуточных транзисторов 8 и 9. Диод 32 предназначен дпя обеспечения одинаковых порогов включения промежуточных

транзисторов 9 и 33 при подаче на вход 6 О, а на вход 7 - 1.

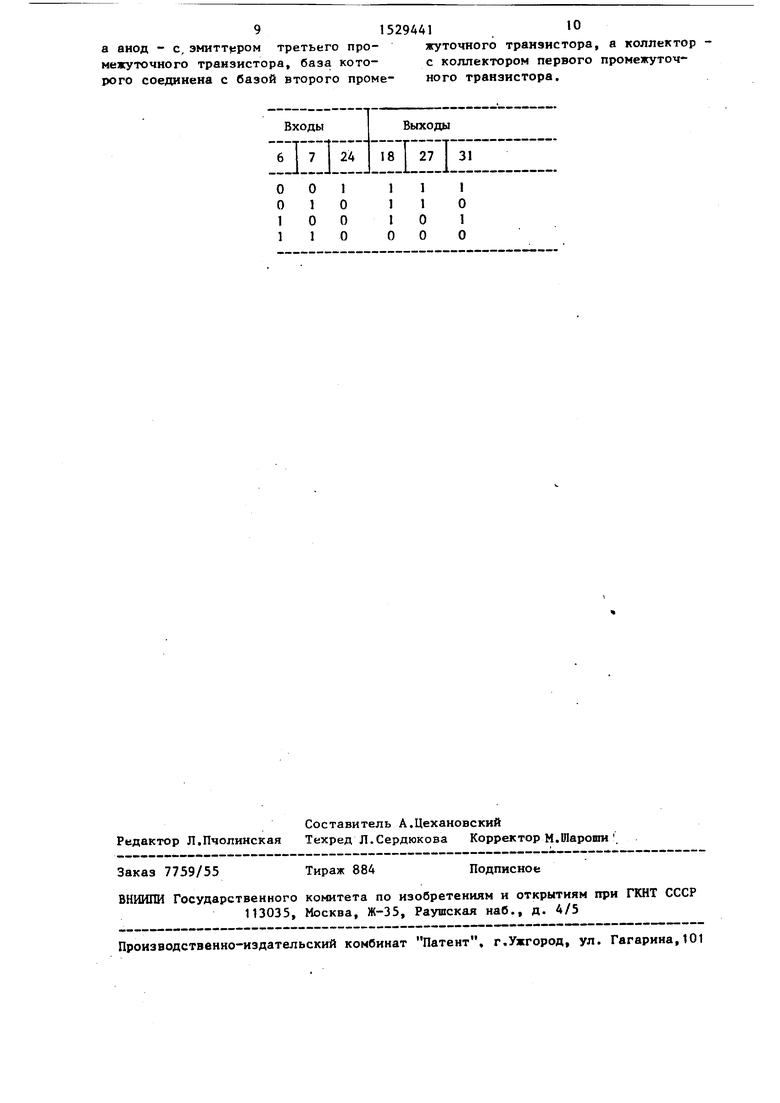

Состояния входов и выходов логического элемента сведены в таблицу.

Из таблицы видно, что на входах 24, 18, 27 и 31 реализуются логические функции соответственно: ИЛИ- НЕ, И-НЕ, ИНВЕРСИЯ XI, ИНВЕРСИЯ Х2, где XI, Х2 состояние логических

сигналов на входах соответственно 6 и 7.

o

5

0

5

Формула изобретения

Логический элемент, содержащий первый и второй входные транзисторы, базы которых через первый и второй резисторы подключены к шине питания, эмиттеры - к первому и второму входам элемента, а коллекторы соединены с базами соответственно первого и . второго промежуточных транзисторов, коллектор первого промежуточного транзистора через третий резистор подключен к щине питания, а эмиттер второго промежуточного транзистора соединен с базой двухэьмттерного транзистора, первый и второй эмиттеры которого соединены соответственно с базами второго и первого промежуточных транзисторов, а коллектор через четвертый резистор подключен к общей шине и соединен с входом первого инвертирующего выходного каскада; выход которого является первым выходом элемента, пятый резистор, под

ключенный первым выводом к общей шине, и Первый неинвертирующий выходной каскад, выход которого является вторым выходом элемента, отличающийся тем, что, с целью расширения функциональных возможностей, в Него введены первый - четвертый диоды, третий промежуточный транзистор, шестой резистор, вторые неинвертирующий и инвертирующий выходные каскады, причем анод первого диода соединен с эмиттером первого промежуточного транзистора, а катод - с вторым выводом пятого резистора и входом второго инвертирующего выходного каскада, выход которого явля- ется третьим выходом элемента, анод второго диода соединен с коллектором первого промежуточного транзистора, а катод подключен к входу первого неинвертирующего выходного каскада, анод третьего диода подключен к коллектору второго промежуточного транзистора и через шестой резистор к шине питания, а катод - к входу второго Неинвертирующего выходного каскада, выход которого является четвертым выходом элемента, катод четвертого диода соединен с базой первого промежуточного транзистора.

9152944110

а анод - с, эмитт ;ром третьего про- жуточного транзистора, а коллектор межуточного транзистора, база кото- с коллектором первого промежуточ рого соединена с базой второго проме- ного транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент | 1988 |

|

SU1554136A1 |

| Логический элемент | 1983 |

|

SU1138941A1 |

| Логический элемент | 1984 |

|

SU1261105A1 |

| Логический элемент | 1985 |

|

SU1262717A1 |

| Стабилизированный источник питания | 1981 |

|

SU993228A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| УСИЛИТЕЛЬ МОЩНОСТИ ЗВУКОВОЙ ЧАСТОТЫ | 1993 |

|

RU2115224C1 |

| Стабилизированный источник питания | 1989 |

|

SU1624593A2 |

| Устройство для управления высоковольтным силовым транзистором | 1991 |

|

SU1835118A3 |

| Перемножающее устройство | 1983 |

|

SU1168971A1 |

Изобретение относится к импульсной технике и предназначено для построения цифровых устройств. Логический элемент содержит входные транзисторы 1, 2, промежуточные транзисторы 8, 9, 33, неинвертирующий каскад 23, инвертирующий каскад 17. Введение диодов 19, 21, 28, 32, промежуточного транзистора 33, резистора 34, неинвертирующего 30 и инвертирующего 26 выходных каскадов, соединенных соответствующим образом, позволяет расширить функциональные возможности логического элемента. Логический элемент с двумя входами позволяет реализовать четыре логические функции на выходах элементов ИЛИ-НЕ, И-НЕ, ИНВЕРСИЯ X1, ИНВЕРСИЯ X2, где X1, X2 - логические состояния сигналов на первом и втором входах устройства. 1 ил.

Входы 6 I 7 I 24

Выходы

01

1О

0о

1о

Составитель А.Цехановский Редактор Л.Пчолинская Техред Л.Сердюкова Корректор М.Шароши .

Заказ 7759/55

Тираж 884

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г.Ужгород, ул. Гагарина,101

Выходы

1 1 I

1 1 о 1 о 1 000

Подписное

| Логический элемент | 1984 |

|

SU1261105A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-12-15—Публикация

1988-04-05—Подача