Изобретение относится к импульсной технике и предназначено для построения цифровых устройств.

Цель изобретения - расширение функциональных возможностей логического элемента путем реализации логических функций ИЛИ-НЕ, И-НЕ, И, ИЛИ.

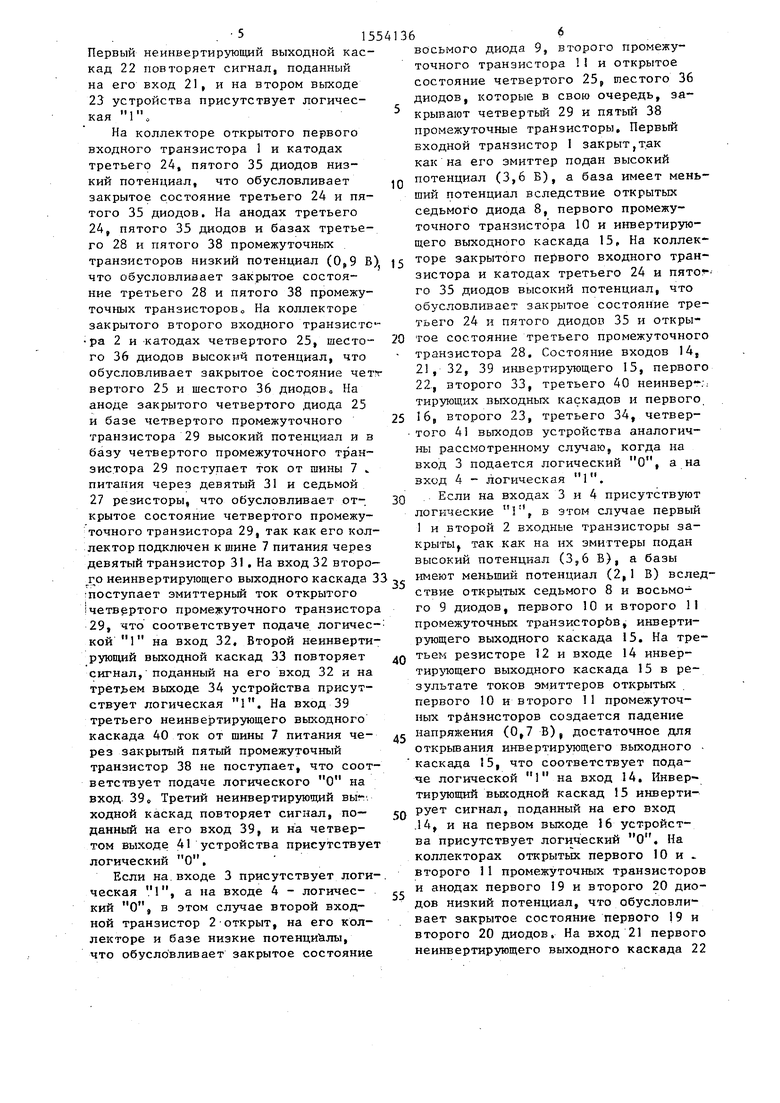

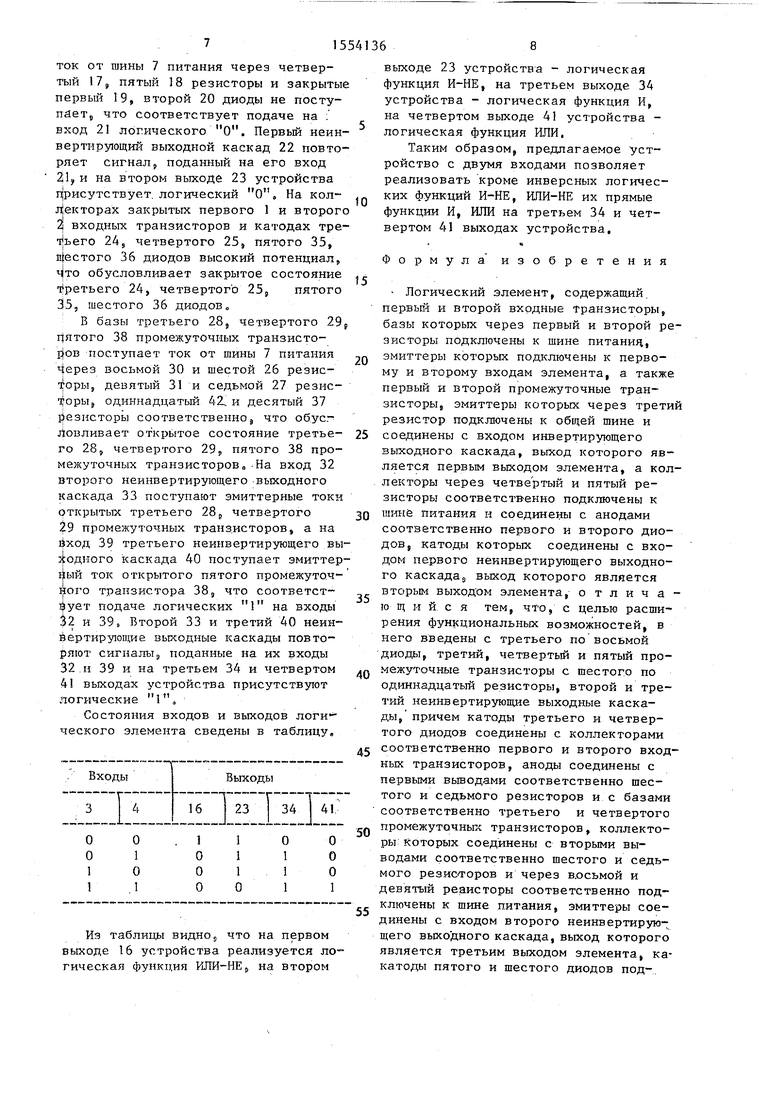

На чертеже представлена принципиальная электрическая схема логического элемента

Логический элемент содержит первый 1 и второй 2 входные транзисторы, эмиттеры которых подключены к первому 3 и второму 4 входам устройства, базы которых через первый 5 и второй 6 резисторы соответственно подключены к шине 7 питания и соединены с анодами седьмого 8 и восьмого 9 диодов, катоды которых соединены с базами соответственно первого 10 и второго 11 промежуточных транзисторов, эмиттеры которых через третий резистор 12 подключены к общей шине 13 и соединегны с входом 14 инвертирующего выходного каскада 15. Выход каскада 15 является первым выходом 1В устройства, а коллекторы через четвертый 17 и пятый 18 резисторы соответственно подключены к mime 7 питания и соединены с анодами соответственно первого 1 9 и второго 20 диодов, катоды которых соединены с входом 21 первого неинвертирующего выходного каскада 22, выход которого является вторым выходом 23 устройства.. Коллекторы первого 1 и второго 2 входных транзисторов соединены с катодами третьего 24 и четвертого 25 диодов, аноды которых соединены с первыми выводами соответственно шестого 26 и седьмого 27 резисторов и базами третьего 28 и четвертого 29 промежуточных транзисторов, коллекторы которых сое- динены с вторыми выводами соответственно шестого 26 и седьмого 27 резисторов и подключены к шине 7 питаШ

С

ел сд

Јь

СЛ &

гаЬ.

ния через восьмой 30 и девятый 31 peзисторы соответственно, а эмиттеры соединены с входом 32 второго неинвертирующего выходного каскада 33, выход которого является третьим выходом 34 устройства. Коллекторы первого 1 и второго 2 входных транзисторов соединены с катодами соответственно пятого 35 и шестого 36 диодов, аноды которых соединены с первым выводом десятого резистора 37 и базой пятого промежуточного транзистора 38, . коллектор которого соединен с вторым выводом десятого резистора 37, а эмиттер соединен с входом 39 третьего неинвертирующего выходного каскада 40, выход которого является четвертым выходом 41 устройства. Коллектор транзистора 38 через одиннадцатый резистор 42 подключен к шине 7 питания.

Логический элемент., работает следующим образом.

Пусть в исходном состоянии на входах 3 и 4 низкий уровень, что соответствует подаче логических О на входы 3 и 4, В этом случае первый 1 |И второй 2 входные транзисторы откры- |тЫ|На их базах и анодах седьмого 8 и восьмого 9 диодов низкие потенциалы, что обусловливает закрытое состояние первого 10 и второго 11 промежуточных транзисторов. Вход 14 инвертирующего выходного каскада 15 оказывается соединенным с общей шиной 13 через третий резистор 12, что соответствует подаче логического О на вход 14. Инвертирующий выходной каскад инвертирует сигнал, поданный на его вход 14, и на первом выходе 16

устройства присутствует логическая

Hi м i

На коллекторах закрытых первого 10 и второго 11 промежуточных транзисторов высокий потенциал и на вход 21 первого неинвертирующего выходного каскада 22 поступает ток от шины 7 питания через четвертый 17, пятый 18 резисторы и прямо включенные первый 19 и второй 20 диоды, что соответствует подаче логической 1 на вход 21. Первый неинвертирующий выходной каскад 22 повторяет сигнал, поданный на его вход 21, и на втором выходе 23 устройства присутствует логическа 1. На коллекторах первого 1 и второго 2 входных транзисторов и катода третьего 24, четвертого 25, пятого

5

0

5

0

5

0

5

0

5

35, шестого 36 диодов низкие потенциалы, что обусловливает открытое состояние третьего 24, четвертого 25, пятого 35, шестого 36 диодов. На анодах третьего 24, четвертого 25, пятого 35, шестого 36 диодов и базах третьего 28, четвертого 29, пятого 38 промежуточных транзисторов низкий потенциал Uj +U , 9 В, где ,7B; ,2 В - падения напряжения на открытом диоде и между коллектором и эмиттером открытого транзистора, что обусловливает закрытое состояние третьего 28, четвертого 29 и пятого 38 промежуточных транзисторов. На входы 32 и 39 второго 33 и третьего 40 неинвертирующего выходных каскадов ток от шины 7 питания не поступает, что соответствует подаче логических О на входы 32 и 39. Второй 33 и третий 40 неинвертирующие выходные каскады повторяют сигналы, поданные на их входы 32 и 39, и на третьем 34 и четвертом 41 выходах устройства приг; сутствуют логические О.

Если на входе 3 логический О, а на входе 4 - логическая 1, в этом случае первый входной транзистор 1 открыт, на его базе и аноде седьмого диода низкий потенциал, что обусловливает закрытое состояние первого промежуточного транзистора 10. Второй входной транзистор 2 закрыт, так как на его эмиттер подан высокий потенциал (3,6 В), а база имеет меньший потенциал за счет открытых восьмого диода 9, второго промежуточного транзистора 11 и инвертирующего выходного каскада 15, Эмиттерный ток открытого второго промежуточного транзистора 11 создает на третьем резисторе 12 и входе 14 инвертирующего выходного каскада 15 падение напряжения (0,7 В), достаточное для открывания инвертирующего выходного каскада 15, что соответствует подаче логической 1 на вход 14„ Инвертирующий выходной каскад 15 инвертирует сигнал, поданный на его вход 14, и на первом выходе 16 устройства присутствует логический О, На коллекторе закрытого первого промежуточного транзистора 10 - высокий потенциал и на вход 21 первого неинвертирующего выходного каскада 22 поступает ток от шины 7 питания через четвертый резистор 17, прямовключен- ный первый диод 19, что соответствует подаче логической 1 на вход 21.

Первый неинвертирующий выходной каскад 22 повторяет сигнал, поданный на его вход 21, и на втором выходе 23 устройства присутствует логическая 1.

На коллекторе открытого первого входного транзистора 1 и катодах третьего 24, пятого 35 диодов низкий потенциал, что обусловливает закрытое состояние третьего 24 и пятого 35 диодов. На анодах третьего 24, пятого 35 диодов и базах третьего

10

восьмого диода 9, второго промежуточного транзистора 11 и открытое состояние четвертого 25, шестого 36 диодов, которые в свою очередь, закрывают четвертый 29 и пятый 38 промежуточные транзисторы. Первый входной транзистор 1 закрыт,так как на его эмиттер подан высокий потенциал (3,6 Б), а база имеет мень ший потенциал вследствие открытых седьмого диода 8, первого промежуточного транзистора 10 и инвертирующего выходного каскада 15, На коллек

28 и пятого 38 промежуточных транзисторов низкий потенциал (0,9 В), 15 т°Ре закрытого первого входного тран

зистора и катодах третьего 24 и пято го 35 диодов высокий потенциал, что ооусловливает закрытое состояние третьего 24 и пятого диодоп 35 и открытое состояние третьего промежуточного транзистора 28. Состояние входов 14,

что ооусловливает закрытое состояние третьего 28 и пятого 38 промежуточных транзисторов о На коллекторе закрытого второго входного транзистс- ра 2 и катодах четвертого 25, шестого 36 диодов высокий потенциал, что обусловливает закрытое состояние чет вертого 25 и шестого 36 диодов„ На аноде закрытого четвертого диода 25 и базе четвертого промежуточного транзистора 29 высокий потенциал и а базу четвертого промежуточного транзистора 29 поступает ток от шины 7 „ питания через девятый 31 и седьмой 27 резисторы, что обусловливает открытое состояние четвертого промежуточного транзистора 29, так как его коллектор подключен к шине 7 питания через девятый транзистор 31 . На вход 32 второ-

20

зистора и катодах третьего 24 и пято- го 35 диодов высокий потенциал, что ооусловливает закрытое состояние третьего 24 и пятого диодоп 35 и открытое состояние третьего промежуточного транзистора 28. Состояние входов 14,

21,32, 39 инвертирующего 15, первого

22,второго 33, третьего 40 неинвертирующих пыходных каскадов и первого

25 16, второго 23, третьего 34, четвертого 41 выходов устройства аналогичны рассмотренному случаю, когда на вход 3 подается логический О, а на вход 4 - логическая 1.

Если на входах 3 и 4 присутствуют логические 1, в этом случае первый I и второй 2 входные транзисторы за- крытьц так как на их эмиттеры подан высокий потенциал (3,6 В), а базы

30

го неинвертирующего выходного каскада 33 ,, имеют меньший потенциал (2,1 В) вследпоступает эмиттерный ток открытого четвертого промежуточного транзистора 29, что соответствует подаче логической 1 на вход 32. Второй неинвертирующий выходной каскад 33 повторяет сигнал, поданный на его вход 32 и на третьем выходе 34 устройства присутствует логическая 1. На вход 39 третьего неинвертирующего выходного каскада 40 ток от шины 7 питания через закрытый пятый промежуточный транзистор 38 не поступает, что соответствует подаче логического О на вход 39 „ Третий неинвертирующий выходной каскад повторяет сигнал, поданный на его вход 39, и на четвертом выходе 41 устройства присутствует логический О.

Если на входе 3 присутствует логическая 1, а на входе 4 - логический О, в этом случае второй входной транзистор 2 открыт, на его коллекторе и базе низкие потенциалы, что обусловливает закрытое состояние

40

ствие открытых седьмого 8 и восьмого 9 диодов, первого 10 и второго 11 промежуточных транзисторЬв, инвертирующего выходного каскада 15. На третьем резисторе 12 и входе 14 инвертирующего выходного каскада 15 в результате токов эмиттеров открытых первого 10 и второго 11 промежуточных транзисторов создается падение .с напряжения (0,7 В), достаточное для открывания инвертирующего выходного каскада 15, что соответствует подаче логической 1 на вход 14. Инвертирующий выходной каскад 15 инвертирует сигнал, поданный на его вход 14, и на первом выходе 16 устройства присутствует логический О. На коллекторах открытых первого 10 и - второго 11 промежуточных транзисторов и анодах первого 19 и второго 20 диодов низкий потенциал, что обусловливает закрытое состояние первого 19 и второго 20 диодов, На вход 21 первого неинвертирующего выходного каскада 22

50

55

восьмого диода 9, второго промежуточного транзистора 11 и открытое состояние четвертого 25, шестого 36 диодов, которые в свою очередь, закрывают четвертый 29 и пятый 38 промежуточные транзисторы. Первый входной транзистор 1 закрыт,так как на его эмиттер подан высокий потенциал (3,6 Б), а база имеет меньший потенциал вследствие открытых седьмого диода 8, первого промежуточного транзистора 10 и инвертирующего выходного каскада 15, На коллект°Ре закрытого первого входного тран

т°Ре закрытого первого входного тран

зистора и катодах третьего 24 и пято- го 35 диодов высокий потенциал, что ооусловливает закрытое состояние третьего 24 и пятого диодоп 35 и открытое состояние третьего промежуточного транзистора 28. Состояние входов 14,

21,32, 39 инвертирующего 15, первого

22,второго 33, третьего 40 неинвертирующих пыходных каскадов и первого

16, второго 23, третьего 34, четвертого 41 выходов устройства аналогичны рассмотренному случаю, когда на вход 3 подается логический О, а на вход 4 - логическая 1.

Если на входах 3 и 4 присутствуют логические 1, в этом случае первый I и второй 2 входные транзисторы за- крытьц так как на их эмиттеры подан высокий потенциал (3,6 В), а базы

0

ствие открытых седьмого 8 и восьмого 9 диодов, первого 10 и второго 11 промежуточных транзисторЬв, инвертирующего выходного каскада 15. На третьем резисторе 12 и входе 14 инвертирующего выходного каскада 15 в результате токов эмиттеров открытых первого 10 и второго 11 промежуточных транзисторов создается падение с напряжения (0,7 В), достаточное для открывания инвертирующего выходного каскада 15, что соответствует подаче логической 1 на вход 14. Инвертирующий выходной каскад 15 инвертирует сигнал, поданный на его вход 14, и на первом выходе 16 устройства присутствует логический О. На коллекторах открытых первого 10 и - второго 11 промежуточных транзисторов и анодах первого 19 и второго 20 диодов низкий потенциал, что обусловливает закрытое состояние первого 19 и второго 20 диодов, На вход 21 первого неинвертирующего выходного каскада 22

0

5

ток от шины 7 питания через четвертый 17, пятый 18 резисторы и закрытые первый 19, второй 20 диоды не поступает, что соответствует подаче на вход 21 логического О. Первый неин- вертпрующий выходной каскад 22 повторяет сигнал, поданный на его вход 21, и на втором выходе 23 устройства присутствует логический О. На коллекторах закрытых первого 1 и второго 2 входных транзисторов и катодах третьего 24, четвертого 25, пятого 35, шестого 36 диодов высокий потенциал, что обусловливает закрытое состояние третьего 24, четвертого 25, пятого 35, шестого 36 диодов.

В базы третьего 28, четвертого 29, пятого 38 промежуточных транзисторов поступает ток от шины 7 питания через восьмой 30 и шестой 26 резисторы, девятый 31 и седьмой 27 резисторы, одиннадцатый 4Z. н десятый 37 резисторы соответственно, что обусловливает открытое состояние третьего 28, четвертого 29, пятого 38 промежуточных транзисторов. На вход 32 второго неинвертирующего выходного каскада 33 поступают эмиттерные токи открытых третьего 28, четвертого 29 промежуточных транзисторов, а на вход 39 третьего неинвертирующего выходного каскада 40 поступает эмиттер- пый ток открытого пятого промежуточного транзистора 38, что соответствует подаче логических 1 на входы 32 и 39, Второй 33 и третий 40 неин- пертирующие выходные каскады повторяют сигналы, поданные на их входы 32 н 39 и на третьем 34 и четвертом

41 выходах устройства присутствуют логические

Г

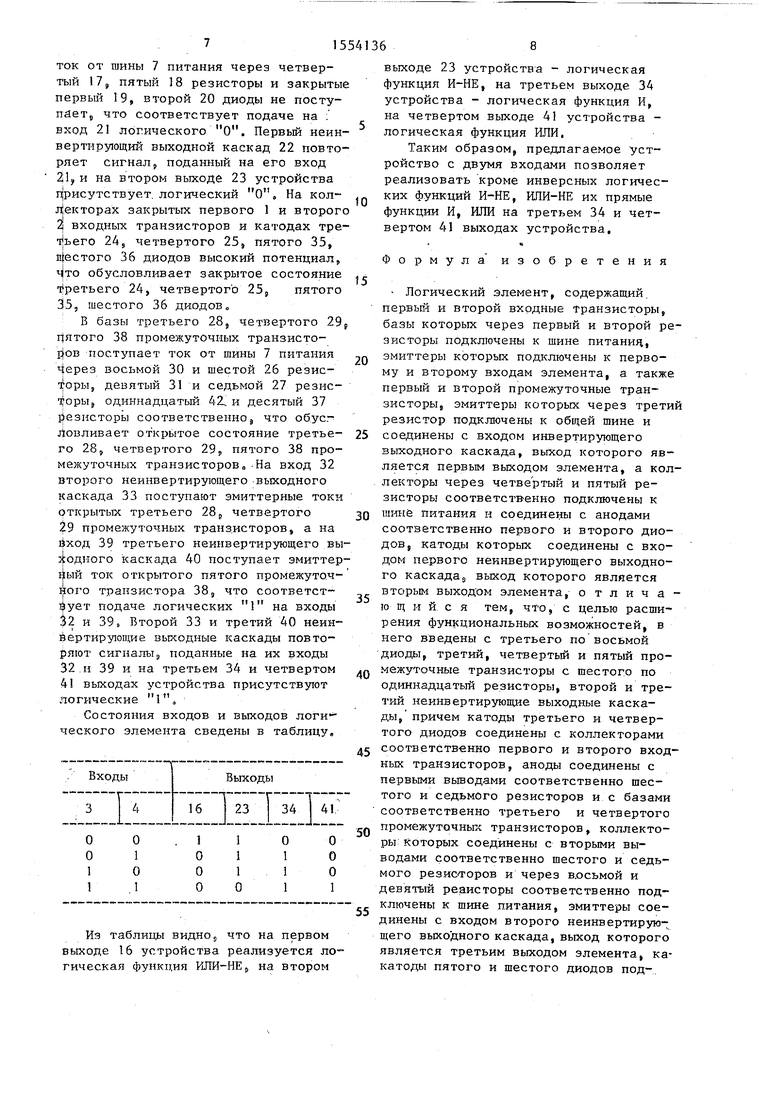

Состояния входов и выходов логического элемента сведены в таблицу.

Из таблицы видно, что на первом выходе 16 устройства реализуется логическая функция ИЛИ-НЕ, на втором

5

0

5

выходе 23 устройства - логическая функция И-НЕ, на третьем выходе 34 устройства - логическая функция И, на четвертом выходе 41 устройства - логическая функция ИЛИ.

Таким образом, предлагаемое устройство с двумя входами позволяет реализовать кроме инверсных логических функций И-НЕ, ИЛИ-НЕ их прямые функции И, ИЛИ на третьем 34 и четвертом 41 выходах устройства.

Формула изобретения

Логический элемент, содержащий первым и второй входные транзисторы, базы которых через первый и второй резисторы подключены к шине питания,, эмиттеры которых подключены к первому и второму входам элемента, а также первый и второй промежуточные транзисторы, эмиттеры которых через третий резистор подключены к общей шине и соединены с входом инвертирующего выходного каскада, выход которого является первым выходом элемента, а коллекторы через четвертый и пятый резисторы соответственно подключены к тине питания н соединены с анодами соответственно первого и второго диодов, катоды которых соединены с входом первого неинвертирующего выходного каскада, выход которого является вторым выходом элемента, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены с третьего по восьмой диоды, третий, четвертый и пятый промежуточные транзисторы с шестого по одиннадцатый резисторы, второй и третий неинвертирующие выходные каскады, причем катоды третьего и четвертого диодов соединены с коллекторами соответственно первого и второго входных транзисторов, аноды соединены с первыми выводами соответственно шестого и седьмого резисторов и с базами соответственно третьего и четвертого Q промежуточных транзисторов, коллекторы которых соединены с вторыми выводами соответственно шестого и седьмого резисторов и через в.осьмой и девятый реаисторы соответственно подключены к шине питания, эмиттеры соединены с входом второго неинвертирующего выходного каскада, выход которого является третьим выходом элемента, ка- катоды пятого и шестого диодов под0

5

0

5

5

ключены к коллекторам соответственно первого и второго входных транзисторов, аноды которых соединены с первым выводом десятого резистора и ба- ( зой пятого промежуточного транзистора, коллектор которого соединен с вторым выводом десятого резистора и через одиннадцатый резистор подключен к шине питания, эмиттер соединен с

входом третьего неннпертирутощего выходного каскада, выход которого является четвертым выходом элемента, катоды седьмого и восьмого диодов соединены с базами соответственно первого и второго промежуточных транзисторов, а аноды - с базами соответственно первого и второго входных транзисторов .

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент | 1988 |

|

SU1529441A1 |

| Логический элемент | 1983 |

|

SU1138941A1 |

| Логический элемент | 1984 |

|

SU1261105A1 |

| Логический элемент | 1985 |

|

SU1262717A1 |

| Устройство для управления высоковольтным силовым транзистором | 1991 |

|

SU1835118A3 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| Перемножающее устройство | 1983 |

|

SU1168971A1 |

| Устройство для выделения тактовой частоты при воспроизведении цифрового сигнала | 1991 |

|

SU1770985A1 |

| Генератор задержанных импульсов | 1990 |

|

SU1750037A1 |

| СИНХРОННЫЙ ГЕНЕРАТОР С ПРЕЦИЗИОННОЙ СИСТЕМОЙ УПРАВЛЕНИЯ | 2005 |

|

RU2295192C1 |

Изобретение относится к импульсной технике и предназначено для построения цифровых устройств. Цель изобретения - расширение функциональных возможностей логического элемента. Логический элемент содержит два входных транзистора, пять промежуточных транзисторов, восемь диодов, одиннадцать резисторов, инвертирующий и три неинвертирующих выходных каскада. Введение новых элементов и связей позволяет логическому элементу с двумя входами реализовать четыре логические функции: И-НЕ, ИЛИ-НЕ, И, ИЛИ. 1 ил, 1 табл.

| Устройство для управления ковочными гидравлическими прессами с электрическим приводом | 1926 |

|

SU12611A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Логический элемент | 1983 |

|

SU1138941A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-03-30—Публикация

1988-07-12—Подача