Изобретение относится к импульсИ технике и предназначено для построения цифровых логических устройств.

Известен логический элемент, содержащий входной многоэмиттерный транзистор, соединенный коллёктором с базой промежуточного транзистора, эмиттер которого через диод подключен к общей шине, а также выходной каскад, в состав которого входит эмиттерный повторитель на транзисторе, база которого является его входом, коллектор подключен к шине питания, а эмиттер через диод - к его выходу, который через резистор подключен к общей щине, а также сложный инвертор на дополнякяцих транзисторах разного типа проводимости, причем база первого транзистора соединена с базой транзистора эмиттарного повторителя, коллектор подключен к шине питания, а база второг транзистора обратной проводимости подключена к выходу эмиттерного повторителя, коллектор - к общей шине, а эмиттер соединен с эмиттером первого транзистора и образует выход устройства Ql .

Недостатком такого логического элемента является то, что он не выполняет функцию ИЛИ-НЕ в положительной логике.

Наиболее близким по технической сущности к предложенному техническому решению является логический элемент, содержащий первый и второй входные транзисторы, базы которых через первый и второй резисторы подключены к шине питания, эмиттеры подключены к первому и второму входам устройства, а коллекторы соединены с базами соответственно первого и второго промежуточных транзисторов эмиттеры которых подключены к входу инвертирующего выходного каскада и через третий резистор подключены к общей щине, коллектор первого промежуточного транзистора через четвертый резистор соединен с шиной питания и подключен к коллектору второго промежуточного транзистора и базе верхнего транзистора иивертйрующего выходного каскада 2J.

Недостатком известного логического элемента является то, что он не выполняет функцию в положительной логике.

Цель изобретения - расширение функциональных возможностей логического элемента.

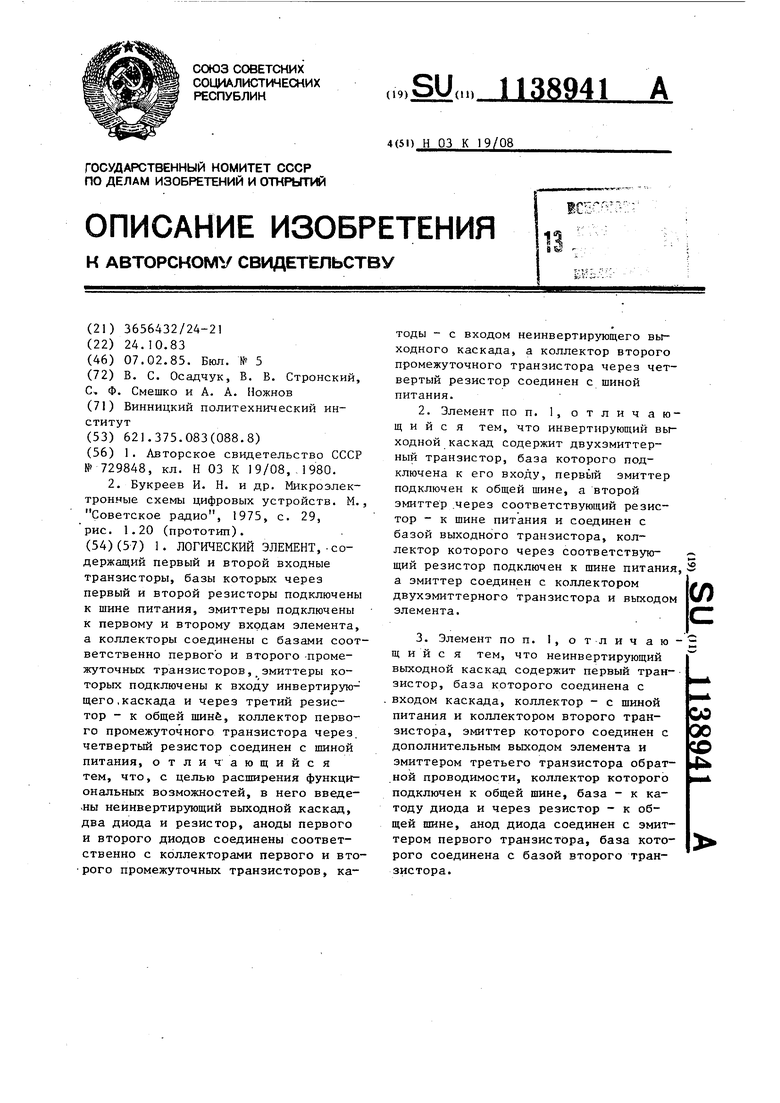

Поставленная цель достигается тем что в логический элемент, содержащий первый и второй входн ме транзисторы, база которых через первый и второй резисторы подключены к шине питания, эмиттеры подключены к первому и второму входам элемента, а коллекторы соединены с базами соответственно первого и второго промежуточных транзисторов, эмиттеры которых подключены к входу инвертирующего выходного каскада и через третий резистор - к общей шине, коллектор первого промежуточного транзистора через четвертый резистор соединен с шиной питания, дополнительно введены неинвертирующий выходной каскад - два диода и резистор, аноды первого и второго диодов соединены соответствено с коллекторами первого и второго промежуточных транзисторов,- катодыс входом неинвертирующего выходного каскада, а коллектор второго промежуточного транзистора через четвертый резистор соединен с шиной питания.

При этом инвертирующий выходной каскад содержит двухэмиттерный транзистор, база которого подключена к его входу, первый эмиттер подключен к общей шине, а второй эмиттер через соответствующий резистор - к шине питания и соединен с базой выходного транзистора, коллектор которого чере соответствующий резистор подключен к шине питания, а эмиттер соединен с коллектором двухэмиттерного транзистора и выходом элемента.

Кроме того, неинвертирующий выходной каскад содержит первый транзистор, база которого соединена с входом каскада, коллектор - с шиной питания и коллектором второго тран-i i зистора, эмиттер которого соединен с дополнительным выходом элемента и эмиттером третьего транзистора обратной проводимости, коллектор которого подключен к общей шине, база к катоду диода и через резистор к общей шине, анод дийда соединен с эмиттером первого транзистора, база которого соедийена с базой второго транзистора.

На чертеже приведена принципиаль ная электрическая схема логическог-о элемента. Логический элемент содержит первый 1 и второй 2 входные транзисторы базы которых через первый и второй резисторы 3 и 4 подключены к шине 5 питания, эмиттеры подключены к первому и второму входам 6 и 7 устройства, а коллекторы соединены с базами соответственно первого 8 и второго 9 промежуточных транзисторов, эмиттеры которых подключены к входу инвертирующего выходного каскада 10, и через третий резистор 11 - к общей шине 12, коллектор первого промежуто ного транзистора 8 через четвертый резистор 13 соединен с шиной 5 питания, аноды первого и второго диодов 14 и 15 соединены соответственно с коллекторами первого и второго промежуточных транзисторов 8 и 9, ка тоды - с входом неинвертирукицего выходного каскада 16, а коллектор второго промежуточного транзистора 9 через четвертый резистор 17 соединен с шиной 5 питания, при этом инвертирукщий выходной каскад 10 содержит двухэмиттерный транзистор 18, база которого подключена к его входу, первый эмиттер подключен к общей шине 1 2, а второй эмиттер через соответствующий резистор 19 - к шине 5 питания, и соединен с базой выходного транзисто ра 20, коллектор которого через соот ветствующий резистор 21 подключен к шине 5 питания, а эмиттер соединен с коллектором двухэмиттерного транзистора 18 и выходом 22 элемента, при этом неинвертирующий выходной каскад 16 содержит первый транзистор 23, база которого соединена с входом каскада, коллектор которого соединен с шиной 5 питания и коллектором второго выходного транзистора 24, эмиттер которого соединен с дополнительным выходом 25 элемента и эмиттером третьего транзистора 26 обратной проводимости, коллектор которого под ключен к общей шине 12, база - к катоду диода 27 и через резистор 28 к общей шине 12, анод диода 27 соединен с эмиттером первого транзистора 23, база которого соединена с базой второго транзистора 24. Логический элемент работает следу ющим образом. Пусть в исходном состоянии на вхьдах 6 и 7 присутствует высокий потенциал, что соответствует значению логических единиц. В этом случае первый I и второй 2 входные транзисторы находятся в инверсном активном режиме и их базовые токи, величина которых определяется резисторами 3 и 4, обуславливают насыценное состояние промежуточных транзисторов 8 и 9. При этом на эмиттерах промежуточных транзисторов 8 и 9, и входе первого выходного каскада 10 присутствует высокий потенциал. С входа первого выходного каскада 10 в базу двухэмиттерного транзистора 18, имеющего большой инверсный коэффициент передачи, поступает ток насыщенных промежуточных транзисторов 8 и 9. Подключение второго эмиттера к базе выходного транзистора 20 обеспечивает выключение последнего после .отпирания транзистора 18.и его перехода в режим насыщения. При этом на выходе 22 присутствует низкий потенциал, что соответствует состоянию логического нуля, следовательно, выходной каскад инвертирует сигнал, поступающий на его вход. На коллекторах промежуточных транзисторов 8 и § присутствует низ- кий потенциал. Первый 14. и второй 15 введенные диоды закрыты, поскольку на базах низкий потенциал, и на входе выходного каскада 16 - яизкий потенциал, в результате транзисторы 23 и 24 оказываются в состоянии отсечки, база р-п-р транзистора 26 оказьшается соединенной с общей шиной 12 через резистор 28, чем обеспечивается открытое состояние транзистора 26, . что соответствует состоянию логического нуля на выходе 22. Следовательно, выходной каскад 16 повторяет сигнал, поступающий на его вход. Если на входе 6 присутствует высокий потенциал, а на входе 7 низкий, в этом случае первый входной транзистор I находится в инверсном активном режиме и его базовый ток обусловливает насыщенное состояние промежуточного транзистора 8, а второй входной транзистор 2 закрыт, его коллекторе присутствует низкий потенциал, что обусловливает состояние отсечки промежуточного транзистора 9. На эмиттерах промежуточных транзисторов 8 и 9 и входе выходного каскада 10 присутствует высокий потенциал. Выходной каскад 10 ннв.ертнрует сигнал, поступахиций на его вход н HQ

s

выходе 22 присутствует низкий потенЦиал, т.е. логический нуль.

На коллекторах промежуточных транзисторов 8 и 9 присутствует соответствеино низкий и высокий потенциал. Первый введенный диод 14 закрыт, поскольку на его аноде низкий потенциал, а второй введенный диод 15 открыт и на входе выходного каскада 16 - высокий потенциал, так в него поступает ток от шины 5 питания через резистор 17 и второй введенный диод 15. Выходной каскад 16 повторяет сигнал, поступающий на его вход, и на выходе 25 присутствует высокий потенциал, т.е. логическая единица.

Если на входе 6 присутствует низкий потенциал, то на входе 7 - высокий. В этом случае первый входной транзистор I закрыт, на его коллекторе присутствует низкий потенциал, что обусловливает состояние отсечки промежуточного транзистора 8, а второй входной транзистор находится в инверсном, активном режиме и его базовый ток обусловливает насыщенное .состояние промежуточного транзистора 9.

На эмиттерах промежуточных транзисторов 8 и 9 и входе выходного каскада 10 присутствует высокий потенциал. Выходной каскад 10 инвертирует сигнал, поступающий на его вход и на выходе 22 присутствует низкий потенциал, т.е. логический нуль.

На коллекторах промежуточных транзисторов 8 и 9 присутствует соответственно высокий и низкий потенциал. Первый введенный диод 1А открыт, а второй введенный диод I5 закрыт и на входе выходного каскада 16 высокий потенциал, так в него поступает ток от шины 5 питания через резистор 13 и первый введенный диод 14. Выходной каскад 16 повторяет сигнал, поступающий на его вход, и на выходе 25 присутствует высокий потенциал, т.е. логическая единица.

Если на входах 6 и 7 присутствует низкий потенциал, то первый 1 и вто89416

рой 2 входные транзисторы закрыты, на их коллекторах - низкий потенциал, что обусловливает состояние отсечки промежуточных транзисторов 8 и 9. 5 На эмиттерах промежуточных транзисторов 8 и 9 и входе выходного каскада 10 присутствует низкий потенциал. Выходной каскад 10 инвертирует сигнал, поступающий на его вход, и на выходе 22 присутствует высокий потенциал, т.е. логическая единица.

На коллекторах промежуточных транзисторов 8 и 9 присутствует высокий потенциал. Первый 14 и второй 15 введенные диоды открыты и на входе выходного каскада 16 высокий потенциал, так как в него поступает ток от шины 5 питания через резистор 13 и первый введенный диод 14, а также

ток от шины 5 питания через резистор 17 и второй введенный диод 15.

каскад 16 повторяет сигнал, поступающий на его вход, и на выходе 25 присутствует высокий

потенциал, т.е. логическая единица. Состояния входов и выходов логического элемента сведены в таблицу.

Выходы

Входы .

25

22

Из таблицы видно, что на выходе 22 реализуется логическая функция И-НЕ, а на входе 25 - логическая функция ИЛИ-НЕ в положительной логике.

Технико-экономический эффект в логическом элементе заключается в расширении его функциональных возможностей, что позволяет уменьшить

номенклатуру логических элементов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент | 1984 |

|

SU1261105A1 |

| Логический элемент | 1988 |

|

SU1529441A1 |

| Логический элемент | 1985 |

|

SU1262717A1 |

| Логический элемент | 1988 |

|

SU1554136A1 |

| Цифровая полупроводниковая интегральная схема с тремя состояниями на выходе | 1980 |

|

SU900454A1 |

| Логический элемент "запрет" | 1976 |

|

SU587627A1 |

| Триггерный логический элемент И/И-НЕ | 2022 |

|

RU2789166C1 |

| Буферное логическое ТТЛ устройство | 1981 |

|

SU993477A1 |

| ТРИГГЕРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ 2И-ИЛИ/2И-ИЛИ-НЕ | 2024 |

|

RU2829649C1 |

| Стабилизированный источник питания | 1981 |

|

SU993228A1 |

1. ЛОГИЧЕСКИЙ ЭЛЕМЕНТ,-содержащий первый и второй входные транзисторы, базы которых через первый и второй резисторы подключены к шине питания, эмиттеры подключены к первому и второму входам элемента, а коллекторы соединены с базами соответственно первого и второго -промежуточных транзисторов,эмиттеры которых подключены к входу инвертирующего .каскада и через третий резистор - к общей шине, коллектор первого промежуточного транзистора через, четвертый резистор соединен с шиной питания, отличающийся тем, что, с целью расширения функциональных возможностей, в него введе-ны неинвертирующий выходной каскад, два диода и резистор, аноды первого и второго диодов соединены соответственно с коллекторами первого и вто-рого промежуточных транзисторов, катоды - с входом неинвертирующего выходного каскада, а коллектор второго промежуточного транзистора через четвертый резистор соединен с шиной питания. 2. Элемент по п. 1, о т л и ч а ющ и и с я тем, что инвертирующий выходной каскад содержит двухэмиттерный транзистор, база которого подключена к его входу, первый эмиттер подключен к общей шине, а второй эмиттер .через соответствующий резистор - к шине питания и соединен с базой выходного транзистора, коллектор которого через соответствующий резистор подключен к щине питания,3 а эмиттер соединен с коллектором (Л двухэмиттерного транзистора и выходом элемента. 3. Элемент по п. 1,отличающ и и с я тем, что неинвертирующий выходной каскад содержит первый транзистор, база которого соединена с входом каскада, коллектор - с шиной 00 питания и коллектором второго тран00 зистора, эмиттер которого соединен с со дополнительным выходом элемента и 4 эмиттером третьего транзистора обратной проводимости, коллектор которого подключен к общей шине, база - к катоду диода и через резистор - к общей шине, анод диода соединен с эмиттером первого транзистора, база которого соединена с базой второго транзистора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Логический элемент и-не | 1978 |

|

SU729848A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Букреев И | |||

| Н | |||

| и др | |||

| Микроэлектронные схемы цифровых устройств | |||

| М., Советское радио, 1975, с | |||

| Солесос | 1922 |

|

SU29A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-02-07—Публикация

1983-10-24—Подача