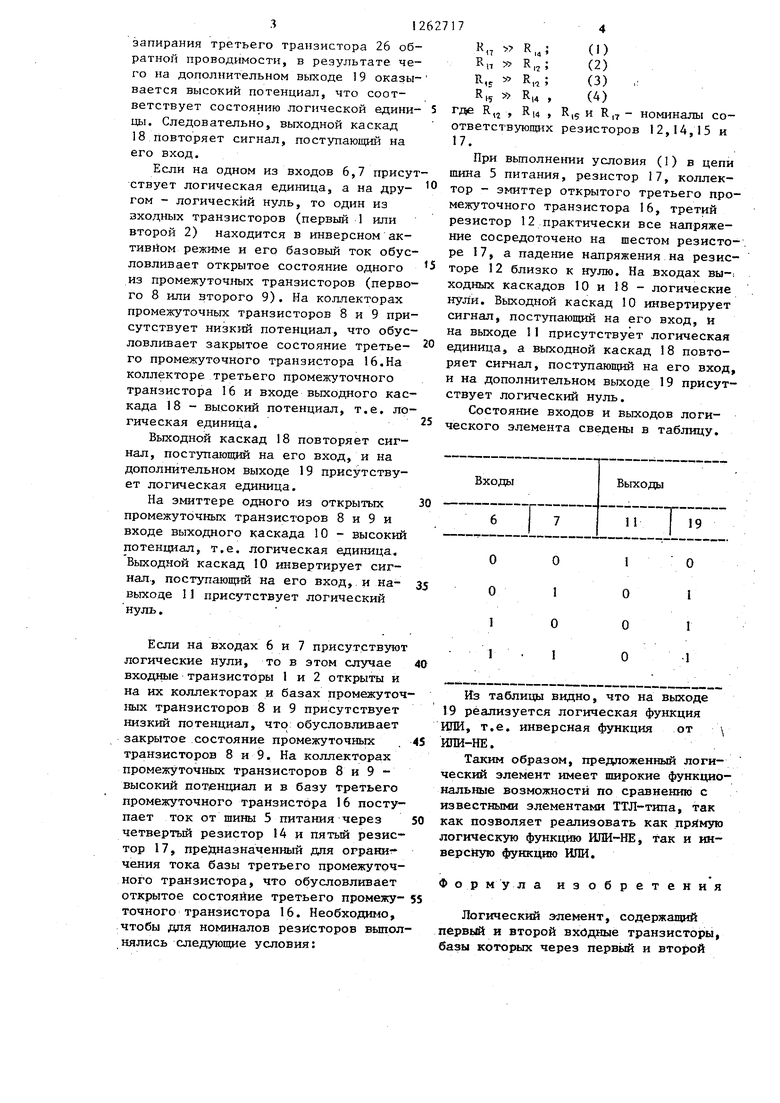

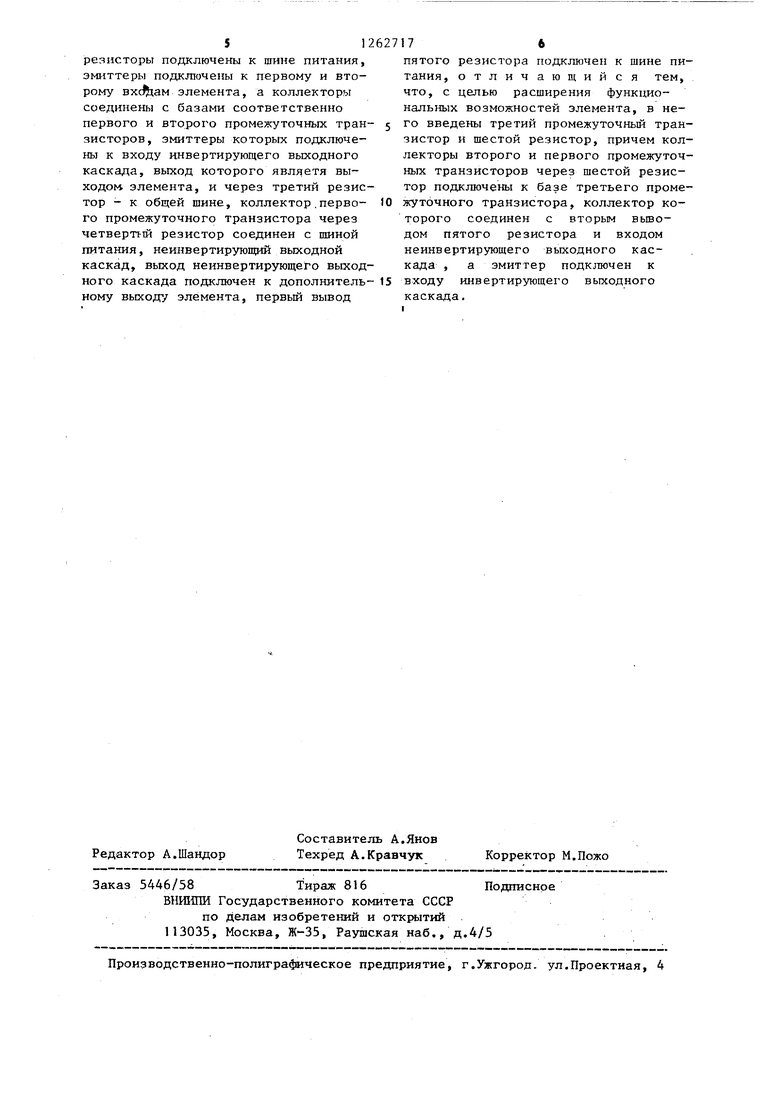

Изобретение относится к импульсной технике и предназначено для пост роения цифровых логических устройств Цель изобретения - расширегше функциональных возможностей логического элемента. На чертеже представлена принципиальная электрическая схема логическо го элегмента. 1 . Логический элемент содержит первый и второй входные транзисторы и 2, базы которых через первый и вто рой резисторы 3 и 4 подключены к шине 5 питания, эмиттеры подключены к первому и второму входам 6 и 7 элемента, а коллекторы соединены с база ми соответственно первого и второго промежуточных транзисторов 8 м 9, эмиттеры которых подключены к входу инвертирующего выходного каскада 10, выход которого является выходом 11 элемента, и через третий резистор 12 подключены к общей шине 13, коллекто ры первого и второго промежуточных транзисторов через четвертый резистор 14 подключены к шине 5 питания,а через шестой резистор 15 соединены с базой третьего промежуточного транзистора 16, коллектор которого через пятый резистор 17 подключен к шине 5 питания и соединен с входом неинвертирующего выходного каскада 18, выход которого является дополнительным выходом 19 элемента, а эмиттер подключен к входу инвертирующего выходного каскада 10, при этом инвертирутопщй каскад 10 содержит двухэмиттерный транзистор 20,база которого соединена с его аходом, первый эмиттер подключен к общей шине 13 а второй эмиттер через соответствующий резистор 21 подключен к шине 5 литания и соединен с базой выходного транзистора 22, коллектор которого через, соответствующий резне .тор 23. подключен к шине 5 питания, а эмиттер соединен с коллектором двухэмиттерного транзистора 20 и выходом 11 элемента, при этом неинвертирующий выходной каскад 18 содержит первый транзистор 24, база которого соединена с входом каскада, коллектор соединен с шиной 5 питания и кол лектором второго выходного транзистора 25, эмиттер которого соединен с дополнительным выходом 19 элемента и эмиттером третьего транзистора 26 обратной проводимости, коллектор ко172торого подключен к общей ишне 13, база - к катоду диода 27 и через резистор 28 - к общей шине 13, анод диода 27 соединен с эмиттером первого транзистора 24, база которогхэ соединена с базой второго выходного транзситора 25. Логический элемент работает следующим образом. Пусть в исходном состоянии на входах 6 и 7 присутствует высокий потенциал, что соответствует значению логических единиц. В этом случае первый и второй входные транзисторы 1 и 2 находятся в инверсном активном режиме и их базовые токи, величина которых определяется резисторами 3 и 4, обуславливают открытое состояние промежуточных транзисторов 8 и 9. При этом на эмиттерах промежуточных транзисторов 8 и 9 и входе инвертирующего выходного каскада 10 присутствует высокий потенциал, т.е. логическая единица. С входа инвертирующего выходного каскада 10 в базу двухэмиттерного транзистора 20, имеющего большой инверсный коэффициент переда-, чи, поступает эмиттерный ток открытых промежуточных транзисторов 8 и 9.Подключение второго эмиттера к базе выходного транзистора 22 обеспечивает выключение последнего после отпирания транзистора 20 и его перехода в режим наcьш eния. При этом на выходе 5 присутствует низкий потенциал,что соответствует состоянию логического нуля. Следовательно, выходной каскад 10 инвертирует сигнал, поступающий на его вход. На коллекторах промежуточных транзисторов В и 9 присутствует низкий потенциал, что обусловливает закрытое состояние третьего промежуточного транзистора 16, так как в его базу поступает ток с коллекторов промежуточных транзисторов через пятый резистор 15, На коллектор1е третьего промежуточного транзистора 16 - высокий потенциал и в базы первого транзистора 24и второго выходного транзистора 25поступает ток от шины 5 питания через резистор 17, что обуславливает открытое состояние первого транзисто- ра 24 и второго выходного транзистора 25, Эмиттерный ток первого транзистора 24 создает на резисторе 28 падение напряжения, достаточное для 31 запирания третьего транзистора 26 об ратной проводимости, в результате че го на дополнительном выходе 19 оказы вается высокий потенциал, что соответствует состоянию логической едини цы. Следовательно, выходной каскад 18 повторяет сигнал, поступающий на его вход. Если на одном из входов 6,7 прису ствует логическая единица, а на дру гом - логический нуль, то один из входных транзисторов (первый 1 или второй 2) находится в инверсном активйом режиме и его базовый ток обус ловливает открытое состояние одного из промежуточных транзисторов (перво го 8 или второго 9). На коллекторах промежуточных транзисторов 8 и 9 при сутствует низкий потенциал, что обус ловливает закрытое состояние третье го промежуточного транзистора 16,На коллекторе третьего промежуточного транзистора 16 и входе выходного кас када 18 - высокий потенциал, т.е. ло гическая единица. Выходной каскад 18 повторяет сигнал, поступающий на его вход, и на дополнительном выходе 19 присутствует логическая единица. На эмиттере одного из открытых промежуточных транзисторов 8 и 9 и входе выходного каскада 10 - высокий потенциал, т.е. логическая единица. Выходной каскад 0 инвертирует сигнал., поступающий на его вход, и навькоце I1 присутствует логический нуль. Если на входах 6 и 7 присутствуют логические нули, то в этом случае входные транзисторы 1 и 2 открыты и на их коллекторах и базах промежуточ ных транзисторов 8 и 9 присутствует низкий потенциал, что обусловливает закрытое состояние промежуточных . транзисторов 8 и 9. На коллекторах промежуточных транзисторов 8 и 9 высокий потенциал и в базу третьего промежуточного транзистора 16 поступает ток от шины 5 питания через четвертый резистор 14 и пятый резистор 17, предназначенный для огранигчения тока базы третьего промежуточного транзистора, что обусловливает открытое состояйие третьего прамежуточного транзистора 16. Необходимо, чтобы для номиналов резисторов выпол нялись следующие условия: 174 к,т (I) R,,;(2) R,,;(3) ,: .. R,4 ,(4) где R,j , R|4 15 и R|7 - номиналы соответствующих резисторов 12,14,15 и 17. При вьтолнении условия (1) в цепи шина 5 питания, резистор 17, коллектор - эмиттер открытого третьего промежуточного транзистора 16, третий резистор 12 практически все напряжение сосредоточено на шестом резисторе 17, а падение напряжения на резисторе 12 близко к нулю. На входах вы-: ходных каскадов 10 и 18 - логические нули. Выходной каскад 10 инвертирует сигнал, поступающий на его вход, И на выходе 11 присутствует логическая единица, а выходной каскад 18 повторяет сктнал, поступающий на его вход, и на дополнительном выходе 19 присутствует логический нуль. Состояние входов и выходов логического элемента сведены в таблицу. О О 01 1О Из таблицы видно, что на выходе 19 реализуется логическая функция ИЛИ, т.е. инверсная функция от ИПИ-НЕ. Таким образом, предложенный логический элемент имеет широкие функциональные возможности по сравнению с известными элементами ТТЛ-типа, так как позволяет реализовать как прямую логическую функцшо ИЛИ-НЕ, Так и инверсную функцию ИЛИ. Формула изобретения Логический элемеит, содержащий первый и второй входные транзисторы, базы которых через первый и второй

5 2627176

резисторы подключены к шине питания,пятого резистора подключен к шине пиэмиттеры подключены к первому и вто-тания, отличающийся тем, рому элемента, а коллекторычто, с целью расширения функциосоединены с базами соответственнональных возможностей элемента, в непервого и второго промежуточных тран- введены третий промежуточный транзисторов, эмиттеры которых подключе-зистор и шестой резистор, причем колны к входу инвертирующего выходноголекторы второго и первого промежуточкаскада, выход которого являетя вы-ных транзисторов через шестой резисходом элемента, и через третий резис-тор подключены к базе третьего прометор - к общей шине, коллектор.перво- 10жуточного транзистора, коллектор кого промежуточного транзистора черезторого соединен с вторым вьшочетвертий резистор соединен с шинойдом пятого резистора и входом питания, неинвертирующий выходнойнеинвертирующего выходного каскаскад, выход неинвертирующего выход-када , а эмиттер подключен к ного каскада подключен к дополнитель- 15входу инвертирующего выходного ному выходу элемента, первый выводкаскада.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент | 1983 |

|

SU1138941A1 |

| Логический элемент | 1984 |

|

SU1261105A1 |

| Логический элемент | 1988 |

|

SU1529441A1 |

| Логический элемент | 1988 |

|

SU1554136A1 |

| Логический элемент "запрет" | 1976 |

|

SU587627A1 |

| Цифровая полупроводниковая интегральная схема с тремя состояниями на выходе | 1980 |

|

SU900454A1 |

| Д-триггер | 1988 |

|

SU1562962A1 |

| Буферное логическое ТТЛ устройство | 1981 |

|

SU993477A1 |

| Устройство согласования | 1983 |

|

SU1138942A1 |

| Триггерный логический элемент И/И-НЕ | 2022 |

|

RU2789166C1 |

Изобретение относится к области импульсной техники и может быть использовано для построения цифровых .логических устройств. Целью изобретения является расширение функциональных возможностей логического злемента. Для достижения этой цели в логи-. ческий элемент введены резистор 15 и третий промежуточный транзистор 16, к базе которого подключен дополнительно введенный резистор .Состояния входов и выходов логического элемента сведены в таблицу , приведенную в описании из об-ретенйя.Предпоженный логический злемент по сравнению с известными злементами типа транзисторно-транзисторной логики.позволяет реализовать как прямую логическую функцию ИЛИ-НЕ, так Щ и инверсную ИЛИ, что расширяет его функциональные возможности, 1 ил, ГЛ 1 табл.

| Букреев И.Н, и др | |||

| Микроэлектронные схемы цифровых устройств | |||

| М.: Советское радио, 1975, с.29, рис,1.20, Авторское свидетельство СССР № 1138941, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-10-07—Публикация

1985-02-28—Подача